What Is Page Coloring

Cache coloring In computer science, cache coloring (also known as page coloring) is the process of attempting to allocate free pages that are contiguous from the CPU cache 's point of view, in order to maximize the total number of pages by the processor. Cache coloring suffers from a number of difficulties that, while not insurmountable, make it difficult and risky for RTOS vendors to implement. For one, cache coloring is specific to the cache structure of your CPU.

The cache size and number of ways vary depending on the model of your Intel, Arm, or PowerPC CPU. Using page coloring to reduce conflicts (for caches with simple modulo a power of two indexing) is less unpopular because the page coloring is not required for correctness. If a particular color becomes scarce, a page can be mis.

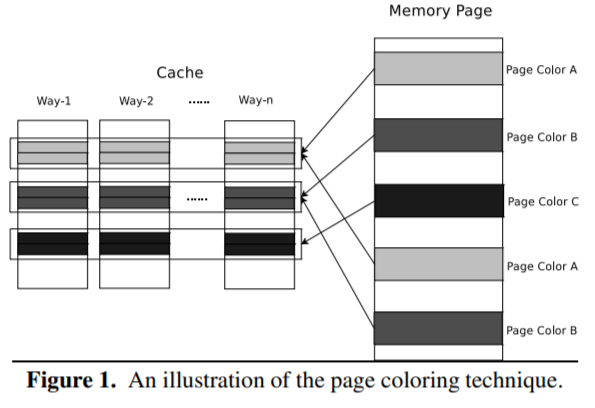

Discover the intricacies of page coloring in computer architecture and learn how to optimize memory performance for enhanced system efficiency. In page coloring, an entire virtual memory page is given a color, which generally forms a set of cache sets that have the same color, but the idea is the same. I have a pretty good image of this saved somewhere.

Because the memory clusters are called pages, the term page coloring is used synonymously with cache coloring. The Sense behind Cache Coloring The whole purpose behind cache coloring is to achieve better deterministic behavior of applications through the exact knowledge and definition of the physically available memory area. Coloring All these details, let's try to understand the ideas behind page coloring.

Some places, like the paper [1] and ARM documentation, refer to it as cache coloring. This multiple definitions stem from the fact that coloring is a software mechanism that is tightly coupled with hardware, i.e. cache, features.

![50 Fascinating Fairy Coloring Pages [Free Printable] - Our Mindful Life 50 Fascinating Fairy Coloring Pages [Free Printable] - Our Mindful Life](https://www.ourmindfullife.com/wp-content/uploads/2023/03/Wicked-bat-fairy-coloring-page-for-adults-full-size.jpg)

Basic idea. Constraining the mapping of virtual to physical addresses (page coloring) can speed and/or simplify caches in the presence of virtual memory. For the mapping to hold, physical memory must be partitioned into distinct colors, and virtual pages allocated to a specific color of physical page determined by the mapping.

This paper uses and analytical model and simulation to compare the paging. Similarly, page coloring techniques have not proven efficient at adapting the cache partition sizes for threads with varying memory demands. This paper presents a memory management framework called COLORIS, which provides support for both static and dynamic cache partitioning using page coloring.

Discover coloring pages history from 1880s Victorian roots to AI.