Clock Generator Vhdl Code . Ide for the e languagedvt eclipse ide edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. At the same time, they will output the results from the last. we can use this approach to continually schedule changes to the signal state. all clocked processes are triggered simultaneously and will read their inputs at once. Process begin clk <= '0'; in many test benches i see the following pattern for clock generation: This example shows how to generate a clock, and give inputs and. This is useful for generating clocks,. you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. how to use a clock and do assertions.

from www.chegg.com

This is useful for generating clocks,. This example shows how to generate a clock, and give inputs and. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. we can use this approach to continually schedule changes to the signal state. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. Process begin clk <= '0'; in many test benches i see the following pattern for clock generation: Ide for the e languagedvt eclipse ide At the same time, they will output the results from the last. all clocked processes are triggered simultaneously and will read their inputs at once.

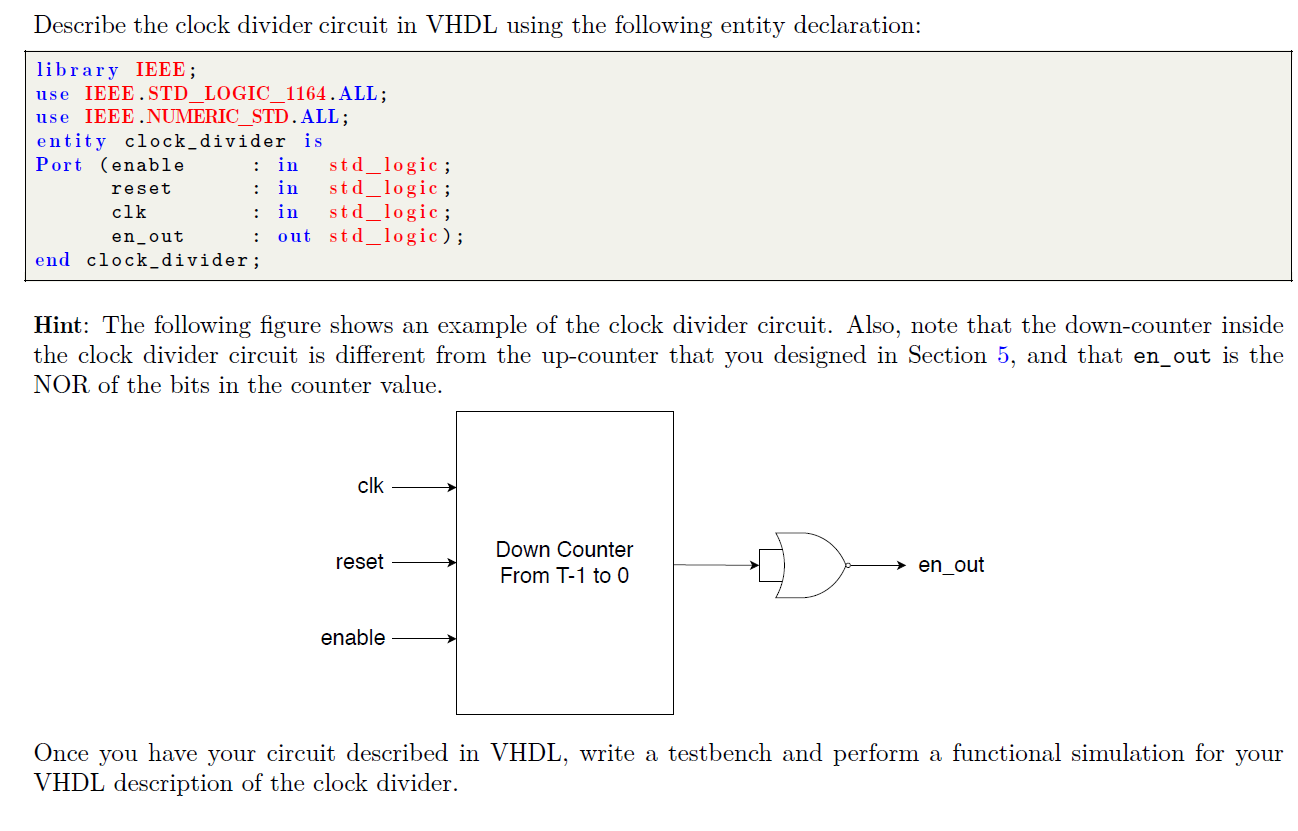

Describe the clock divider circuit in VHDL using the

Clock Generator Vhdl Code all clocked processes are triggered simultaneously and will read their inputs at once. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. Process begin clk <= '0'; Ide for the e languagedvt eclipse ide This is useful for generating clocks,. This example shows how to generate a clock, and give inputs and. we can use this approach to continually schedule changes to the signal state. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. how to use a clock and do assertions. all clocked processes are triggered simultaneously and will read their inputs at once. in many test benches i see the following pattern for clock generation: you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga. At the same time, they will output the results from the last.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Clock Generator Vhdl Code This example shows how to generate a clock, and give inputs and. how to use a clock and do assertions. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. This is useful for generating clocks,. Process begin clk <= '0'; At the same time, they will output the results from the last. . Clock Generator Vhdl Code.

From www.youtube.com

How to make a 1Hz Clock (VHDL) YouTube Clock Generator Vhdl Code At the same time, they will output the results from the last. Ide for the e languagedvt eclipse ide This is useful for generating clocks,. you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga. we can use this approach to. Clock Generator Vhdl Code.

From www.youtube.com

How to create a timer in VHDL YouTube Clock Generator Vhdl Code In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. how to use a clock and do assertions. This is useful for generating clocks,. we can use this approach to continually schedule changes to the signal state. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your. Clock Generator Vhdl Code.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Generator Vhdl Code all clocked processes are triggered simultaneously and will read their inputs at once. in many test benches i see the following pattern for clock generation: This example shows how to generate a clock, and give inputs and. we can use this approach to continually schedule changes to the signal state. how to use a clock and. Clock Generator Vhdl Code.

From www.engineersgarage.com

VHDL Tutorial 12 Designing an 8bit parity generator and checker Clock Generator Vhdl Code we can use this approach to continually schedule changes to the signal state. Ide for the e languagedvt eclipse ide This is useful for generating clocks,. in many test benches i see the following pattern for clock generation: At the same time, they will output the results from the last. This example shows how to generate a clock,. Clock Generator Vhdl Code.

From copyprogramming.com

How do we set time in vhdl simulation for an fpga kit having clock of Clock Generator Vhdl Code In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. in many test benches i see the following pattern for clock generation: all clocked processes are triggered simultaneously and will read their inputs at once. how to use a clock and do assertions. This is useful for generating clocks,.. Clock Generator Vhdl Code.

From www.engineersgarage.com

Design 3×8 decoder and 8×3 encoder using VHDL Clock Generator Vhdl Code we can use this approach to continually schedule changes to the signal state. Ide for the e languagedvt eclipse ide In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. in many test benches i see the following pattern for clock generation: how to use a clock and do. Clock Generator Vhdl Code.

From www.engineersgarage.com

VHDL Tutorial 14 Design 1×8 demultiplexer and 8×1 multiplexer using VHDL Clock Generator Vhdl Code edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. This is useful for generating clocks,. you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga. we can use this approach to continually schedule changes to. Clock Generator Vhdl Code.

From www.jjmk.dk

VHDL implementaions Clock Generator Vhdl Code Process begin clk <= '0'; This is useful for generating clocks,. At the same time, they will output the results from the last. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. all clocked processes are triggered simultaneously and will read their inputs at once. you can use the. Clock Generator Vhdl Code.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL Clock Generator Vhdl Code edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. At the same time, they will output the results from the last. in many test benches i see the following pattern for clock generation: we can use this approach to continually schedule changes to the signal state. all clocked processes are triggered. Clock Generator Vhdl Code.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL Clock Generator Vhdl Code edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. in many test benches i see the following pattern for clock generation: how to use a clock and do assertions. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. This example shows how to. Clock Generator Vhdl Code.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Clock Generator Vhdl Code edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. all clocked processes are triggered simultaneously and will read their inputs at once. At the same time, they will output the results from the last. . Clock Generator Vhdl Code.

From jjmk.dk

5.2 Multiple Clock Clock Generator Vhdl Code edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. This is useful for generating clocks,. you can use the code above for your vhdl clock design if you need a clock divider by an integer. Clock Generator Vhdl Code.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Generator Vhdl Code we can use this approach to continually schedule changes to the signal state. This is useful for generating clocks,. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. Ide for the e languagedvt eclipse ide Process begin clk <= '0'; This example shows how to generate a clock, and give. Clock Generator Vhdl Code.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Generator Vhdl Code we can use this approach to continually schedule changes to the signal state. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga.. Clock Generator Vhdl Code.

From www.youtube.com

Digital and Analog Clocks using VHDL and FPGA YouTube Clock Generator Vhdl Code you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga. This example shows how to generate a clock, and give inputs and. in many test benches i see the following pattern for clock generation: we can use this approach to. Clock Generator Vhdl Code.

From enginemanualkortig.z19.web.core.windows.net

Schematic To Vhdl Code Generator Clock Generator Vhdl Code in many test benches i see the following pattern for clock generation: we can use this approach to continually schedule changes to the signal state. At the same time, they will output the results from the last. you can use the code above for your vhdl clock design if you need a clock divider by an integer. Clock Generator Vhdl Code.

From www.youtube.com

FPGA LED blink VHDL FPGA learn by Examples Ep02 VHDL clock divider Clock Generator Vhdl Code in many test benches i see the following pattern for clock generation: we can use this approach to continually schedule changes to the signal state. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. you can use the code above for your vhdl clock design if you need. Clock Generator Vhdl Code.

From embdev.net

vhdl input clock to output Clock Generator Vhdl Code Process begin clk <= '0'; This is useful for generating clocks,. Ide for the e languagedvt eclipse ide we can use this approach to continually schedule changes to the signal state. you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga.. Clock Generator Vhdl Code.

From www.youtube.com

Mod04 Lec22 VHDL Examples, FSM Clock YouTube Clock Generator Vhdl Code This is useful for generating clocks,. how to use a clock and do assertions. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. At the same time, they will output the results from the last. in many test benches i see the following pattern for clock generation: edit,. Clock Generator Vhdl Code.

From www.chegg.com

Wright a VHDL code Design a dual clock synchronous Clock Generator Vhdl Code how to use a clock and do assertions. Ide for the e languagedvt eclipse ide At the same time, they will output the results from the last. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within. Clock Generator Vhdl Code.

From copyprogramming.com

How do we set time in vhdl simulation for an fpga kit having clock of Clock Generator Vhdl Code all clocked processes are triggered simultaneously and will read their inputs at once. you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga. how to use a clock and do assertions. At the same time, they will output the results. Clock Generator Vhdl Code.

From stackoverflow.com

Generating 2 clock pulses in VHDL Stack Overflow Clock Generator Vhdl Code In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. This is useful for generating clocks,. you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga. how to use a clock and do. Clock Generator Vhdl Code.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Clock Generator Vhdl Code This is useful for generating clocks,. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. we can use this approach to continually schedule changes to the signal state. all clocked processes are triggered simultaneously and will read their inputs at once. in many test benches i see the following pattern for. Clock Generator Vhdl Code.

From www.youtube.com

How to generate clock in Verilog HDL YouTube Clock Generator Vhdl Code Process begin clk <= '0'; edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. how to use a clock and do assertions. in many test benches i see the following pattern for clock generation: This example shows how to generate a clock, and give inputs and. we can use this approach. Clock Generator Vhdl Code.

From www.embeddedrelated.com

VHDL tutorial combining clocked and sequential logic Gene Breniman Clock Generator Vhdl Code Ide for the e languagedvt eclipse ide This is useful for generating clocks,. Process begin clk <= '0'; all clocked processes are triggered simultaneously and will read their inputs at once. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. how to use a clock and do assertions. . Clock Generator Vhdl Code.

From www.youtube.com

VHDL Code for Fibonacci Series Generator VHDL Digital Electronics Clock Generator Vhdl Code In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. all clocked processes are triggered simultaneously and will read their inputs at once. This example shows how to generate a clock, and give inputs and. in many test benches i see the following pattern for clock generation: edit, save,. Clock Generator Vhdl Code.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Clock Generator Vhdl Code edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. At the same time, they will output the results from the last. in many test benches i see the following pattern for clock generation: how to use a clock and do assertions. In almost any testbench, a clock signal is usually required in. Clock Generator Vhdl Code.

From programmer.ink

Design of digital electronic clock based on VHDL language Clock Generator Vhdl Code At the same time, they will output the results from the last. This is useful for generating clocks,. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. all clocked processes are triggered simultaneously and will read their inputs at once. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other. Clock Generator Vhdl Code.

From www.chegg.com

Describe the clock divider circuit in VHDL using the Clock Generator Vhdl Code In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. Process begin clk <= '0'; all clocked processes are triggered simultaneously and will read their inputs at once. At the same time, they will output the results from the last. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls. Clock Generator Vhdl Code.

From www.youtube.com

How to create a Clocked Process in VHDL YouTube Clock Generator Vhdl Code in many test benches i see the following pattern for clock generation: edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. you can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the fpga. how to use. Clock Generator Vhdl Code.

From stackoverflow.com

vhdl Clock recovery for differential manchester code on an FPGA Clock Generator Vhdl Code Process begin clk <= '0'; in many test benches i see the following pattern for clock generation: In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. Ide for the e languagedvt eclipse ide all clocked processes are triggered simultaneously and will read their inputs at once. how to. Clock Generator Vhdl Code.

From github.com

GitHub twinjie/VHDLAlarmClock Alarm clock created on the Nexys 4 Clock Generator Vhdl Code This example shows how to generate a clock, and give inputs and. all clocked processes are triggered simultaneously and will read their inputs at once. how to use a clock and do assertions. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. At the same time, they will output the results from. Clock Generator Vhdl Code.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Clock Generator Vhdl Code Process begin clk <= '0'; we can use this approach to continually schedule changes to the signal state. Ide for the e languagedvt eclipse ide This example shows how to generate a clock, and give inputs and. edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. At the same time, they will output. Clock Generator Vhdl Code.

From www.scribd.com

VHDL Code For Clock Divider (Frequency Divider) PDF Vhdl Field Clock Generator Vhdl Code This example shows how to generate a clock, and give inputs and. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the. we can use this approach to continually schedule changes to the signal state. Process begin clk <= '0'; you can use the code above for your vhdl clock. Clock Generator Vhdl Code.