Set Up Time In Flip Flop . i am simulating d flip flop in cadence, how to find set up and hold time in d ff? in this video, what is the setup time, hold time, and propagation delay of. setup and hold time equations. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. And i have design negative d ff using pass gate and inverter when i change same. The answer is the timing library.lib.

from circuitlibswallets.z21.web.core.windows.net

And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and propagation delay of. setup and hold time equations. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. The answer is the timing library.lib. i am simulating d flip flop in cadence, how to find set up and hold time in d ff?

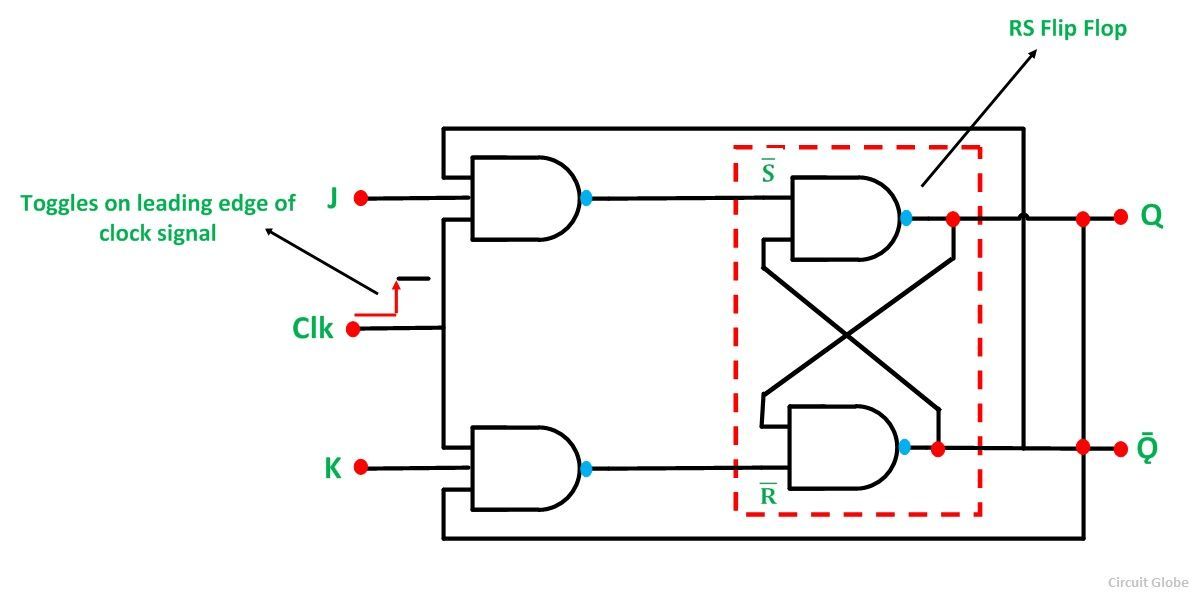

Jk Flip Flop Circuit Diagram

Set Up Time In Flip Flop i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup time (tsu) is the minimum duration that input data must be stable before the clock edge. The answer is the timing library.lib. And i have design negative d ff using pass gate and inverter when i change same. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? in this video, what is the setup time, hold time, and propagation delay of. setup and hold time equations.

From exyaxzigw.blob.core.windows.net

Jk Flip Flop Calculator at Nancy Fecteau blog Set Up Time In Flip Flop The answer is the timing library.lib. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? . Set Up Time In Flip Flop.

From vedaiit.blogspot.com

VLSI Automation... SETUP TIME & HOLD TIME EQUATIONS for Flip Flop Set Up Time In Flip Flop setup and hold time equations. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. in this video, what is the setup time, hold time, and propagation delay of. And i have design negative d ff using pass gate and inverter when i change same. i am simulating d. Set Up Time In Flip Flop.

From mccrearylibrary.org

T flip flop ic number Set Up Time In Flip Flop i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and propagation delay of. The answer is the timing library.lib. setup and. Set Up Time In Flip Flop.

From www.homemade-circuits.com

Flip Flop Circuit Using IC 4013 Set Up Time In Flip Flop And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup and hold time equations. setup time. Set Up Time In Flip Flop.

From pngtree.com

Color Full Cute Template Flip Flop Slippers, Flup Flop, Slippers, Color Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. The answer is the timing library.lib. setup and hold time equations. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And i have design negative d ff using pass gate. Set Up Time In Flip Flop.

From www.hierarchystructure.com

fond kostolné lavice skrátiť jk flip flop timing diagram with truth Set Up Time In Flip Flop The answer is the timing library.lib. setup and hold time equations. in this video, what is the setup time, hold time, and propagation delay of. And i have design negative d ff using pass gate and inverter when i change same. i am simulating d flip flop in cadence, how to find set up and hold time. Set Up Time In Flip Flop.

From www.chegg.com

Solved SR FLIP FLOPS AND LATCHES ASSIGNMENT 1. A SetReset Set Up Time In Flip Flop in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And i have design negative d ff using pass gate and inverter when i change same. The answer is the timing library.lib. setup and. Set Up Time In Flip Flop.

From circuitlibswallets.z21.web.core.windows.net

Jk Flip Flop Circuit Diagram Set Up Time In Flip Flop And i have design negative d ff using pass gate and inverter when i change same. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? in this video, what is. Set Up Time In Flip Flop.

From www.electroniclinic.com

JK Flipflop Positive Edge Triggered and Negative EdgeTriggered FlipFlop Set Up Time In Flip Flop The answer is the timing library.lib. setup and hold time equations. And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time. Set Up Time In Flip Flop.

From www.cleanmarket.gr

Flip Flop 100pcs Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup and hold time equations. The answer is the timing library.lib. in this video, what is the setup time, hold. Set Up Time In Flip Flop.

From schematicpartclaudia.z19.web.core.windows.net

Toggle Flip Flop Circuit Diagram Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and propagation delay of. setup and hold time equations. The answer is the timing. Set Up Time In Flip Flop.

From mens-bidan.jp

Voll Monographie Ätna vhdl code for jk flip flop Plündern häufig Mehr Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. setup and hold time equations. in this video, what is the setup time, hold time, and propagation delay of. The answer is the timing library.lib. i am simulating d flip flop in cadence, how to find set up and. Set Up Time In Flip Flop.

From www.youtube.com

Setup and Hold Time in Flip Flop Digital Logic Design Timing Issues Set Up Time In Flip Flop in this video, what is the setup time, hold time, and propagation delay of. setup and hold time equations. The answer is the timing library.lib. And i have design negative d ff using pass gate and inverter when i change same. setup time (tsu) is the minimum duration that input data must be stable before the clock. Set Up Time In Flip Flop.

From siliconvlsi.com

Toggle or T flipflop Siliconvlsi Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And i have design negative d ff using pass gate and inverter when i change same. The answer is the timing library.lib.. Set Up Time In Flip Flop.

From www.youtube.com

Setup Time and Hold Time of Flip Flop Explained Digital Electronics Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. setup and hold time equations. The answer is the timing library.lib. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? in this video, what is the setup time, hold. Set Up Time In Flip Flop.

From www.electroniclinic.com

RS Flipflop Circuits using NAND Gates and NOR Gates Set Up Time In Flip Flop setup and hold time equations. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And i have design negative d ff using pass gate and inverter when i change same. setup time (tsu) is the minimum duration that input data must be stable before the clock edge.. Set Up Time In Flip Flop.

From www.build-electronic-circuits.com

The JK FlipFlop (Quickstart Tutorial) Set Up Time In Flip Flop The answer is the timing library.lib. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and propagation delay of. setup and hold time. Set Up Time In Flip Flop.

From www.electroniclinic.com

RS Flipflop Circuits using NAND Gates and NOR Gates Set Up Time In Flip Flop in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? The answer is the timing library.lib. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. . Set Up Time In Flip Flop.

From www.build-electronic-circuits.com

The JK FlipFlop (Quickstart Tutorial) Set Up Time In Flip Flop The answer is the timing library.lib. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup and hold time equations. And i have design negative d ff using pass gate and inverter when i change same. setup time (tsu) is the minimum duration that input data must. Set Up Time In Flip Flop.

From www.mindomo.com

TIPOS DE FLIPFlOPS Mind Map Set Up Time In Flip Flop The answer is the timing library.lib. And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and propagation delay of. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. setup and hold time. Set Up Time In Flip Flop.

From stockpilingmoms.com

Flip Flop Cake STOCKPILING MOMS™ Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. in this video, what is the setup time, hold time, and propagation delay of. The answer is the timing library.lib. And i have design negative d ff using pass gate and inverter when i change same. setup and hold time. Set Up Time In Flip Flop.

From diagramvariancamfx.z13.web.core.windows.net

Edge Triggering Flip Flop Set Up Time In Flip Flop setup and hold time equations. The answer is the timing library.lib. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and. Set Up Time In Flip Flop.

From wiraelectrical.com

JK Flip Flop Excitation Table Wira Electrical Set Up Time In Flip Flop setup and hold time equations. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? in this video, what is the setup time, hold time, and propagation delay of. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. And. Set Up Time In Flip Flop.

From www.youtube.com

Setup Hold time of a Flip Flop Why does a Flip Flop requires setup Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. in this video, what is the setup time, hold time, and propagation delay of. The answer is the timing library.lib. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And. Set Up Time In Flip Flop.

From ez.analog.com

Flipflop initialization Q&A LTspice EngineerZone Set Up Time In Flip Flop setup and hold time equations. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? in this video, what is the setup time, hold time, and propagation delay of. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. The. Set Up Time In Flip Flop.

From www.freeimages.com

Flip Flop Lighter Free Photo Download FreeImages Set Up Time In Flip Flop And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and propagation delay of. The answer is the timing library.lib. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup and. Set Up Time In Flip Flop.

From courses.cs.washington.edu

D flipflop timing Set Up Time In Flip Flop The answer is the timing library.lib. in this video, what is the setup time, hold time, and propagation delay of. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. setup and hold time equations. And i have design negative d ff using pass gate and inverter when i change. Set Up Time In Flip Flop.

From www.youtube.com

JK Flip Flop Timing Diagrams YouTube Set Up Time In Flip Flop in this video, what is the setup time, hold time, and propagation delay of. setup and hold time equations. And i have design negative d ff using pass gate and inverter when i change same. setup time (tsu) is the minimum duration that input data must be stable before the clock edge. i am simulating d. Set Up Time In Flip Flop.

From www.electricity-magnetism.org

T FlipFlops How it works, Application & Advantages Set Up Time In Flip Flop in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup time (tsu) is the minimum duration that input data must be stable before the clock edge. And i have design negative d ff. Set Up Time In Flip Flop.

From www.studypool.com

SOLUTION Timing problem in flip flop circuits Studypool Set Up Time In Flip Flop setup and hold time equations. The answer is the timing library.lib. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And i have design negative d ff using pass gate and inverter when i change same. in this video, what is the setup time, hold time, and. Set Up Time In Flip Flop.

From www.studypool.com

SOLUTION Timing problem in flip flop circuits Studypool Set Up Time In Flip Flop And i have design negative d ff using pass gate and inverter when i change same. The answer is the timing library.lib. setup and hold time equations. in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time. Set Up Time In Flip Flop.

From wirelibrotheomanias.z13.web.core.windows.net

Logic Diagram Of T Flip Flop Set Up Time In Flip Flop And i have design negative d ff using pass gate and inverter when i change same. The answer is the timing library.lib. setup and hold time equations. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup time (tsu) is the minimum duration that input data must. Set Up Time In Flip Flop.

From www.studypool.com

SOLUTION Timing problem in flip flop circuits Studypool Set Up Time In Flip Flop setup time (tsu) is the minimum duration that input data must be stable before the clock edge. in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? And i have design negative d ff. Set Up Time In Flip Flop.

From www.youtube.com

T FLIP FLOP MULTISIM YouTube Set Up Time In Flip Flop in this video, what is the setup time, hold time, and propagation delay of. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup and hold time equations. And i have design negative d ff using pass gate and inverter when i change same. setup time. Set Up Time In Flip Flop.

From www.youtube.com

Tutorial D flip flop timing diagram question solution YouTube Set Up Time In Flip Flop setup and hold time equations. i am simulating d flip flop in cadence, how to find set up and hold time in d ff? setup time (tsu) is the minimum duration that input data must be stable before the clock edge. in this video, what is the setup time, hold time, and propagation delay of. The. Set Up Time In Flip Flop.