Arm Cpu Cycle Counter . the cycle counter register bits [31:0] contain the count value. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. The counters include cycle counter and event counters. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). the cycle counter register counts the processor clock cycles. You can use it in conjunction with the performance monitor. Each event counter to count specified hardware events. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. when i am using the cycle counter in aarch64, i am not getting cycles properly. I have enabled read of pmccntr_el0 in user. the pmu collects hardware event counts through counters. Each counter to collect hardware events from workloads at various cpu exception levels and states. Static inline uint32_t read_counter(void) {.

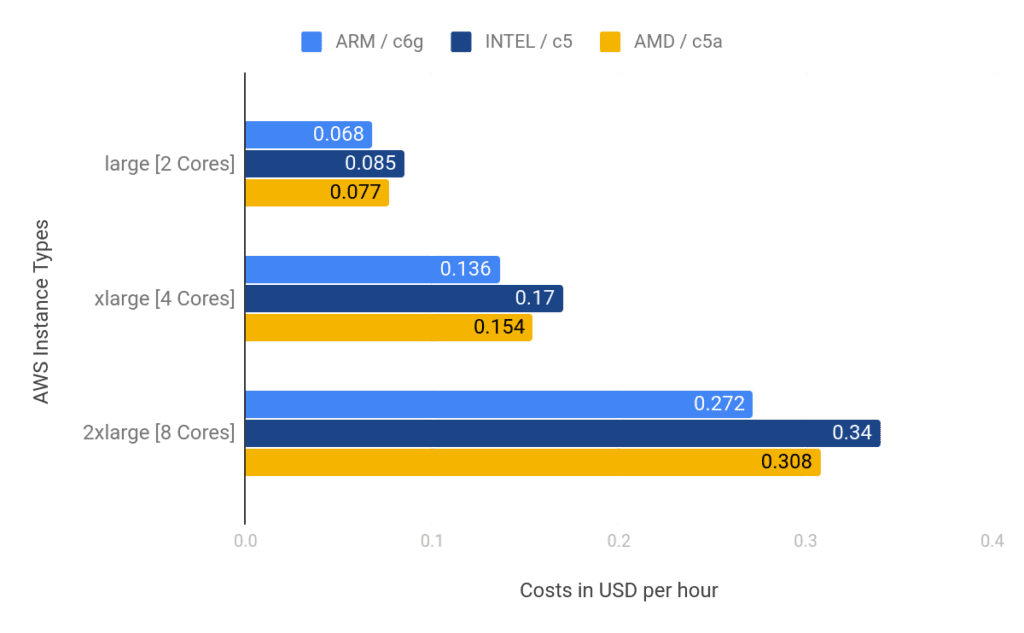

from bitmovin.com

the pmu collects hardware event counts through counters. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. I have enabled read of pmccntr_el0 in user. when i am using the cycle counter in aarch64, i am not getting cycles properly. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). The counters include cycle counter and event counters. You can use it in conjunction with the performance monitor. Each event counter to count specified hardware events. the cycle counter register bits [31:0] contain the count value. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a.

Bitmovin’s Intern Series The Journey from x86 to ARM Testing AMD vs

Arm Cpu Cycle Counter when i am using the cycle counter in aarch64, i am not getting cycles properly. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). the pmu collects hardware event counts through counters. the cycle counter register counts the processor clock cycles. the cycle counter register bits [31:0] contain the count value. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. I have enabled read of pmccntr_el0 in user. when i am using the cycle counter in aarch64, i am not getting cycles properly. Each counter to collect hardware events from workloads at various cpu exception levels and states. Static inline uint32_t read_counter(void) {. The counters include cycle counter and event counters. You can use it in conjunction with the performance monitor. Each event counter to count specified hardware events.

From www.juku.it

More ARM CPUs in the Datacenter for 2017? Juku.it Arm Cpu Cycle Counter the cycle counter register bits [31:0] contain the count value. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). Each event counter to count specified hardware events. The counters include cycle counter and event counters. Each counter to collect hardware events from workloads at various cpu exception levels and states. i'm trying to profile. Arm Cpu Cycle Counter.

From www.researchgate.net

CPU cycles comparison chart implemented on ARM Cortex A15, ARM Cortex Arm Cpu Cycle Counter You can use it in conjunction with the performance monitor. I have enabled read of pmccntr_el0 in user. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. Static inline uint32_t read_counter(void) {. a cycle count indicates the number of processor cycles between the. Arm Cpu Cycle Counter.

From community.arm.com

Arm Fundamentals Intro to understanding Arm processors Architectures Arm Cpu Cycle Counter when i am using the cycle counter in aarch64, i am not getting cycles properly. the cycle counter register bits [31:0] contain the count value. You can use it in conjunction with the performance monitor. the cycle counter register counts the processor clock cycles. Each counter to collect hardware events from workloads at various cpu exception levels. Arm Cpu Cycle Counter.

From www.sumika-sajima.jp

日没 シアー バーマド arm cpu comparison sumikasajima.jp Arm Cpu Cycle Counter I have enabled read of pmccntr_el0 in user. You can use it in conjunction with the performance monitor. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere). Arm Cpu Cycle Counter.

From community.arm.com

Question about the Pipeline, clock cycle and machine cycle in CortexM Arm Cpu Cycle Counter I have enabled read of pmccntr_el0 in user. the pmu collects hardware event counts through counters. Each event counter to count specified hardware events. when i am using the cycle counter in aarch64, i am not getting cycles properly. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being.. Arm Cpu Cycle Counter.

From computersciencewiki.org

The machine instruction cycle Computer Science Wiki Arm Cpu Cycle Counter the pmu collects hardware event counts through counters. Static inline uint32_t read_counter(void) {. the cycle counter register counts the processor clock cycles. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). Each counter to collect hardware events from workloads at various cpu exception levels and states. The counters include cycle counter and event counters.. Arm Cpu Cycle Counter.

From www.microcontrollertips.com

Armbased processors deliver 10x performance on AI and highperformance Arm Cpu Cycle Counter the cycle counter register counts the processor clock cycles. Each event counter to count specified hardware events. You can use it in conjunction with the performance monitor. Each counter to collect hardware events from workloads at various cpu exception levels and states. a cycle count indicates the number of processor cycles between the two most recent instructions committed. Arm Cpu Cycle Counter.

From www.researchgate.net

Execution latency measuring process in a dual issue ARM architecture Arm Cpu Cycle Counter I have enabled read of pmccntr_el0 in user. Static inline uint32_t read_counter(void) {. when i am using the cycle counter in aarch64, i am not getting cycles properly. You can use it in conjunction with the performance monitor. The counters include cycle counter and event counters. the pmu collects hardware event counts through counters. Each event counter to. Arm Cpu Cycle Counter.

From www.intel.com

CPU Cycle Counter Arm Cpu Cycle Counter The counters include cycle counter and event counters. when i am using the cycle counter in aarch64, i am not getting cycles properly. the cycle counter register counts the processor clock cycles. I have enabled read of pmccntr_el0 in user. the pmu collects hardware event counts through counters. i'm trying to profile a c function (which. Arm Cpu Cycle Counter.

From www.cgdirector.com

x86 vs. x64 vs. ARM Differences & Which Is Best [2024 Update] Arm Cpu Cycle Counter Each event counter to count specified hardware events. the pmu collects hardware event counts through counters. You can use it in conjunction with the performance monitor. Each counter to collect hardware events from workloads at various cpu exception levels and states. when i am using the cycle counter in aarch64, i am not getting cycles properly. The counters. Arm Cpu Cycle Counter.

From zhuanlan.zhihu.com

CortexA9之Performance Monitoring Unit(性能监测单元) 知乎 Arm Cpu Cycle Counter the pmu collects hardware event counts through counters. I have enabled read of pmccntr_el0 in user. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). Each counter to collect hardware events from workloads at various cpu exception levels and states. the cycle counter register counts the processor clock cycles. i'm trying to profile. Arm Cpu Cycle Counter.

From www.totalphase.com

What is an ARM Processor? Comparison to x86 and its Advantages and Arm Cpu Cycle Counter I have enabled read of pmccntr_el0 in user. when i am using the cycle counter in aarch64, i am not getting cycles properly. The counters include cycle counter and event counters. the pmu collects hardware event counts through counters. the cycle counter register bits [31:0] contain the count value. i am measuring cycle counts on raspberry. Arm Cpu Cycle Counter.

From www.intel.com

CPU Cycle Counter Arm Cpu Cycle Counter the cycle counter register bits [31:0] contain the count value. Each counter to collect hardware events from workloads at various cpu exception levels and states. Static inline uint32_t read_counter(void) {. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. the pmu collects hardware event counts through counters. The. Arm Cpu Cycle Counter.

From www.manzlab.com

짐켈러, ‘K12 ARM CPU 프로젝트 취소한 AMD 아쉬워’ Arm Cpu Cycle Counter i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). Each counter to collect hardware events from workloads at various cpu exception levels and states. You can use it in conjunction with the performance monitor. the cycle counter register bits [31:0] contain the count value. the cycle counter register counts the processor clock cycles. I. Arm Cpu Cycle Counter.

From cellphones.com.vn

lên kế hoạch tung ra CPU ARM 12 lõi, cạnh tranh với Apple M2 Arm Cpu Cycle Counter The counters include cycle counter and event counters. when i am using the cycle counter in aarch64, i am not getting cycles properly. You can use it in conjunction with the performance monitor. Static inline uint32_t read_counter(void) {. the cycle counter register counts the processor clock cycles. i am measuring cycle counts on raspberry pi 3b+ (arm. Arm Cpu Cycle Counter.

From chipsandcheese.com

Hot Chips 2023 Arm’s Neoverse V2 Chips and Cheese Arm Cpu Cycle Counter I have enabled read of pmccntr_el0 in user. when i am using the cycle counter in aarch64, i am not getting cycles properly. the cycle counter register counts the processor clock cycles. Each event counter to count specified hardware events. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). a cycle count indicates. Arm Cpu Cycle Counter.

From www.anandtech.com

Arm Cortex X4 Fastest Arm Core Ever Built Arm Unveils 2023 Mobile Arm Cpu Cycle Counter Each event counter to count specified hardware events. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. the pmu collects hardware event counts through counters. when i am using the cycle counter in aarch64, i am not getting cycles properly. the cycle counter register bits [31:0] contain. Arm Cpu Cycle Counter.

From github.com

GitHub TeflonAntihaft/ARMv7Logisim ARMv7 SingleCycle processor Arm Cpu Cycle Counter i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). You can use it in conjunction with the performance monitor. when i am using the cycle counter in aarch64, i am not getting cycles properly. the pmu collects hardware event counts through counters. i'm trying to profile a c function (which is called from. Arm Cpu Cycle Counter.

From www.researchgate.net

ARM Cortex CPU in STM32 microcontroller, block diagram [9]. Download Arm Cpu Cycle Counter when i am using the cycle counter in aarch64, i am not getting cycles properly. Each counter to collect hardware events from workloads at various cpu exception levels and states. The counters include cycle counter and event counters. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). a cycle count indicates the number of. Arm Cpu Cycle Counter.

From community.arm.com

Question about the Pipeline, clock cycle and machine cycle in CortexM Arm Cpu Cycle Counter the cycle counter register counts the processor clock cycles. when i am using the cycle counter in aarch64, i am not getting cycles properly. Each event counter to count specified hardware events. You can use it in conjunction with the performance monitor. Each counter to collect hardware events from workloads at various cpu exception levels and states. . Arm Cpu Cycle Counter.

From community.arm.com

First Armv9 Cortex CPUs for Consumer Compute Architectures and Arm Cpu Cycle Counter the cycle counter register counts the processor clock cycles. the cycle counter register bits [31:0] contain the count value. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. I have enabled read of pmccntr_el0 in user. i am measuring cycle counts on raspberry pi 3b+ (arm cortex. Arm Cpu Cycle Counter.

From community.arm.com

Decoding the startup file for Arm CortexM4 Processors blog Arm Cpu Cycle Counter the pmu collects hardware event counts through counters. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. You can use it in conjunction with the performance monitor. Static inline uint32_t read_counter(void) {. The counters include cycle counter and event counters. the cycle counter register counts the processor clock. Arm Cpu Cycle Counter.

From slideplayer.com

Time, Delays, and Deferred Work ppt download Arm Cpu Cycle Counter The counters include cycle counter and event counters. Static inline uint32_t read_counter(void) {. when i am using the cycle counter in aarch64, i am not getting cycles properly. You can use it in conjunction with the performance monitor. the pmu collects hardware event counts through counters. i'm trying to profile a c function (which is called from. Arm Cpu Cycle Counter.

From blog.csdn.net

ARM CPU modes和Exception Level_exception level 和 cpu mode 的关系CSDN博客 Arm Cpu Cycle Counter i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. Static inline uint32_t. Arm Cpu Cycle Counter.

From michaelbambrick.com

Arm Processor Instruction Set Arm Cpu Cycle Counter You can use it in conjunction with the performance monitor. the cycle counter register counts the processor clock cycles. The counters include cycle counter and event counters. the pmu collects hardware event counts through counters. when i am using the cycle counter in aarch64, i am not getting cycles properly. the cycle counter register bits [31:0]. Arm Cpu Cycle Counter.

From www.programmathically.com

How does a CPU Execute Instructions Understanding Instruction Cycles Arm Cpu Cycle Counter i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. The counters include cycle counter and event counters. Each counter to collect hardware events from workloads at various cpu exception levels and states. a cycle count indicates the number of processor cycles between the. Arm Cpu Cycle Counter.

From www.slideserve.com

PPT ARM Processor Architecture (II) PowerPoint Presentation, free Arm Cpu Cycle Counter i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. when i am using the cycle counter in aarch64, i am not getting cycles properly. the pmu collects hardware event counts through counters. I have enabled read of pmccntr_el0 in user. You can. Arm Cpu Cycle Counter.

From www.geeksforgeeks.org

ARM processor and its Features Arm Cpu Cycle Counter The counters include cycle counter and event counters. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. I have enabled read of pmccntr_el0 in user. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being.. Arm Cpu Cycle Counter.

From www.makeuseof.com

ARM vs. Intel Processors What's the Difference? Arm Cpu Cycle Counter a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. Each counter to collect hardware events from workloads at various cpu exception levels and states. Each event counter to count specified hardware events. the pmu collects hardware event counts through counters. The counters include cycle counter and event counters. . Arm Cpu Cycle Counter.

From www.anandtech.com

Cortex A720 Middle Core, Big on Efficiency Arm Unveils 2023 Mobile Arm Cpu Cycle Counter The counters include cycle counter and event counters. You can use it in conjunction with the performance monitor. the pmu collects hardware event counts through counters. Static inline uint32_t read_counter(void) {. Each counter to collect hardware events from workloads at various cpu exception levels and states. I have enabled read of pmccntr_el0 in user. Each event counter to count. Arm Cpu Cycle Counter.

From bitmovin.com

Bitmovin’s Intern Series The Journey from x86 to ARM Testing AMD vs Arm Cpu Cycle Counter i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. Static inline uint32_t read_counter(void) {. the cycle counter register counts the processor clock cycles. i am measuring cycle counts on raspberry pi 3b+ (arm cortex a53). You can use it in conjunction with. Arm Cpu Cycle Counter.

From techrecipe.co.kr

ARM이 발표한 차세대 CPU 시리즈 테크레시피 Arm Cpu Cycle Counter when i am using the cycle counter in aarch64, i am not getting cycles properly. The counters include cycle counter and event counters. the pmu collects hardware event counts through counters. Each counter to collect hardware events from workloads at various cpu exception levels and states. i'm trying to profile a c function (which is called from. Arm Cpu Cycle Counter.

From www.youtube.com

ARM Processors Modes AMR7 LPC2148 Advanced Processors YouTube Arm Cpu Cycle Counter The counters include cycle counter and event counters. the cycle counter register bits [31:0] contain the count value. Each event counter to count specified hardware events. a cycle count indicates the number of processor cycles between the two most recent instructions committed to being. i'm trying to profile a c function (which is called from an interrupt,. Arm Cpu Cycle Counter.

From www.extremeit.com

AppleM18CoreARMCPUvsIntelCorei711700KAMDRyzen75800XCPUs Arm Cpu Cycle Counter the cycle counter register bits [31:0] contain the count value. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. the pmu collects hardware event counts through counters. when i am using the cycle counter in aarch64, i am not getting cycles. Arm Cpu Cycle Counter.

From mspoweruser.com

Arm unveils its PC CPU roadmap, claims it will beat Intel chips in Arm Cpu Cycle Counter The counters include cycle counter and event counters. the cycle counter register bits [31:0] contain the count value. Each event counter to count specified hardware events. Static inline uint32_t read_counter(void) {. i'm trying to profile a c function (which is called from an interrupt, but i can extract it and profile it elsewhere) on a. I have enabled. Arm Cpu Cycle Counter.