Clock Enable Signal . the clkena signals are supported at the clock network level instead of at the pll output counter level. The module has an input. this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. So, when the enable signal is. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). The intel® max® 10 devices support clkena signals at the gclk network level. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. This allows you to gate off. the clkena signals are supported at the clock network level instead of at the pll output counter level. the input signal is taken over when the enable signal is high (level) and the clock rises (edge). to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal.

from bestengineeringprojects.com

the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). the clkena signals are supported at the clock network level instead of at the pll output counter level. this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. So, when the enable signal is. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal. The intel® max® 10 devices support clkena signals at the gclk network level. The module has an input. the input signal is taken over when the enable signal is high (level) and the clock rises (edge). This allows you to gate off. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above.

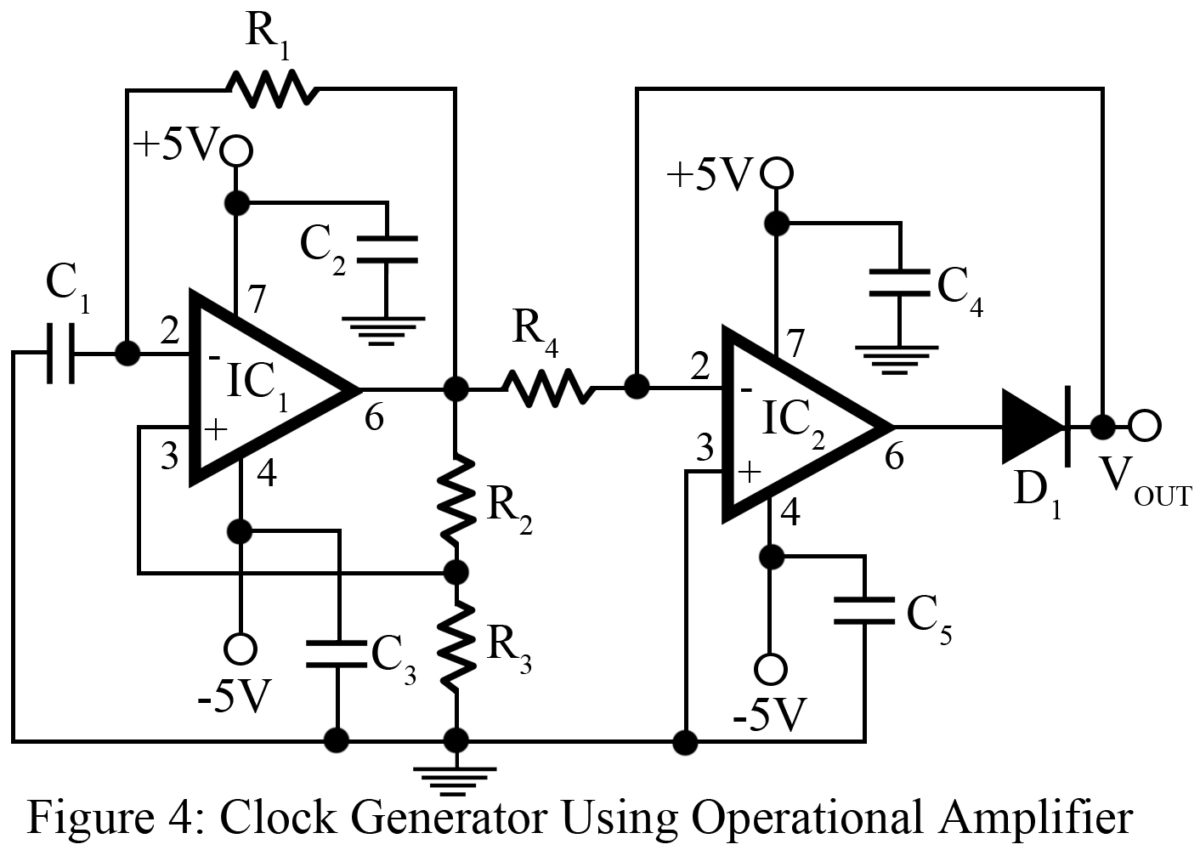

Clock Signal Generator Circuit Best Engineering Projects

Clock Enable Signal the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. the input signal is taken over when the enable signal is high (level) and the clock rises (edge). the clkena signals are supported at the clock network level instead of at the pll output counter level. So, when the enable signal is. The intel® max® 10 devices support clkena signals at the gclk network level. The module has an input. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). This allows you to gate off. this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal. the clkena signals are supported at the clock network level instead of at the pll output counter level.

From es.mathworks.com

Clock, Reset, and Enable Signals MATLAB & Simulink MathWorks España Clock Enable Signal This allows you to gate off. the clkena signals are supported at the clock network level instead of at the pll output counter level. this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. the following verilog clock generator module has three parameters to tweak the. Clock Enable Signal.

From www.youtube.com

Clock signal YouTube Clock Enable Signal the input signal is taken over when the enable signal is high (level) and the clock rises (edge). The module has an input. This allows you to gate off. this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. the clock enable signal, generated by a. Clock Enable Signal.

From www.electroniclinic.com

Types of Clock Discrete Components and Integrated Circuit TTL Clock Clock Enable Signal The intel® max® 10 devices support clkena signals at the gclk network level. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). This allows you to gate off. So, when the enable signal is. the input signal is taken over when the enable. Clock Enable Signal.

From www.youtube.com

5 Ways To Generate Clock Signal In Verilog YouTube Clock Enable Signal The intel® max® 10 devices support clkena signals at the gclk network level. So, when the enable signal is. This allows you to gate off. the clkena signals are supported at the clock network level instead of at the pll output counter level. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to. Clock Enable Signal.

From www.bot-thoughts.com

Bot Thoughts Generating a clock signal with dsPIC33F Clock Enable Signal the clkena signals are supported at the clock network level instead of at the pll output counter level. This allows you to gate off. the input signal is taken over when the enable signal is high (level) and the clock rises (edge). the clkena signals are supported at the clock network level instead of at the pll. Clock Enable Signal.

From www.researchgate.net

Ideal signals for synthesizing the clock signal with triple basal Clock Enable Signal The intel® max® 10 devices support clkena signals at the gclk network level. the clkena signals are supported at the clock network level instead of at the pll output counter level. this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. This allows you to gate off.. Clock Enable Signal.

From www.vrogue.co

Timing Diagram Of Input Signals Using Scan N 3 Downlo vrogue.co Clock Enable Signal this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). So, when the enable signal is. The module has an input. the. Clock Enable Signal.

From www.numerade.com

SOLVED Verilog Code Required to Blink LED at a Different Frequency (1/ Clock Enable Signal This allows you to gate off. the clkena signals are supported at the clock network level instead of at the pll output counter level. So, when the enable signal is. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal. the input signal is taken over. Clock Enable Signal.

From www.youtube.com

How to Generate a Clock Signal with a 555 timer The Learning Circuit Clock Enable Signal the clkena signals are supported at the clock network level instead of at the pll output counter level. The module has an input. the input signal is taken over when the enable signal is high (level) and the clock rises (edge). this article will review the common fpga resources that allow us to efficiently generate and distribute. Clock Enable Signal.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Enable Signal the input signal is taken over when the enable signal is high (level) and the clock rises (edge). This allows you to gate off. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal. The intel® max® 10 devices support clkena signals at the gclk network level.. Clock Enable Signal.

From www.slideserve.com

PPT Unit 11 Latches and FlipFlops PowerPoint Presentation ID4832180 Clock Enable Signal The module has an input. the clkena signals are supported at the clock network level instead of at the pll output counter level. The intel® max® 10 devices support clkena signals at the gclk network level. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. the clock enable. Clock Enable Signal.

From lcamtuf.substack.com

Clocks in digital circuits lcamtuf’s thing Clock Enable Signal The intel® max® 10 devices support clkena signals at the gclk network level. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). The module has. Clock Enable Signal.

From www.youtube.com

simulation clock circuit multisim YouTube Clock Enable Signal So, when the enable signal is. the clkena signals are supported at the clock network level instead of at the pll output counter level. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). The module has an input. to avoid the fpga. Clock Enable Signal.

From www.semanticscholar.org

Figure 2 from Timing closure of clock enable signals on a 32 nm Intel Clock Enable Signal the input signal is taken over when the enable signal is high (level) and the clock rises (edge). the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). to avoid the fpga timing issues or clock domain crossing issues, it is recommended to. Clock Enable Signal.

From www.analogictips.com

When to buffer and when to drive signals Clock Enable Signal So, when the enable signal is. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). The intel® max® 10 devices support clkena signals at the gclk network level. the input signal is taken over when the enable signal is high (level) and the. Clock Enable Signal.

From www.ece.northwestern.edu

Signal Generator (Simulink Reference) Clock Enable Signal the clkena signals are supported at the clock network level instead of at the pll output counter level. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). the following verilog clock generator module has three parameters to tweak the three different properties. Clock Enable Signal.

From electronics.stackexchange.com

How to generate a single pulse signal with existing clock signal Clock Enable Signal the clkena signals are supported at the clock network level instead of at the pll output counter level. the input signal is taken over when the enable signal is high (level) and the clock rises (edge). So, when the enable signal is. the following verilog clock generator module has three parameters to tweak the three different properties. Clock Enable Signal.

From www.researchgate.net

Write enable signal generation logic for two output memories Clock Enable Signal the clkena signals are supported at the clock network level instead of at the pll output counter level. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above.. Clock Enable Signal.

From www.youtube.com

What is Clock signal? Explain Clock signal, Define Clock signal Clock Enable Signal This allows you to gate off. the input signal is taken over when the enable signal is high (level) and the clock rises (edge). the clkena signals are supported at the clock network level instead of at the pll output counter level. the clkena signals are supported at the clock network level instead of at the pll. Clock Enable Signal.

From www.researchgate.net

17 Component throttling with forcing clock modulation using enable Clock Enable Signal This allows you to gate off. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. the input signal is taken over when the enable. Clock Enable Signal.

From www.slideserve.com

PPT EKT 124 / 3 DIGITAL ELEKTRONIC 1 PowerPoint Presentation, free Clock Enable Signal the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. This allows you to gate off. The intel® max® 10 devices support clkena signals at the. Clock Enable Signal.

From ww2.mathworks.cn

Clock, Reset, and Enable Signals MATLAB & Simulink MathWorks 中国 Clock Enable Signal So, when the enable signal is. The intel® max® 10 devices support clkena signals at the gclk network level. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in. Clock Enable Signal.

From usermanualtractors.z1.web.core.windows.net

Clock Signal Generator Circuit Diagram Clock Enable Signal So, when the enable signal is. The module has an input. The intel® max® 10 devices support clkena signals at the gclk network level. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal. This allows you to gate off. the input signal is taken over when. Clock Enable Signal.

From www.chegg.com

Solved (10 points) Use a 4bit register with synchronous Clock Enable Signal This allows you to gate off. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. So, when the enable signal is. the clkena signals are supported at the clock network level instead of at the pll output counter level. the input signal is taken over when the enable. Clock Enable Signal.

From birthofasynth.org

SM2010 System Clock Clock Enable Signal the clkena signals are supported at the clock network level instead of at the pll output counter level. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). this article will review the common fpga resources that allow us to efficiently generate and. Clock Enable Signal.

From www.researchgate.net

A simplified gated clock network consisting of five sinks, an Clock Enable Signal the clkena signals are supported at the clock network level instead of at the pll output counter level. So, when the enable signal is. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock. Clock Enable Signal.

From bestengineeringprojects.com

Clock Signal Generator Circuit Best Engineering Projects Clock Enable Signal The intel® max® 10 devices support clkena signals at the gclk network level. So, when the enable signal is. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). the input signal is taken over when the enable signal is high (level) and the. Clock Enable Signal.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Clock Enable Signal this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. This allows you to gate off. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. to avoid the fpga timing issues or clock domain crossing issues, it. Clock Enable Signal.

From eternallearning.github.io

Inverter vs Buffer based clock tree Eternal Learning Electrical Clock Enable Signal to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal. the clkena signals are supported at the clock network level instead of at the pll output counter level. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above.. Clock Enable Signal.

From www.chegg.com

The Primitives subdirectory contains a D flipflop Clock Enable Signal the input signal is taken over when the enable signal is high (level) and the clock rises (edge). the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. This allows you to gate off. the clkena signals are supported at the clock network level instead of at the pll. Clock Enable Signal.

From www.researchgate.net

Clock skew in a loop of 25 and 64 oscillators (top view) where the Clock Enable Signal The module has an input. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal. The intel® max® 10 devices support clkena signals at the gclk network level. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. . Clock Enable Signal.

From eureka.patsnap.com

Control method and circuit for stopping clock signal Eureka Patsnap Clock Enable Signal the input signal is taken over when the enable signal is high (level) and the clock rises (edge). the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. to avoid the fpga timing issues or clock domain crossing issues, it is recommended to generate a slow clock enable signal.. Clock Enable Signal.

From itecnotes.com

Electrical How to turn a clock signal into a logic high that also Clock Enable Signal the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). this article will review the common fpga resources that allow us to efficiently generate and distribute clock signals throughout a system. the clkena signals are supported at the clock network level instead of. Clock Enable Signal.

From teamvlsi.com

Integrated Clock Gating (ICG) Cell in VLSI Team VLSI Clock Enable Signal The intel® max® 10 devices support clkena signals at the gclk network level. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). The module has an input. So, when the enable signal is. to avoid the fpga timing issues or clock domain crossing. Clock Enable Signal.

From slideplayer.com

DIGITAL 2 EKT 221. Today’s Outline Register Transfer Clock Gating Clock Enable Signal The module has an input. the clkena signals are supported at the clock network level instead of at the pll output counter level. the clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). this article will review the common fpga resources that allow. Clock Enable Signal.