Latch To Latch Timing . Figure below shows the waveforms for setup and hold checks. clock for timing synchronization. Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing.

from www.chegg.com

for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. clock for timing synchronization. Timing path from positive edge flop to positive level latch.

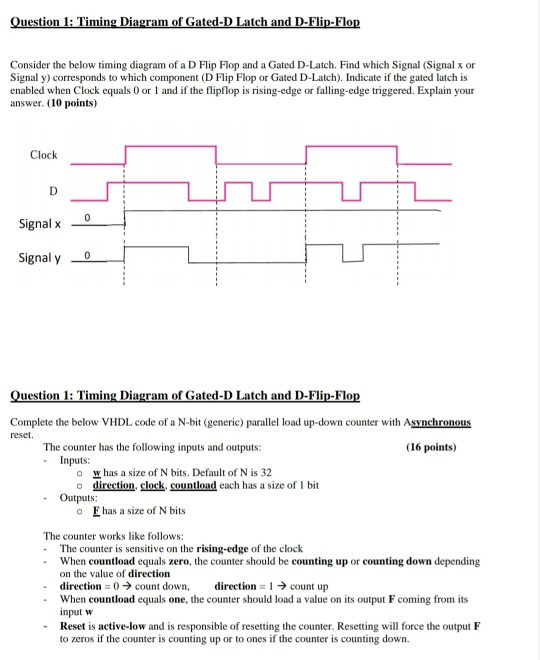

Solved Question 1 Timing Diagram of GatedD Latch and

Latch To Latch Timing clock for timing synchronization. Figure below shows the waveforms for setup and hold checks. clock for timing synchronization. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing.

From www.youtube.com

SR Latch Timing Diagram YouTube Latch To Latch Timing Clocks serve to slow down signals that are too fast. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. clock for timing synchronization. Latch To Latch Timing.

From diagramlibadlertaghw6.z13.web.core.windows.net

Latch Vs Flip Flop Timing Diagram Latch To Latch Timing Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. clock for timing synchronization. Latch To Latch Timing.

From malaydanan.blogspot.com

Sr Latch Timing Diagram malaydanan Latch To Latch Timing Clocks serve to slow down signals that are too fast. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. Figure below shows the waveforms for setup and hold checks. Latch To Latch Timing.

From www.youtube.com

Setup and Hold Time of a Latch YouTube Latch To Latch Timing clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. Latch To Latch Timing.

From www.slideserve.com

PPT Chapter 6 Introduction to Sequential Devices PowerPoint Latch To Latch Timing Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Latch To Latch Timing.

From ranger.uta.edu

D Latch Timing Constraints Latch To Latch Timing Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Latch To Latch Timing.

From www.slideserve.com

PPT D Latch PowerPoint Presentation, free download ID2400394 Latch To Latch Timing clock for timing synchronization. Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Latch To Latch Timing.

From www.edn.com

Ensure closure with proper latch constraints EDN Latch To Latch Timing for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. clock for timing synchronization. Figure below shows the waveforms for setup and hold checks. Latch To Latch Timing.

From vlsiuniverse.blogspot.com

Time borrowing in latches Latch To Latch Timing for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. clock for timing synchronization. Latch To Latch Timing.

From www.youtube.com

How to use Latch and Unlatch PLC instructions with example YouTube Latch To Latch Timing Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Figure below shows the waveforms for setup and hold checks. Latch To Latch Timing.

From userdataleominster.z21.web.core.windows.net

Sr Latch Time Diagram Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Clocks serve to slow down signals that are too fast. clock for timing synchronization. Latch To Latch Timing.

From circuithoarronnehorodc.z4.web.core.windows.net

D Latch Circuit Time Diagram Latch To Latch Timing Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. Latch To Latch Timing.

From olukraine.weebly.com

Positive d latch timing diagram olukraine Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. clock for timing synchronization. Clocks serve to slow down signals that are too fast. Latch To Latch Timing.

From www.numerade.com

SOLVED SR Latch Timing Diagram Which one of the timing diagrams Latch To Latch Timing Clocks serve to slow down signals that are too fast. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. clock for timing synchronization. Figure below shows the waveforms for setup and hold checks. Latch To Latch Timing.

From www.chegg.com

Solved 3) Fill in the timing diagram for a Gated D Latch 4) Latch To Latch Timing Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. Figure below shows the waveforms for setup and hold checks. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. clock for timing synchronization. Latch To Latch Timing.

From wirelistcyaniding.z14.web.core.windows.net

Latch Vs Flip Flop Timing Diagram Latch To Latch Timing for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. clock for timing synchronization. Latch To Latch Timing.

From tech.tdzire.com

Latch Setup and Hold Timing Checks Basics TechnologyTdzire Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. clock for timing synchronization. Latch To Latch Timing.

From www.researchgate.net

(a) A pulsedlatch is approximated as a flipflop and (b) it follows a Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. Latch To Latch Timing.

From www.chegg.com

Solved Question 1 Timing Diagram of GatedD Latch and Latch To Latch Timing Timing path from positive edge flop to positive level latch. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. Latch To Latch Timing.

From ar.inspiredpencil.com

Sr Latch Timing Diagram Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. clock for timing synchronization. Clocks serve to slow down signals that are too fast. Latch To Latch Timing.

From www.youtube.com

20b D Latch Transparency D Latch Timing Diagram Digital Logic Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Clocks serve to slow down signals that are too fast. Latch To Latch Timing.

From ranger.uta.edu

D Latch Timing Diagram Latch To Latch Timing Timing path from positive edge flop to positive level latch. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. Latch To Latch Timing.

From webdocs.cs.ualberta.ca

Dlatch timing parameters Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. clock for timing synchronization. Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. Latch To Latch Timing.

From slidetodoc.com

Timing in Sequential circuits Stabilization time of a Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Timing path from positive edge flop to positive level latch. clock for timing synchronization. Latch To Latch Timing.

From julicrush.weebly.com

Positive d latch timing diagram Julicrush Latch To Latch Timing for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Figure below shows the waveforms for setup and hold checks. clock for timing synchronization. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. Latch To Latch Timing.

From vlsiuniverse.blogspot.com

Lockup latch principle, application and timing Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. clock for timing synchronization. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. Latch To Latch Timing.

From mommylery.weebly.com

Positive d latch timing diagram mommylery Latch To Latch Timing for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. clock for timing synchronization. Figure below shows the waveforms for setup and hold checks. Latch To Latch Timing.

From www.researchgate.net

Timing diagram of a SR latch with nor gates. Gate propagation delays Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Latch To Latch Timing.

From tech.tdzire.com

Latch Setup and Hold Timing Checks Basics TechnologyTdzire Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. clock for timing synchronization. Timing path from positive edge flop to positive level latch. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Latch To Latch Timing.

From www.edn.com

Ensure closure with proper latch constraints EDN Latch To Latch Timing clock for timing synchronization. Timing path from positive edge flop to positive level latch. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. Latch To Latch Timing.

From schematiclibexogen123.z4.web.core.windows.net

Latch Schematic Diagram Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Latch To Latch Timing.

From tech.tdzire.com

Latch Setup and Hold Timing Checks Basics TechnologyTdzire Latch To Latch Timing clock for timing synchronization. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Latch To Latch Timing.

From schematicdreyer2010j3.z22.web.core.windows.net

Timing Diagram Of Sr Latch Latch To Latch Timing Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. clock for timing synchronization. for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. Latch To Latch Timing.

From guidewetbenchps.z14.web.core.windows.net

Sr Latch Time Diagram Latch To Latch Timing for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. clock for timing synchronization. Timing path from positive edge flop to positive level latch. Clocks serve to slow down signals that are too fast. Figure below shows the waveforms for setup and hold checks. Latch To Latch Timing.

From stewart-switch.com

D Latch Timing Diagram Latch To Latch Timing for latches, the setup relationship is to the opening edge of the latch, which allows time borrowing. clock for timing synchronization. Figure below shows the waveforms for setup and hold checks. Clocks serve to slow down signals that are too fast. Timing path from positive edge flop to positive level latch. Latch To Latch Timing.