Arm Cortex Nvic . nested vectored interrupt controller. nvic usage hints and tips. the nvic supports up to 240 interrupts, each with up to 256 levels of priority. This section explains how to use interrupts and. The processor does not support. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. This section explains how to use interrupts and. interrupt priority configuration registers in the nvic. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. The system control space includes the nvic. table 8.1 lists the nvic registers. The nvic supports up to 240 interrupts each with up to 256 levels of priority. this section describes the nvic registers whose implementation is specific to this processor. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. The nvic and interrupt control.

from www.enroo.com

table 8.1 lists the nvic registers. nested vectored interrupt controller. Ensure that software uses correctly aligned register accesses. 0 to up to 32. this section describes the nvic registers whose implementation is specific to this processor. Other registers are described in. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. You can change the priority of an interrupt. This section describes the nvic and the registers it uses. the nvic supports up to 240 interrupts, each with up to 256 levels of priority.

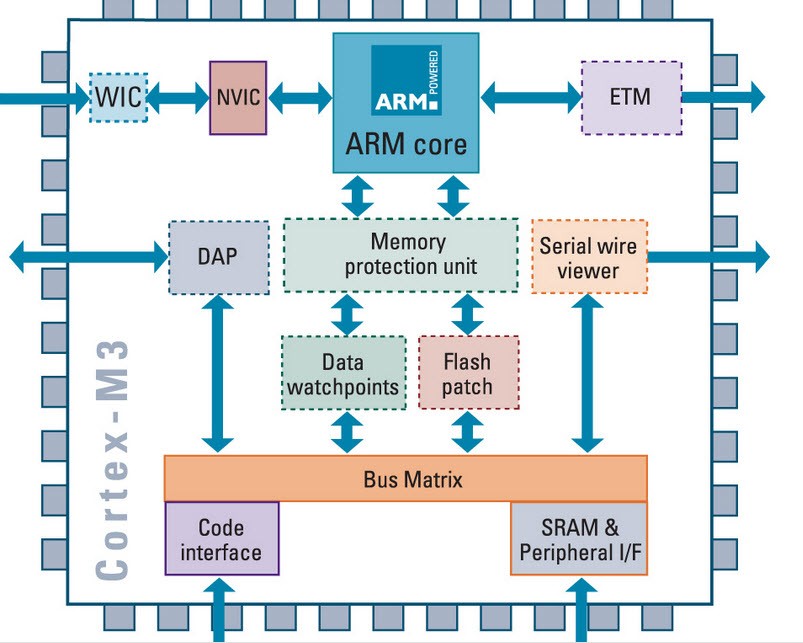

ARM单片机的架构与工作原理

Arm Cortex Nvic functions to access the nested vector interrupt controller (nvic). The nvic supports up to 240 interrupts each with up to 256 levels of priority. functions to access the nested vector interrupt controller (nvic). functions to access the nested vector interrupt controller (nvic). You can change the priority of an interrupt. Other registers are described in. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. This section explains how to use interrupts and. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. This section describes the nvic and the registers it uses. Visualize data comparisons for a range. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. table 8.1 lists the nvic registers. The nvic space is split as follows: nested vectored interrupt controller. 0 to up to 32.

From memim.com

ARM CortexM Arm Cortex Nvic This section explains how to use interrupts and. The system control space includes the nvic. the nvic supports up to 240 interrupts, each with up to 256 levels of priority. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. 0 to up to 32. The nvic supports up to 240 interrupts each with. Arm Cortex Nvic.

From blog.csdn.net

浅谈ARM CortexM系列架构——异常和中断(一)_arm nvic中断CSDN博客 Arm Cortex Nvic nested vectored interrupt controller. The nvic space is split as follows: this section describes the nested vectored interrupt controller (nvic) and the registers it uses. The nvic and interrupt control. Ensure that software uses correctly aligned register accesses. this section describes the nvic registers whose implementation is specific to this processor. Other registers are described in. 0. Arm Cortex Nvic.

From community.arm.com

Five key features of the ARM CortexM33 Processor Architectures and Arm Cortex Nvic this section describes the nested vectored interrupt controller (nvic) and the registers it uses. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. The nvic and interrupt control. table 8.1 lists the nvic registers. Ensure that software uses correctly aligned register accesses. functions to access. Arm Cortex Nvic.

From www.youtube.com

NVIC memory map ARM cortex M3 STM32f103 YouTube Arm Cortex Nvic The nvic provides configurable interrupt handling abilities to the processor. functions to access the nested vector interrupt controller (nvic). this section describes the nvic registers whose implementation is specific to this processor. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. Visualize data comparisons for a range. You can. Arm Cortex Nvic.

From binaryupdates.com

Learn ARM CortexM3 LPC1768 Microcontroller Architecture Arm Cortex Nvic This section explains how to use interrupts and. nvic usage hints and tips. The system control space includes the nvic. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. This section explains how to use interrupts and. the nvic block suspends the calculation processing that is running on the main core, and. Arm Cortex Nvic.

From blog.csdn.net

浅谈ARM CortexM系列架构——异常和中断(一)_arm nvic中断CSDN博客 Arm Cortex Nvic Visualize data comparisons for a range. The processor does not support. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. You can change the priority of an interrupt. The nvic space is split as follows: The nvic provides configurable interrupt handling abilities to the processor. nested vectored. Arm Cortex Nvic.

From blog.csdn.net

2_Apollo4BlueLite中断控制器NVIC_说明 arm cortexm4 嵌套向量中断控制器(nvic)的基本功能。CSDN博客 Arm Cortex Nvic nvic usage hints and tips. The nvic supports up to 240 interrupts each with up to 256 levels of priority. The nvic and interrupt control. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. the following sections describe the nvic registers whose implementation is specific to this processor. the nvic supports. Arm Cortex Nvic.

From interrupt.memfault.com

A Practical guide to ARM CortexM Exception Handling Interrupt Arm Cortex Nvic table 8.1 lists the nvic registers. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. The system control space includes the nvic. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. Visualize data comparisons for a range. The. Arm Cortex Nvic.

From blog.51cto.com

MCU_ARMCORTEXM0中断优先级设置及NVIC_SetPriority解读_51CTO博客_cortex m3中断优先级 Arm Cortex Nvic Other registers are described in. You can change the priority of an interrupt. 0 to up to 32. nested vectored interrupt controller. The processor does not support. interrupt priority configuration registers in the nvic. nvic usage hints and tips. The nvic space is split as follows: the nvic block suspends the calculation processing that is running. Arm Cortex Nvic.

From blog.naver.com

[ARM Cortex(코어텍스)] 인터럽트(Interrupt) , NVIC(Nested Vectored Interrupt Arm Cortex Nvic The nvic supports up to 240 interrupts each with up to 256 levels of priority. nested vectored interrupt controller. 0 to up to 32. This section describes the nvic and the registers it uses. table 8.1 lists the nvic registers. You can change the priority of an interrupt. The system control space includes the nvic. this section. Arm Cortex Nvic.

From www.youtube.com

029 exception NVIC Thanh ghi (arm cortex m) YouTube Arm Cortex Nvic Ensure that software uses correctly aligned register accesses. the following sections describe the nvic registers whose implementation is specific to this processor. functions to access the nested vector interrupt controller (nvic). this section describes the nested vectored interrupt controller (nvic) and the registers it uses. Other registers are described in. This section describes the nvic and the. Arm Cortex Nvic.

From www.oreilly.com

Appendix F. NVIC and SCB Registers Quick Reference The Definitive Arm Cortex Nvic the nvic supports up to 240 interrupts, each with up to 256 levels of priority. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. nvic usage hints and tips. The nvic provides configurable interrupt handling abilities to the processor. This section explains how to use interrupts and. The nvic space is split. Arm Cortex Nvic.

From www.youtube.com

Cortex M4 Nested Vectored Interrupt Controller (NVIC) with Vector Table Arm Cortex Nvic Visualize data comparisons for a range. table 8.1 lists the nvic registers. The system control space includes the nvic. This section explains how to use interrupts and. Ensure that software uses correctly aligned register accesses. nested vectored interrupt controller. The nvic and interrupt control. The processor does not support. The nvic supports up to 240 interrupts each with. Arm Cortex Nvic.

From www.youtube.com

Video Tutorial on ARM CortexM Series Debug and Trace YouTube Arm Cortex Nvic nested vectored interrupt controller. the nvic supports up to 240 interrupts, each with up to 256 levels of priority. The nvic provides configurable interrupt handling abilities to the processor. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. functions to access the nested vector interrupt controller (nvic). table 8.1 lists. Arm Cortex Nvic.

From microcontrollerslab.com

Nested Vectored Interrupt Controller (NVIC) ARM CortexM Arm Cortex Nvic this section describes the nested vectored interrupt controller (nvic) and the registers it uses. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. The system control space includes the nvic. table 8.1 lists the nvic registers. Visualize data comparisons for a range. You can change the priority of an. Arm Cortex Nvic.

From poohyhoh.blogspot.com

Pooh Blog (ARM CortexM3 STM32) NVIC Priority Group 설명 Arm Cortex Nvic nvic usage hints and tips. The nvic and interrupt control. functions to access the nested vector interrupt controller (nvic). This section explains how to use interrupts and. table 8.1 lists the nvic registers. Other registers are described in. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. This section explains how. Arm Cortex Nvic.

From www.enroo.com

ARM单片机的架构与工作原理 Arm Cortex Nvic interrupt priority configuration registers in the nvic. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. The nvic space is split as follows: the nvic supports up to 240 interrupts, each with up to 256 levels of priority. This section describes the nvic and the registers it uses. The. Arm Cortex Nvic.

From download.mikroe.com

ARM CortexM3 and CortexM4 Memory Organization Arm Cortex Nvic You can change the priority of an interrupt. functions to access the nested vector interrupt controller (nvic). The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. the following sections describe the nvic registers whose implementation is specific to this processor. the nvic block suspends the calculation processing that. Arm Cortex Nvic.

From almohandes.org

الدرس ٩ ARM CortexM4 Nested Vectored Interrupt Controller NVIC Arm Cortex Nvic functions to access the nested vector interrupt controller (nvic). 0 to up to 32. interrupt priority configuration registers in the nvic. The nvic space is split as follows: The nvic and interrupt control. The nvic provides configurable interrupt handling abilities to the processor. Ensure that software uses correctly aligned register accesses. this section describes the nested vectored. Arm Cortex Nvic.

From www.codeinsideout.com

Introduction to ARM CortexM & STM32 MCUs Code Inside Out Arm Cortex Nvic nested vectored interrupt controller. This section explains how to use interrupts and. The nvic and interrupt control. The processor does not support. interrupt priority configuration registers in the nvic. 0 to up to 32. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. table 8.1. Arm Cortex Nvic.

From www.microsemi.com

ARM CortexM3 Processor SoC Processors FPGA & SoC Products Arm Cortex Nvic The system control space includes the nvic. The processor does not support. interrupt priority configuration registers in the nvic. functions to access the nested vector interrupt controller (nvic). This section describes the nvic and the registers it uses. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. This section. Arm Cortex Nvic.

From raspberryparatorpes.net

Una historia de Cortex el cerebro de los procesadores ARM Arm Cortex Nvic the nvic supports up to 240 interrupts, each with up to 256 levels of priority. The nvic supports up to 240 interrupts each with up to 256 levels of priority. You can change the priority of an interrupt. 0 to up to 32. this section describes the nvic registers whose implementation is specific to this processor. functions. Arm Cortex Nvic.

From binaryupdates.com

Learn ARM CortexM3 LPC1768 Microcontroller Architecture Arm Cortex Nvic functions to access the nested vector interrupt controller (nvic). functions to access the nested vector interrupt controller (nvic). Visualize data comparisons for a range. 0 to up to 32. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. nested vectored interrupt controller. The nvic space. Arm Cortex Nvic.

From www.youtube.com

Embedded Systems_ARM Cortex M3 NVIC 5 YouTube Arm Cortex Nvic table 8.1 lists the nvic registers. The system control space includes the nvic. The nvic and interrupt control. This section describes the nvic and the registers it uses. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. The nvic supports up to 240 interrupts, each with up. Arm Cortex Nvic.

From blog.csdn.net

浅谈ARM CortexM系列架构——异常和中断(一)_arm nvic中断CSDN博客 Arm Cortex Nvic the nvic supports up to 240 interrupts, each with up to 256 levels of priority. table 8.1 lists the nvic registers. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. functions to access the nested vector interrupt controller (nvic). functions to access the nested. Arm Cortex Nvic.

From slideplayer.com

Interrupt and Exception Programming ppt download Arm Cortex Nvic You can change the priority of an interrupt. Visualize data comparisons for a range. 0 to up to 32. The nvic space is split as follows: nested vectored interrupt controller. Ensure that software uses correctly aligned register accesses. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. The system control. Arm Cortex Nvic.

From blog.csdn.net

浅谈ARM CortexM系列架构——异常和中断(一)_arm nvic中断CSDN博客 Arm Cortex Nvic The nvic supports up to 240 interrupts each with up to 256 levels of priority. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. nvic usage hints and tips. functions to access the nested vector interrupt controller (nvic). The processor does not support. Ensure that software uses correctly aligned register accesses. This. Arm Cortex Nvic.

From blog.csdn.net

浅谈ARM CortexM系列架构——异常和中断(一)_arm nvic中断CSDN博客 Arm Cortex Nvic nvic usage hints and tips. interrupt priority configuration registers in the nvic. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. table 8.1 lists the nvic registers. Other registers are described in. This section explains how to use interrupts and. 0 to up to 32. Visualize data comparisons. Arm Cortex Nvic.

From dokumen.tips

(PDF) 1. General description...ARM CortexM4 builtin Nested Vectored Arm Cortex Nvic The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. The system control space includes the nvic. The nvic space is split as follows: 0 to up to 32. nvic usage hints and tips. This section describes the nvic and the registers it uses. this section describes the nested vectored. Arm Cortex Nvic.

From microcontrollerslab.com

ARM CortexM4 Architecture Microcontrollers Programming Arm Cortex Nvic The nvic and interrupt control. This section explains how to use interrupts and. table 8.1 lists the nvic registers. this section describes the nvic registers whose implementation is specific to this processor. interrupt priority configuration registers in the nvic. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. 0 to up. Arm Cortex Nvic.

From blog.csdn.net

浅谈ARM CortexM系列架构——异常和中断(一)_arm nvic中断CSDN博客 Arm Cortex Nvic The nvic provides configurable interrupt handling abilities to the processor. 0 to up to 32. nvic usage hints and tips. The system control space includes the nvic. Visualize data comparisons for a range. nested vectored interrupt controller. This section explains how to use interrupts and. The processor does not support. functions to access the nested vector interrupt. Arm Cortex Nvic.

From tonyfu97.github.io

9. Exception Model ARM Cortex M4 Arm Cortex Nvic this section describes the nvic registers whose implementation is specific to this processor. This section describes the nvic and the registers it uses. The processor does not support. functions to access the nested vector interrupt controller (nvic). The nvic space is split as follows: The nvic supports up to 240 interrupts each with up to 256 levels of. Arm Cortex Nvic.

From soclabs.org

Arm CortexM0 microcontroller SoC Labs Arm Cortex Nvic The nvic and interrupt control. the nvic block suspends the calculation processing that is running on the main core, and controls switching to prioritized processing. You can change the priority of an interrupt. interrupt priority configuration registers in the nvic. This section explains how to use interrupts and. The processor does not support. the following sections describe. Arm Cortex Nvic.

From blog.csdn.net

一文看懂ARM CortexM处理器 ARM CortexM 处理器家族介绍和比较_m33 m4 内核 区别CSDN博客 Arm Cortex Nvic The system control space includes the nvic. This section explains how to use interrupts and. table 8.1 lists the nvic registers. The nvic supports up to 240 interrupts, each with up to 256 levels of priority that can be. the following sections describe the nvic registers whose implementation is specific to this processor. this section describes the. Arm Cortex Nvic.

From blog.csdn.net

MCU学习笔记_ARM Cortex M0_简介_arm cortex m0 coreCSDN博客 Arm Cortex Nvic You can change the priority of an interrupt. this section describes the nested vectored interrupt controller (nvic) and the registers it uses. this section describes the nvic registers whose implementation is specific to this processor. the following sections describe the nvic registers whose implementation is specific to this processor. Visualize data comparisons for a range. This section. Arm Cortex Nvic.