Interface Code In Uvm . An interface is a bundle of signals or nets through which a testbench communicates with a design. The put interfaces are used to send, or put, transactions to other components. The get interfaces are used to retrieve. A virtual interface is a variable that represents an interface. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; All the interface variables/methods can be. Open verification methodology (ovm) and. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the.

from www10.edacafe.com

The put interfaces are used to send, or put, transactions to other components. All the interface variables/methods can be. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. Open verification methodology (ovm) and. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. The get interfaces are used to retrieve. An interface is a bundle of signals or nets through which a testbench communicates with a design. A virtual interface is a variable that represents an interface. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and.

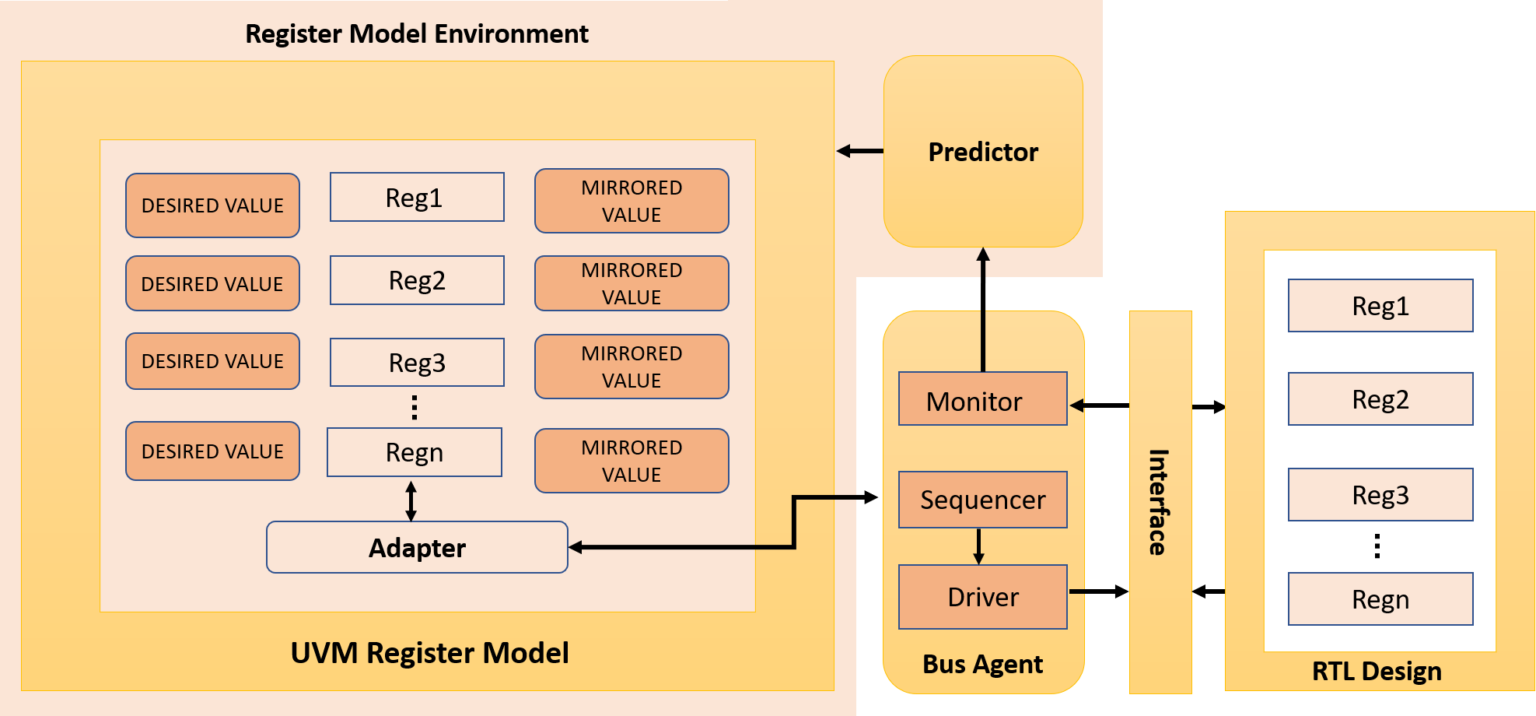

EDACafe Automating the UVM Register Abstraction Layer (RAL)

Interface Code In Uvm The get interfaces are used to retrieve. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. Open verification methodology (ovm) and. The put interfaces are used to send, or put, transactions to other components. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; All the interface variables/methods can be. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. The get interfaces are used to retrieve. A virtual interface is a variable that represents an interface. An interface is a bundle of signals or nets through which a testbench communicates with a design.

From www.techdesignforums.com

UVM the Universal Verification Methodology, moving to deployment Interface Code In Uvm Open verification methodology (ovm) and. The get interfaces are used to retrieve. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. The virtual interfaces can. Interface Code In Uvm.

From blog.csdn.net

6UVM configuration机制_uvm如何把interface传递到testcase里面CSDN博客 Interface Code In Uvm The get interfaces are used to retrieve. All the interface variables/methods can be. An interface is a bundle of signals or nets through which a testbench communicates with a design. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. Open verification methodology (ovm) and. The put interfaces are used. Interface Code In Uvm.

From www.maven-silicon.com

What is UVM Factory? Maven Silicon Interface Code In Uvm This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. The put interfaces are used to send, or put, transactions to other components. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. A virtual interface. Interface Code In Uvm.

From www.learnuvmverification.com

UVM Configuration Object Concept Universal Verification Methodology Interface Code In Uvm This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. The put interfaces are used to send, or put, transactions to other components. All the interface variables/methods can be. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; A virtual interface is a variable that. Interface Code In Uvm.

From www.youtube.com

Course UVM in Systemverilog 1 L2.1 Introduction to UVM YouTube Interface Code In Uvm Open verification methodology (ovm) and. All the interface variables/methods can be. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. The virtual interfaces can be. Interface Code In Uvm.

From www.slideserve.com

PPT SVA Encapsulation in UVM enabling phase and configuration aware Interface Code In Uvm An interface is a bundle of signals or nets through which a testbench communicates with a design. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. All the interface variables/methods can. Interface Code In Uvm.

From mavink.com

Uvm Architecture Diagram Interface Code In Uvm The virtual interfaces can be passed as arguments to the tasks, functions, or methods; We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. The put interfaces are used to send, or put, transactions to other components. All the interface variables/methods can be. A virtual interface. Interface Code In Uvm.

From www.learnuvmverification.com

UVM Sequences and Transactions Application Universal Verification Interface Code In Uvm The put interfaces are used to send, or put, transactions to other components. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. The get interfaces are used to retrieve. Open verification methodology (ovm) and. All the interface variables/methods can be. We'll go through the design specification, write a test. Interface Code In Uvm.

From www.chipverify.com

UVM Agent uvm_agent Interface Code In Uvm Open verification methodology (ovm) and. A virtual interface is a variable that represents an interface. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; An interface is a bundle of signals or nets through which a testbench communicates with a design. All the interface variables/methods can be. The put interfaces are used to send, or. Interface Code In Uvm.

From zhuanlan.zhihu.com

UVM入门到进阶:uvm cookbook(1) 知乎 Interface Code In Uvm A virtual interface is a variable that represents an interface. Open verification methodology (ovm) and. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. Uvm. Interface Code In Uvm.

From evision-systems.de

Aldec RivieraPRO™ UVMGenerator eVision Systems GmbH Interface Code In Uvm A virtual interface is a variable that represents an interface. All the interface variables/methods can be. Open verification methodology (ovm) and. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. The put interfaces are used to send, or put, transactions to other components. Uvm is. Interface Code In Uvm.

From verificationacademy.com

SystemVerilog Interfaces Introduction to UVM Interface Code In Uvm A virtual interface is a variable that represents an interface. The get interfaces are used to retrieve. All the interface variables/methods can be. An interface is a bundle of signals or nets through which a testbench communicates with a design. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such. Interface Code In Uvm.

From cluelogic.com

UVM Tutorial for Candy Lovers 13. Configuration Database ClueLogic Interface Code In Uvm Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. The get interfaces are used to retrieve. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. We'll go through the design specification, write a test. Interface Code In Uvm.

From blog.csdn.net

6UVM configuration机制_uvm如何把interface传递到testcase里面CSDN博客 Interface Code In Uvm This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. All the interface variables/methods can be. An interface is a bundle of signals or nets through which a testbench communicates with a design. Open verification methodology (ovm) and. A virtual interface is a variable that represents an interface. The virtual. Interface Code In Uvm.

From www.youtube.com

UVM Ques Describe the handshake between uvm_sequence, uvm_sequencer Interface Code In Uvm The virtual interfaces can be passed as arguments to the tasks, functions, or methods; A virtual interface is a variable that represents an interface. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog. Interface Code In Uvm.

From verificationacademy.com

Sequences for Interface UVM Verification Academy Interface Code In Uvm The put interfaces are used to send, or put, transactions to other components. Open verification methodology (ovm) and. An interface is a bundle of signals or nets through which a testbench communicates with a design. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. The. Interface Code In Uvm.

From semiconductorclub.com

How UVM RAL Works? Semiconductor Club Interface Code In Uvm The put interfaces are used to send, or put, transactions to other components. The get interfaces are used to retrieve. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; A virtual interface is a variable that represents an interface. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog. Interface Code In Uvm.

From www.semanticscholar.org

Figure 1 from A Flexible UVMBased Verification Framework Reusable with Interface Code In Uvm A virtual interface is a variable that represents an interface. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; All the interface variables/methods can be. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. An interface is a bundle of. Interface Code In Uvm.

From blog.csdn.net

UVM 验证方法学之interface学习系列文章(三)进阶《含类参数化的interface》_uvm中interface带有参数怎么半CSDN博客 Interface Code In Uvm We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. All the interface variables/methods can be. The put interfaces are used to send, or put, transactions to other components. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment. Interface Code In Uvm.

From asicwhale.github.io

uvm environment ASIC Notes Interface Code In Uvm An interface is a bundle of signals or nets through which a testbench communicates with a design. The get interfaces are used to retrieve. A virtual interface is a variable that represents an interface. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. Uvm is. Interface Code In Uvm.

From theartofverification.com

Typical UVM Testbench Architecture The Art Of Verification Interface Code In Uvm The get interfaces are used to retrieve. An interface is a bundle of signals or nets through which a testbench communicates with a design. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. All the interface variables/methods can be. This is an example showing how. Interface Code In Uvm.

From gbu-taganskij.ru

Detailed Explanation Of The Easier UVM Coding Guidelines, 44 OFF Interface Code In Uvm A virtual interface is a variable that represents an interface. Open verification methodology (ovm) and. The get interfaces are used to retrieve. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. The put interfaces are used to send, or put, transactions to other components. This. Interface Code In Uvm.

From www.techdesignforums.com

Accelerate your UVM adoption and usage with an IDE Interface Code In Uvm The virtual interfaces can be passed as arguments to the tasks, functions, or methods; This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. All the interface variables/methods can be. The put interfaces are used to send, or put, transactions to other components. Uvm is based on the systemverilog language,. Interface Code In Uvm.

From www10.edacafe.com

EDACafe Automating the UVM Register Abstraction Layer (RAL) Interface Code In Uvm Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. All the interface variables/methods can be. The put interfaces are used to send, or put, transactions to other components. We'll go through the design specification, write a test plan that details how the design will be. Interface Code In Uvm.

From github.com

GitHub EngAhmed21/SPIusingUVM Implementation of Serial Peripheral Interface Code In Uvm Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench. Interface Code In Uvm.

From theartofverification.com

How Virtual Interface Can Be Pass Using Uvm_config_db In The UVM Interface Code In Uvm The get interfaces are used to retrieve. All the interface variables/methods can be. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. Open verification methodology. Interface Code In Uvm.

From verificationacademy.com

UVM Framework (UVMF) Track Track Interface Code In Uvm The virtual interfaces can be passed as arguments to the tasks, functions, or methods; The put interfaces are used to send, or put, transactions to other components. All the interface variables/methods can be. The get interfaces are used to retrieve. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the.. Interface Code In Uvm.

From blog.csdn.net

6UVM configuration机制_uvm如何把interface传递到testcase里面CSDN博客 Interface Code In Uvm An interface is a bundle of signals or nets through which a testbench communicates with a design. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. All the interface variables/methods can. Interface Code In Uvm.

From www.slideserve.com

PPT SVA Encapsulation in UVM enabling phase and configuration aware Interface Code In Uvm This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. We'll go through the design specification, write a test plan that details how the design will be tested, develop a uvm testbench structure and. Open verification methodology (ovm) and. The get interfaces are used to retrieve. A virtual interface is. Interface Code In Uvm.

From blog.csdn.net

6UVM configuration机制_uvm如何把interface传递到testcase里面CSDN博客 Interface Code In Uvm A virtual interface is a variable that represents an interface. All the interface variables/methods can be. The get interfaces are used to retrieve. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. An interface is a bundle of signals or nets through which a testbench communicates with a design.. Interface Code In Uvm.

From www.mentor.com

UVM Tips and Tricks Mentor Graphics Interface Code In Uvm This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. The get interfaces are used to retrieve. The virtual interfaces can be passed as arguments to the tasks, functions, or methods; A virtual interface is a variable that represents an interface. Uvm is based on the systemverilog language, so you. Interface Code In Uvm.

From www.youtube.com

UVM SV Basics 4 Interface UVC YouTube Interface Code In Uvm This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. An interface is a bundle of signals or nets through which a testbench communicates with a design. The put interfaces are used to send, or put, transactions to other components. The virtual interfaces can be passed as arguments to the. Interface Code In Uvm.

From blog.csdn.net

UVM_TLM通信机制_uvm port有哪些 tlm机制哪三种CSDN博客 Interface Code In Uvm The put interfaces are used to send, or put, transactions to other components. Open verification methodology (ovm) and. A virtual interface is a variable that represents an interface. The get interfaces are used to retrieve. An interface is a bundle of signals or nets through which a testbench communicates with a design. This is an example showing how to access. Interface Code In Uvm.

From www.asictronix.com

UVM Sequencer and Driver Interface Code In Uvm This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. The put interfaces are used to send, or put, transactions to other components. Open verification methodology (ovm) and. Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes,. Interface Code In Uvm.

From www.youtube.com

UVM SV Basics 13 Interface UVC Environment YouTube Interface Code In Uvm Uvm is based on the systemverilog language, so you should have a basic understanding of systemverilog syntax and constructs, such as classes, inheritance, and. This is an example showing how to access a parameterized systemverilog interface from a uvm verification environment by calling the. All the interface variables/methods can be. Open verification methodology (ovm) and. The get interfaces are used. Interface Code In Uvm.