What Is Clock Latency In Vlsi . the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. Synchronous systems use a clock to keep operations in sequence. in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. clock latency has been explained in this video tutorial along with. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing.

from dxojuqyzr.blob.core.windows.net

in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. Synchronous systems use a clock to keep operations in sequence. in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. clock latency has been explained in this video tutorial along with. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency.

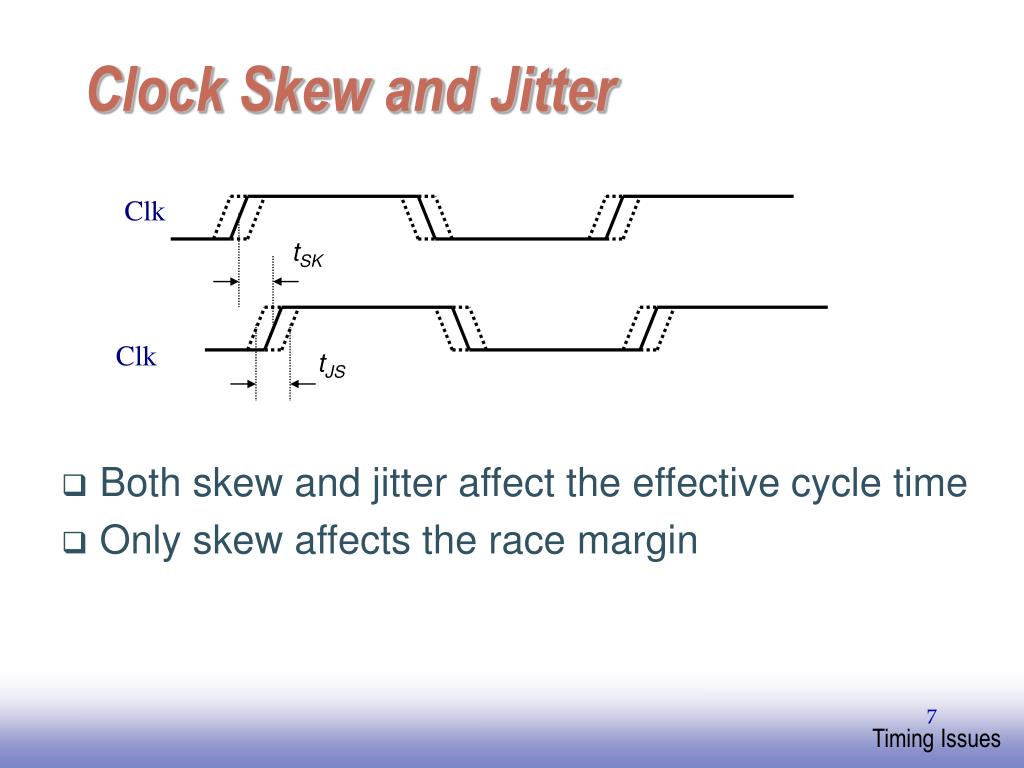

Clock Skew And Clock Jitter In Vlsi at Lee Eastman blog

What Is Clock Latency In Vlsi in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. Synchronous systems use a clock to keep operations in sequence. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. clock latency has been explained in this video tutorial along with.

From dxojuqyzr.blob.core.windows.net

Clock Skew And Clock Jitter In Vlsi at Lee Eastman blog What Is Clock Latency In Vlsi in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is. What Is Clock Latency In Vlsi.

From www.academia.edu

(PDF) ClockLatencyAware PreCTS for better Timing Closure in VLSI What Is Clock Latency In Vlsi the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. in electronic design automation (eda) tools, specifying clock latency is crucial. What Is Clock Latency In Vlsi.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design What Is Clock Latency In Vlsi in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. clock latency has been explained in this video tutorial along with. Synchronous systems. What Is Clock Latency In Vlsi.

From www.youtube.com

Clock Latency in VLSI Source Latency Network Latency Insertion What Is Clock Latency In Vlsi clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. Synchronous systems use a clock to keep operations in sequence. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. clock latency has been explained in this video tutorial along with.. What Is Clock Latency In Vlsi.

From vlsi-soc.blogspot.com

VLSI SoC Design Clock Jargon Important Terms What Is Clock Latency In Vlsi in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. Synchronous systems use a clock to keep operations in sequence. the time taken by clock signal to reach from. What Is Clock Latency In Vlsi.

From www.youtube.com

Clock Tree Synthesis CTS VLSI Physical Design Flow YouTube What Is Clock Latency In Vlsi clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. Synchronous systems use a clock to keep operations in sequence. in short, latency is the value we give the tool before. What Is Clock Latency In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Clock Latency In Vlsi clock latency has been explained in this video tutorial along with. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. in general, clock latency (or clock insertion delay) is. What Is Clock Latency In Vlsi.

From ivlsi.com

Standard Design Constraints (.sdc) in VLSI Physical Design What Is Clock Latency In Vlsi clock latency has been explained in this video tutorial along with. Synchronous systems use a clock to keep operations in sequence. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. the time taken by clock signal to reach from clock source to the clock pin. What Is Clock Latency In Vlsi.

From mahajankankit.medium.com

STA Explanation of Clock Skew Concepts in VLSI by ANKIT MAHAJAN Medium What Is Clock Latency In Vlsi in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. clock latency has been explained in this video tutorial along with. in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. the time taken by clock signal to. What Is Clock Latency In Vlsi.

From vlsitutorials.com

Constraining timing paths in Synthesis Part 2 VLSI Tutorials What Is Clock Latency In Vlsi in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. the time taken by clock signal to reach from clock source to the clock pin. What Is Clock Latency In Vlsi.

From blogs.cuit.columbia.edu

Clock Tree Latency Skew Uncertainty What Is Clock Latency In Vlsi clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. Synchronous systems use a clock to keep operations in sequence. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. clock latency has been explained in this video tutorial along with.. What Is Clock Latency In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Clock Latency In Vlsi in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal. What Is Clock Latency In Vlsi.

From vlsiuniverse.blogspot.com

Virtual clock purpose and timing What Is Clock Latency In Vlsi the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. clock latency, also known as clock insertion delay, refers to the. What Is Clock Latency In Vlsi.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design What Is Clock Latency In Vlsi in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. in short, latency is the value we give the tool before cts, and insertion delay is the actual value. What Is Clock Latency In Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis vlsi What Is Clock Latency In Vlsi in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. clock latency has been explained in this video tutorial along with. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. Synchronous systems use a clock to keep operations in sequence.. What Is Clock Latency In Vlsi.

From www.youtube.com

Introduction to Clocks YouTube What Is Clock Latency In Vlsi Synchronous systems use a clock to keep operations in sequence. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. the time taken. What Is Clock Latency In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Clock Latency In Vlsi in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. the time taken by clock signal to reach from clock source to the. What Is Clock Latency In Vlsi.

From www.youtube.com

Clock Latency (Source & Network Latency) STA VLSI Excellence Do 👍 What Is Clock Latency In Vlsi clock latency has been explained in this video tutorial along with. in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. the. What Is Clock Latency In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Clock Latency In Vlsi clock latency has been explained in this video tutorial along with. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. the time taken by clock signal to reach from. What Is Clock Latency In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Clock Latency In Vlsi clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is. What Is Clock Latency In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Clock Latency In Vlsi Synchronous systems use a clock to keep operations in sequence. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. in short, latency is the value we. What Is Clock Latency In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Clock Latency In Vlsi in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. Synchronous systems use a clock to keep operations in sequence. in short, latency. What Is Clock Latency In Vlsi.

From www.vlsijunction.com

VLSI Physical Design Clock Skew What Is Clock Latency In Vlsi in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. clock latency, also known as clock insertion delay, refers. What Is Clock Latency In Vlsi.

From 8.136.218.141

Static Timing Analysis Physical Design VLSI BackEnd Adventure What Is Clock Latency In Vlsi in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. Synchronous systems use a clock to keep operations in sequence. clock latency has been explained in this video tutorial along with.. What Is Clock Latency In Vlsi.

From vlsitalks.com

CTS (CLOCK TREE SYNTHESIS) VLSI TALKS What Is Clock Latency In Vlsi in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. clock latency has been explained in this video tutorial along with. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. in general, clock latency (or. What Is Clock Latency In Vlsi.

From www.youtube.com

VLSI Physical Design Clock Tree Synthesis (CTS) YouTube What Is Clock Latency In Vlsi in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. clock latency has been explained in this video tutorial along with. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as. What Is Clock Latency In Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru What Is Clock Latency In Vlsi clock latency has been explained in this video tutorial along with. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. Synchronous systems use a clock to keep operations in sequence.. What Is Clock Latency In Vlsi.

From www.vlsisystemdesign.com

VSD 2019 DefaultRules Based Clock Tree Synthesis contest VLSI System What Is Clock Latency In Vlsi Synchronous systems use a clock to keep operations in sequence. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. in. What Is Clock Latency In Vlsi.

From www.vlsisystemdesign.com

Selective NonDefault Rules Based Clock Tree Synthesis using open What Is Clock Latency In Vlsi Synchronous systems use a clock to keep operations in sequence. in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. in general, clock latency (or clock insertion delay) is defined as. What Is Clock Latency In Vlsi.

From nguyenquanicd.blogspot.com

[STA] Các thông số của clock trong phân tích timing VLSI TECHNOLOGY What Is Clock Latency In Vlsi in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. Synchronous systems use a clock to keep operations in sequence. in general, clock latency (or. What Is Clock Latency In Vlsi.

From tech.tdzire.com

What are virtual clocks and why they are needed ? TechnologyTdzire What Is Clock Latency In Vlsi in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. Synchronous systems use a clock to keep operations in sequence. in short, latency is the value we. What Is Clock Latency In Vlsi.

From dxojuqyzr.blob.core.windows.net

Clock Skew And Clock Jitter In Vlsi at Lee Eastman blog What Is Clock Latency In Vlsi in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. the time taken by clock signal to reach from clock source to the clock pin of a particular flip. What Is Clock Latency In Vlsi.

From www.youtube.com

PD Lec 51 How to balance skew and latency? CTS Clock Tree Synthesis What Is Clock Latency In Vlsi clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. the time taken by clock signal to reach from clock source to the. What Is Clock Latency In Vlsi.

From vlsi-freaks.blogspot.com

VLSI freaks virtual clocks and their usage What Is Clock Latency In Vlsi in electronic design automation (eda) tools, specifying clock latency is crucial for achieving accurate timing. clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. the time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is. What Is Clock Latency In Vlsi.

From blogs.cuit.columbia.edu

update clock latency What Is Clock Latency In Vlsi in short, latency is the value we give the tool before cts, and insertion delay is the actual value after cts. clock latency has been explained in this video tutorial along with. in general, clock latency (or clock insertion delay) is defined as the amount of time taken by the clock signal in traveling from. in. What Is Clock Latency In Vlsi.