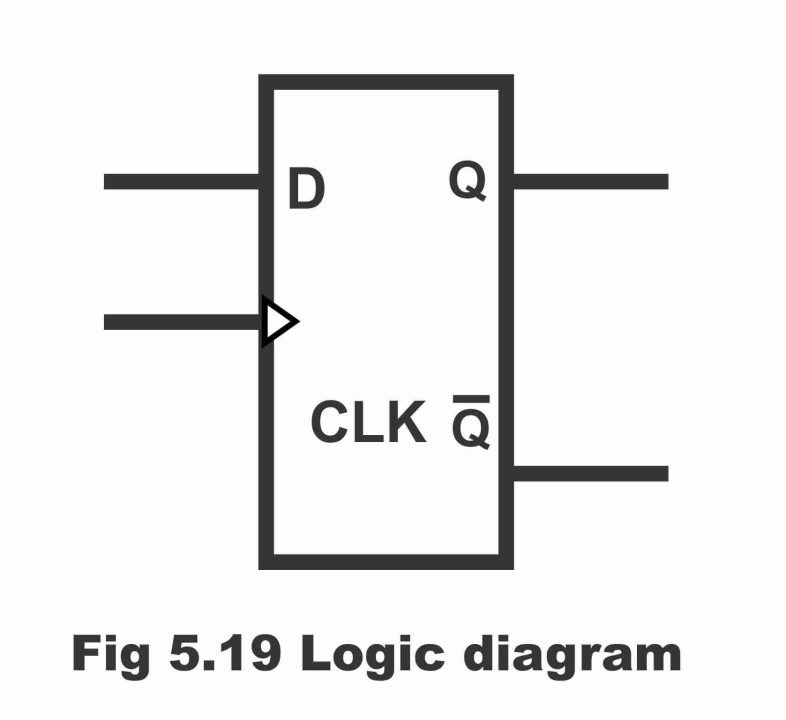

D Flip Flop With Logic Gates . If clock is low, the enable signal to master flip flop is high. A d flip flop stores 2 bits of information at the. D is the data input. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. In this project, we will show how to build a d flip flop from nand gates. D flip flops can be used in place of sr flip flops where you need only set and reset state. Due to its versatility they are available as ic packages. It stores one bit of data. The operation of positive edge triggered master slave d flip flop is explained below. A flip flop is an electronic device that can store bits of information. Clk is the clock input. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and tying them together. The d latch is a logic circuit most frequently used for storing data in digital systems.

from www.electroniclinic.com

Due to its versatility they are available as ic packages. A d flip flop stores 2 bits of information at the. It stores one bit of data. D flip flops can be used in place of sr flip flops where you need only set and reset state. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and tying them together. The d latch is a logic circuit most frequently used for storing data in digital systems. A flip flop is an electronic device that can store bits of information. In this project, we will show how to build a d flip flop from nand gates. The operation of positive edge triggered master slave d flip flop is explained below. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle.

D FlipFlop and EdgeTriggered D FlipFlop With Circuit diagram and

D Flip Flop With Logic Gates Due to its versatility they are available as ic packages. If clock is low, the enable signal to master flip flop is high. In this project, we will show how to build a d flip flop from nand gates. D flip flops can be used in place of sr flip flops where you need only set and reset state. The d latch is a logic circuit most frequently used for storing data in digital systems. Due to its versatility they are available as ic packages. The operation of positive edge triggered master slave d flip flop is explained below. It stores one bit of data. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. Clk is the clock input. A d flip flop stores 2 bits of information at the. D is the data input. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and tying them together. A flip flop is an electronic device that can store bits of information.

From www.youtube.com

Clocked D Flip Flop using NAND Gates with Truth Table and Circuit D Flip Flop With Logic Gates The d latch is a logic circuit most frequently used for storing data in digital systems. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and tying them together. In this project, we will show how to build a d. D Flip Flop With Logic Gates.

From slidetodoc.com

FlipFlops Logic Circuits Gates are referred to as D Flip Flop With Logic Gates D is the data input. A d flip flop stores 2 bits of information at the. A flip flop is an electronic device that can store bits of information. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and tying. D Flip Flop With Logic Gates.

From www.electroniclinic.com

RS Flipflop Circuits using NAND Gates and NOR Gates D Flip Flop With Logic Gates This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. Due to its versatility they are available as ic packages. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in. D Flip Flop With Logic Gates.

From slidetodoc.com

FlipFlops Logic Circuits Gates are referred to as D Flip Flop With Logic Gates D flip flops can be used in place of sr flip flops where you need only set and reset state. D is the data input. The d latch is a logic circuit most frequently used for storing data in digital systems. A d flip flop stores 2 bits of information at the. A flip flop is an electronic device that. D Flip Flop With Logic Gates.

From mungfali.com

D Flip Flop Nand Gates D Flip Flop With Logic Gates If clock is low, the enable signal to master flip flop is high. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. A flip flop is an electronic device that can store bits of information. In this project, we will show how to. D Flip Flop With Logic Gates.

From itecnotes.com

Logisim Using Custom D Flip Flop in Logisim Valuable Tech Notes D Flip Flop With Logic Gates A flip flop is an electronic device that can store bits of information. D flip flops can be used in place of sr flip flops where you need only set and reset state. Clk is the clock input. The d latch is a logic circuit most frequently used for storing data in digital systems. Due to its versatility they are. D Flip Flop With Logic Gates.

From www.electroniclinic.com

D FlipFlop and EdgeTriggered D FlipFlop With Circuit diagram and D Flip Flop With Logic Gates D is the data input. The operation of positive edge triggered master slave d flip flop is explained below. A flip flop is an electronic device that can store bits of information. If clock is low, the enable signal to master flip flop is high. Clk is the clock input. It stores one bit of data. This approach will help. D Flip Flop With Logic Gates.

From www.electroniclinic.com

RS Flipflop Circuits using NAND Gates and NOR Gates D Flip Flop With Logic Gates D flip flops can be used in place of sr flip flops where you need only set and reset state. It stores one bit of data. If clock is low, the enable signal to master flip flop is high. A d flip flop stores 2 bits of information at the. The operation of positive edge triggered master slave d flip. D Flip Flop With Logic Gates.

From www.electroniclinic.com

RS Flipflop Circuits using NAND Gates and NOR Gates D Flip Flop With Logic Gates D flip flops can be used in place of sr flip flops where you need only set and reset state. If clock is low, the enable signal to master flip flop is high. D is the data input. Due to its versatility they are available as ic packages. It stores one bit of data. In this project, we will show. D Flip Flop With Logic Gates.

From www.electroniclinic.com

D FlipFlop and EdgeTriggered D FlipFlop With Circuit diagram and D Flip Flop With Logic Gates D flip flops can be used in place of sr flip flops where you need only set and reset state. D is the data input. The d latch is a logic circuit most frequently used for storing data in digital systems. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented. D Flip Flop With Logic Gates.

From dcaclab.com

D Flip Flop Explained in Detail DCAClab Blog D Flip Flop With Logic Gates Clk is the clock input. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. If clock is low, the enable signal to master flip flop is high. A d flip flop stores 2 bits of information at the. In this project, we will. D Flip Flop With Logic Gates.

From www.youtube.com

GATE 2000 ECE Sequential circuit using D flip flop and logic gates is D Flip Flop With Logic Gates If clock is low, the enable signal to master flip flop is high. It stores one bit of data. The operation of positive edge triggered master slave d flip flop is explained below. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and. D Flip Flop With Logic Gates.

From www.electricaltechnology.org

Digital FlipFlops SR, D, JK and T Types of FlipFlops D Flip Flop With Logic Gates In this project, we will show how to build a d flip flop from nand gates. The operation of positive edge triggered master slave d flip flop is explained below. Due to its versatility they are available as ic packages. A flip flop is an electronic device that can store bits of information. This approach will help us understand how. D Flip Flop With Logic Gates.

From www.nutsvolts.com

Small Logic Gates — The building blocks of versatile digital circuits D Flip Flop With Logic Gates The operation of positive edge triggered master slave d flip flop is explained below. It stores one bit of data. A flip flop is an electronic device that can store bits of information. A d flip flop stores 2 bits of information at the. D flip flops or data flip flops or delay flip flops can be designed using sr. D Flip Flop With Logic Gates.

From wiringdiagramsuspiring.z14.web.core.windows.net

Positive Edge Triggered D Flip Flop Circuit Diagram D Flip Flop With Logic Gates If clock is low, the enable signal to master flip flop is high. D flip flops can be used in place of sr flip flops where you need only set and reset state. Clk is the clock input. The d latch is a logic circuit most frequently used for storing data in digital systems. The operation of positive edge triggered. D Flip Flop With Logic Gates.

From wiremanualthompson.z13.web.core.windows.net

Sr To D Flip Flop Circuit Diagram D Flip Flop With Logic Gates D flip flops can be used in place of sr flip flops where you need only set and reset state. In this project, we will show how to build a d flip flop from nand gates. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the. D Flip Flop With Logic Gates.

From schematicdiagram75.blogspot.com

Logic Diagram And Truth Table Of Sr Flip Flops In Electronics T Flip D Flip Flop With Logic Gates If clock is low, the enable signal to master flip flop is high. A d flip flop stores 2 bits of information at the. It stores one bit of data. Clk is the clock input. The d latch is a logic circuit most frequently used for storing data in digital systems. The operation of positive edge triggered master slave d. D Flip Flop With Logic Gates.

From usermanualfoulness.z21.web.core.windows.net

D Flip Flop Negative Edge Triggered D Flip Flop With Logic Gates D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and tying them together. The d latch is a logic circuit most frequently used for storing data in digital systems. D flip flops can be used in place of sr flip. D Flip Flop With Logic Gates.

From www.wellpcb.com

Transistor Flip Flop A Sequential Logic Circuit for Storing Binary Data D Flip Flop With Logic Gates This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. The d latch is a logic circuit most frequently used for storing data in digital systems. In this project, we will show how to build a d flip flop from nand gates. If clock. D Flip Flop With Logic Gates.

From slidetodoc.com

FlipFlops Logic Circuits Gates are referred to as D Flip Flop With Logic Gates D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and tying them together. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. D. D Flip Flop With Logic Gates.

From slidetodoc.com

FlipFlops Logic Circuits Gates are referred to as D Flip Flop With Logic Gates In this project, we will show how to build a d flip flop from nand gates. If clock is low, the enable signal to master flip flop is high. D flip flops can be used in place of sr flip flops where you need only set and reset state. The operation of positive edge triggered master slave d flip flop. D Flip Flop With Logic Gates.

From slidetodoc.com

FlipFlops Logic Circuits Gates are referred to as D Flip Flop With Logic Gates D flip flops can be used in place of sr flip flops where you need only set and reset state. Due to its versatility they are available as ic packages. A flip flop is an electronic device that can store bits of information. The d latch is a logic circuit most frequently used for storing data in digital systems. If. D Flip Flop With Logic Gates.

From byjus.com

FlipFlop Types, Conversion and Applications GATE Notes D Flip Flop With Logic Gates If clock is low, the enable signal to master flip flop is high. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and tying them together. A flip flop is an electronic device that can store bits of information. It. D Flip Flop With Logic Gates.

From www.electroniclinic.com

D FlipFlop and EdgeTriggered D FlipFlop With Circuit diagram and D Flip Flop With Logic Gates Due to its versatility they are available as ic packages. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. It stores one bit of data. The d latch is a logic circuit most frequently used for storing data in digital systems. In this. D Flip Flop With Logic Gates.

From www.electroniclinic.com

RS Flipflop Circuits using NAND Gates and NOR Gates D Flip Flop With Logic Gates Due to its versatility they are available as ic packages. The operation of positive edge triggered master slave d flip flop is explained below. A d flip flop stores 2 bits of information at the. It stores one bit of data. D flip flops can be used in place of sr flip flops where you need only set and reset. D Flip Flop With Logic Gates.

From www.numerade.com

SOLVED A sequential circuit using D flip flop and logic gates are D Flip Flop With Logic Gates D is the data input. A d flip flop stores 2 bits of information at the. D flip flops can be used in place of sr flip flops where you need only set and reset state. The operation of positive edge triggered master slave d flip flop is explained below. It stores one bit of data. In this project, we. D Flip Flop With Logic Gates.

From www.researchgate.net

Logic gates and flipflops. A. A symbol for an ANDNOT logic gate, with D Flip Flop With Logic Gates If clock is low, the enable signal to master flip flop is high. The d latch is a logic circuit most frequently used for storing data in digital systems. Clk is the clock input. The operation of positive edge triggered master slave d flip flop is explained below. This approach will help us understand how a program counter may be. D Flip Flop With Logic Gates.

From graphicmaths.com

GraphicMaths Simple flipflops D Flip Flop With Logic Gates In this project, we will show how to build a d flip flop from nand gates. If clock is low, the enable signal to master flip flop is high. Due to its versatility they are available as ic packages. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each. D Flip Flop With Logic Gates.

From www.engineersgarage.com

VHDL Tutorial 16 Design a D flipflop using VHDL D Flip Flop With Logic Gates A d flip flop stores 2 bits of information at the. If clock is low, the enable signal to master flip flop is high. D is the data input. The operation of positive edge triggered master slave d flip flop is explained below. Clk is the clock input. A flip flop is an electronic device that can store bits of. D Flip Flop With Logic Gates.

From manualdatametrists.z21.web.core.windows.net

Sr Flip Flop Circuit Diagram Using Nand Gates D Flip Flop With Logic Gates This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. A flip flop is an electronic device that can store bits of information. A d flip flop stores 2 bits of information at the. Clk is the clock input. The operation of positive edge. D Flip Flop With Logic Gates.

From itecnotes.com

Digital Logic D Flip Flop with Asynchronous Reset Circuit Design D Flip Flop With Logic Gates The operation of positive edge triggered master slave d flip flop is explained below. In this project, we will show how to build a d flip flop from nand gates. D flip flops or data flip flops or delay flip flops can be designed using sr flip flops by connecting a not gate in between s and r inputs and. D Flip Flop With Logic Gates.

From www.electroniclinic.com

D FlipFlop and EdgeTriggered D FlipFlop With Circuit diagram and D Flip Flop With Logic Gates Clk is the clock input. In this project, we will show how to build a d flip flop from nand gates. A flip flop is an electronic device that can store bits of information. This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle.. D Flip Flop With Logic Gates.

From www.researchgate.net

DFlip Flop using Transmission gates Download Scientific Diagram D Flip Flop With Logic Gates Due to its versatility they are available as ic packages. D is the data input. A d flip flop stores 2 bits of information at the. In this project, we will show how to build a d flip flop from nand gates. It stores one bit of data. If clock is low, the enable signal to master flip flop is. D Flip Flop With Logic Gates.

From www.youtube.com

D Flip flop using NAND gates explained YouTube D Flip Flop With Logic Gates This approach will help us understand how a program counter may be designed within the cpu and automatically incremented for each tick of the clock cycle. In this project, we will show how to build a d flip flop from nand gates. Due to its versatility they are available as ic packages. The operation of positive edge triggered master slave. D Flip Flop With Logic Gates.

From fixenginemerciful.z4.web.core.windows.net

Edge Triggered D Type Flip Flop D Flip Flop With Logic Gates It stores one bit of data. A flip flop is an electronic device that can store bits of information. D is the data input. The operation of positive edge triggered master slave d flip flop is explained below. If clock is low, the enable signal to master flip flop is high. The d latch is a logic circuit most frequently. D Flip Flop With Logic Gates.