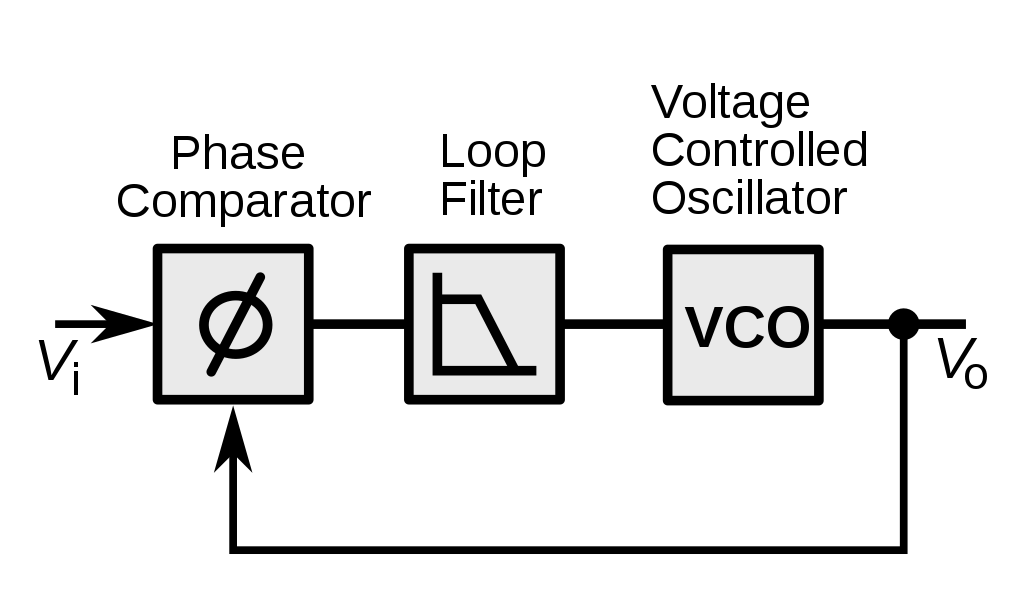

Phase Locked Loop Clock Generator . With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. The pfd’s output current pulses are filtered and integrated to generate a voltage.

from zhuanlan.zhihu.com

With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a.

PhaseLocked Loops 的思考(一) 知乎

Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz.

From www.semanticscholar.org

Figure 1 from A LowN Phase Locked Loop Clock Generator with Delay Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.researchgate.net

Multiplereferences phaselocked loop implementation Download Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.azoquantum.com

The Principles of PhaseLocked Loops in Analog Signals Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.semanticscholar.org

Figure 1 from A LowN Phase Locked Loop Clock Generator with Delay Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.researchgate.net

Alldigital phaselocked loop, used to lock the DPWM switching Phase Locked Loop Clock Generator With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From zapadpribor.com

Clock generators, phaselocked loop systems, frequency synthesizers Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From studylib.net

Phase Locked Loop Basics Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From irpsiea4schematic.z21.web.core.windows.net

Phase Locked Loop Schematic Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From www.analog.com

PhaseLocked Loop (PLL) Fundamentals Analog Devices Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From zapadpribor.com

Clock generators, phaselocked loop systems, frequency synthesizers Phase Locked Loop Clock Generator With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From www.aliexpress.com

Serial control High precision frequency doubling clock signal pulse Phase Locked Loop Clock Generator With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From zapadpribor.com

Clock generators, phaselocked loop systems, frequency synthesizers Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From www.mdpi.com

Electronics Free FullText Comparison of PhaseLocked Loops Used Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From github.com

GitHub SanaullahHukam/PhaseLockedLoopBasedTunableClockGenerator Phase Locked Loop Clock Generator With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From www.youtube.com

What is Phase Lock Loop (PLL)? How Phase Lock Loop Works ? PLL Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.jos.ac.cn

CMOS analog and mixedsignal phaselocked loops An overview Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From exotdgxvh.blob.core.windows.net

Monolithic PhaseLocked Loops And Clock Recovery Circuits Theory And Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From studylib.net

PhaseLocked Loop Based Clock Generators Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.slideserve.com

PPT ECE4331, Fall, 2009 Communication Systems PowerPoint Presentation Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From eureka.patsnap.com

Phaselocked loop modeling method and system based on timedelay phase Phase Locked Loop Clock Generator With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From datasheetspdf.com

AZ12000 Arizona Microtek Generator, Distributor, Stock and Best Price Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From datasheetspdf.com

AZ12010 Arizona Microtek Generator, Distributor, Stock and Best Price Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From www.slideserve.com

PPT PhaseLocked Loop (PLL) PowerPoint Presentation, free download Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From slideplayer.com

Implementation of Phase Locked Loop (PLL) by using IC 565 and IC555 Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From www.keysight.com

Consider the Source Part 1 What is a Phase Locked Loop? Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From www.next.gr

Fullband phase locked loop circuit diagram fast under PLL Circuits Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.youtube.com

Phase Locked Loop Tutorial the basics of PLLs YouTube Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From studylib.net

FS7140 Programmable PhaseLocked Loop Clock Generator Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. The pfd’s output current pulses are filtered and integrated to generate a voltage. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.slideserve.com

PPT PhaseLocked Loop (PLL) PowerPoint Presentation, free download Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From data.epo.org

Phaselocked loop clock signal generator Patent 0472211 Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From zapadpribor.com

Clock generators, phaselocked loop systems, frequency synthesizers Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From www.analogictips.com

Phase Locked Loop A fundamental building block in wireless technology Phase Locked Loop Clock Generator The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. Phase Locked Loop Clock Generator.

From www.slideserve.com

PPT Phase Locked Loops PowerPoint Presentation, free download ID271463 Phase Locked Loop Clock Generator With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.

From hackaday.com

Unlock The Phase Locked Loop Hackaday Phase Locked Loop Clock Generator The proposed adpll architecture uses both a. With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. Phase Locked Loop Clock Generator.

From zhuanlan.zhihu.com

PhaseLocked Loops 的思考(一) 知乎 Phase Locked Loop Clock Generator With phase locked loop analog frequency synthesizers using integer n and fractional n topologies designers can generate stable clock frequencies up to 30 ghz. The pfd’s output current pulses are filtered and integrated to generate a voltage. The proposed adpll architecture uses both a. Phase Locked Loop Clock Generator.