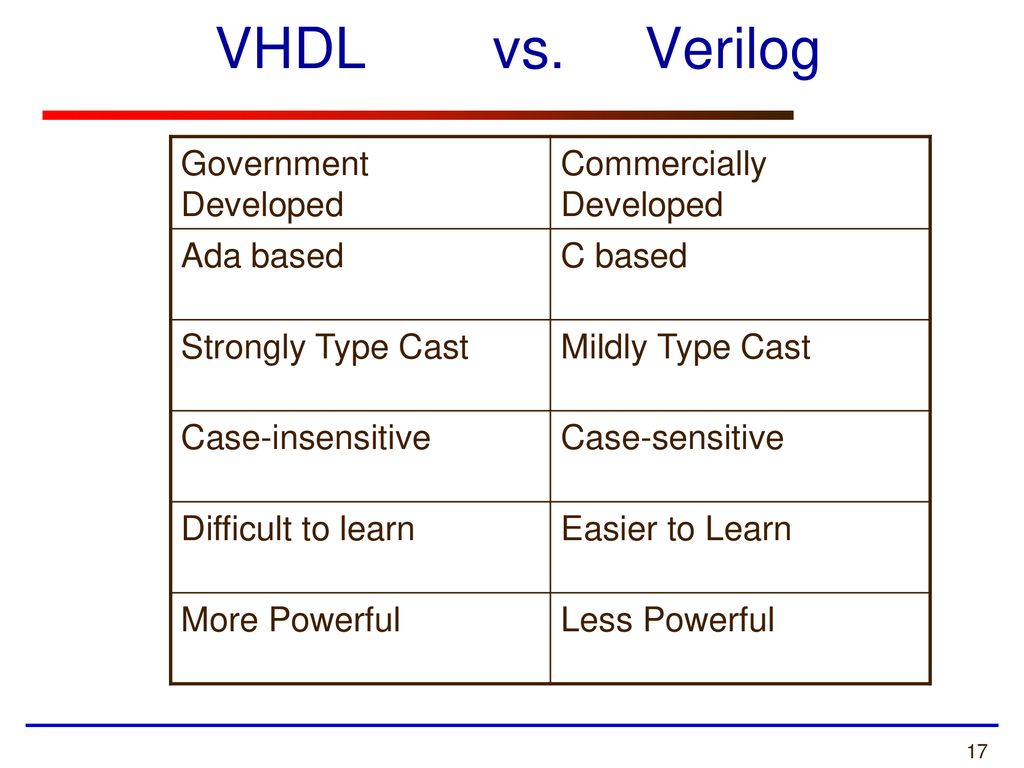

Difference Between Assembly And Vhdl . There is a fundamental difference between c. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. Using vhdl affords the user concurrent system descriptions. For the first part of your question, about the motivations of using one or the other: Verilog's syntax is similar to c, making it easier for those with a background in c or. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. They are called hdls, or hardware. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. When learning fpga design, there are two languages to choose from, verilog or vhdl. The ease of learning verilog or vhdl depends on the individual's background and preferences.

from slideplayer.com

Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. For the first part of your question, about the motivations of using one or the other: The ease of learning verilog or vhdl depends on the individual's background and preferences. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. Verilog's syntax is similar to c, making it easier for those with a background in c or. When learning fpga design, there are two languages to choose from, verilog or vhdl. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. There is a fundamental difference between c. Using vhdl affords the user concurrent system descriptions.

Introduction to VHDL for Synthesis ppt download

Difference Between Assembly And Vhdl When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. There is a fundamental difference between c. For the first part of your question, about the motivations of using one or the other: Using vhdl affords the user concurrent system descriptions. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. When learning fpga design, there are two languages to choose from, verilog or vhdl. Verilog's syntax is similar to c, making it easier for those with a background in c or. They are called hdls, or hardware. The ease of learning verilog or vhdl depends on the individual's background and preferences. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code.

From pediaa.com

What is the Difference Between Signal and Variable in VHDL Difference Between Assembly And Vhdl The ease of learning verilog or vhdl depends on the individual's background and preferences. There is a fundamental difference between c. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. For the first part of your question, about the motivations of using one or the other: They are. Difference Between Assembly And Vhdl.

From pediaa.com

What is the Difference Between Simulation and Synthesis in VHDL Difference Between Assembly And Vhdl For the first part of your question, about the motivations of using one or the other: When learning fpga design, there are two languages to choose from, verilog or vhdl. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the. Difference Between Assembly And Vhdl.

From askanydifference.com

Verilog vs VHDL Difference and Comparison Difference Between Assembly And Vhdl The ease of learning verilog or vhdl depends on the individual's background and preferences. There is a fundamental difference between c. Verilog's syntax is similar to c, making it easier for those with a background in c or. When learning fpga design, there are two languages to choose from, verilog or vhdl. Vhdl is a dataflow language, which means it. Difference Between Assembly And Vhdl.

From www.researchgate.net

Comparison of some aspects of VHDLAMS and Modelica Download Table Difference Between Assembly And Vhdl When learning fpga design, there are two languages to choose from, verilog or vhdl. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. Vhdl and verilog are two prominent hardware description languages (hdls) used in. Difference Between Assembly And Vhdl.

From www.slideserve.com

PPT Verilog Intro Part 1 PowerPoint Presentation, free download ID Difference Between Assembly And Vhdl They are called hdls, or hardware. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. For the first part of your question, about the motivations of using one or the other: Using vhdl affords the user concurrent system descriptions. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and. Difference Between Assembly And Vhdl.

From www.engineersgarage.com

Design 3×8 decoder and 8×3 encoder using VHDL Difference Between Assembly And Vhdl Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. Verilog's syntax is similar to c, making it easier for those with a background in c or. For the first part of your question, about the motivations of using one or the other: Assembly languages allow you type instructions from your cpu's instruction set in. Difference Between Assembly And Vhdl.

From surf-vhdl.com

VHDL Structural Modeling Style Difference Between Assembly And Vhdl The ease of learning verilog or vhdl depends on the individual's background and preferences. For the first part of your question, about the motivations of using one or the other: They are called hdls, or hardware. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. When looking at verilog and vhdl code at the. Difference Between Assembly And Vhdl.

From www.maven-silicon.com

Difference between simulation and synthesis in VHDL? Maven Silicon Difference Between Assembly And Vhdl When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. When learning fpga design, there are two languages to choose from, verilog or vhdl. Vhdl is a dataflow language, which means it can simultaneously consider every. Difference Between Assembly And Vhdl.

From www.slideserve.com

PPT Microprocessor and Assembly Language PowerPoint Presentation Difference Between Assembly And Vhdl When learning fpga design, there are two languages to choose from, verilog or vhdl. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. For the first part of your question, about the motivations of using one or the other: Assembly languages allow you type instructions from your cpu's instruction set in plain text, use. Difference Between Assembly And Vhdl.

From www.slideserve.com

PPT LOGIC DESIGN WITH VHDL PowerPoint Presentation, free download Difference Between Assembly And Vhdl Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. When learning fpga design, there are two. Difference Between Assembly And Vhdl.

From www.aldec.com

Simulation Libraries in Active HDL Difference Between Assembly And Vhdl Using vhdl affords the user concurrent system descriptions. There is a fundamental difference between c. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. When learning fpga design, there are two languages to. Difference Between Assembly And Vhdl.

From www.startertutorials.com

Introduction to C++ My Blog Difference Between Assembly And Vhdl They are called hdls, or hardware. The ease of learning verilog or vhdl depends on the individual's background and preferences. For the first part of your question, about the motivations of using one or the other: When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl. Difference Between Assembly And Vhdl.

From pediaa.com

What is the Difference Between Verilog and VHDL Difference Between Assembly And Vhdl Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. Assembly languages allow you type instructions from. Difference Between Assembly And Vhdl.

From pediaa.com

What is the Difference Between Verilog and VHDL Difference Between Assembly And Vhdl Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. The ease of learning verilog. Difference Between Assembly And Vhdl.

From www.scribd.com

Difference Between VHDL & Verilog PDF Vhdl Programming Language Difference Between Assembly And Vhdl For the first part of your question, about the motivations of using one or the other: When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. Verilog's syntax is similar to c, making it easier for. Difference Between Assembly And Vhdl.

From www.youtube.com

Difference between C,VHDL,and Verilog by sai jamalapurapu YouTube Difference Between Assembly And Vhdl Using vhdl affords the user concurrent system descriptions. For the first part of your question, about the motivations of using one or the other: When learning fpga design, there are two languages to choose from, verilog or vhdl. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. There. Difference Between Assembly And Vhdl.

From www.allaboutcircuits.com

Implementing a Finite State Machine in VHDL Technical Articles Difference Between Assembly And Vhdl For the first part of your question, about the motivations of using one or the other: When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. Vhdl and verilog are two prominent hardware description languages (hdls). Difference Between Assembly And Vhdl.

From www.youtube.com

Software Engineering Difference between assembly code and disassembly Difference Between Assembly And Vhdl Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. When learning fpga design, there are two languages to choose from, verilog or vhdl. For the first part of your question, about the motivations. Difference Between Assembly And Vhdl.

From www.slideserve.com

PPT A VHDL nyelv alapjai PowerPoint Presentation ID6115087 Difference Between Assembly And Vhdl For the first part of your question, about the motivations of using one or the other: Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. Using vhdl affords the user concurrent system descriptions. There is. Difference Between Assembly And Vhdl.

From usemynotes.com

8 Difference between Assembly Language and Machine Language UseMyNotes Difference Between Assembly And Vhdl Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. They are called hdls, or hardware. The ease of learning verilog or vhdl depends on the individual's background and preferences. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. When looking at verilog and vhdl. Difference Between Assembly And Vhdl.

From slideplayer.com

Introduction to VHDL for Synthesis ppt download Difference Between Assembly And Vhdl Verilog's syntax is similar to c, making it easier for those with a background in c or. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. Vhdl is a. Difference Between Assembly And Vhdl.

From www.youtube.com

VHDL difference between component and subprogram (2 Solutions!!) YouTube Difference Between Assembly And Vhdl Verilog's syntax is similar to c, making it easier for those with a background in c or. Using vhdl affords the user concurrent system descriptions. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. They are called hdls, or hardware. For the first part of your question, about the motivations. Difference Between Assembly And Vhdl.

From pediaa.com

What is the Difference Between Namespace and Assembly Difference Between Assembly And Vhdl When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. They are called hdls, or hardware. There. Difference Between Assembly And Vhdl.

From www.congress-intercultural.eu

Hdl And Vhdl Difference UK Shop www.congressintercultural.eu Difference Between Assembly And Vhdl The ease of learning verilog or vhdl depends on the individual's background and preferences. Using vhdl affords the user concurrent system descriptions. For the first part of your question, about the motivations of using one or the other: Verilog's syntax is similar to c, making it easier for those with a background in c or. When learning fpga design, there. Difference Between Assembly And Vhdl.

From www.slideserve.com

PPT Introduction to Verilog HDL PowerPoint Presentation, free Difference Between Assembly And Vhdl They are called hdls, or hardware. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. Verilog's syntax is similar to c, making it easier for those with a background in c or. When. Difference Between Assembly And Vhdl.

From www.youtube.com

Types of Programming Languages Machine, Assembly and High Level YouTube Difference Between Assembly And Vhdl There is a fundamental difference between c. Verilog's syntax is similar to c, making it easier for those with a background in c or. They are called hdls, or hardware. For the first part of your question, about the motivations of using one or the other: When learning fpga design, there are two languages to choose from, verilog or vhdl.. Difference Between Assembly And Vhdl.

From mavink.com

Vhdl Conversion Chart Difference Between Assembly And Vhdl The ease of learning verilog or vhdl depends on the individual's background and preferences. For the first part of your question, about the motivations of using one or the other: Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. When looking at verilog and vhdl code at the. Difference Between Assembly And Vhdl.

From resources.pcb.cadence.com

Hardware Description Languages VHDL vs Verilog, and Their Functional Uses Difference Between Assembly And Vhdl Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. When learning fpga design, there are two languages to choose from, verilog or vhdl. There is a fundamental difference between c. Verilog's syntax is similar to c, making it easier for those with a background in c or. When looking at. Difference Between Assembly And Vhdl.

From www.youtube.com

Introduction to VHDL Part 2 Structural Modeling YouTube Difference Between Assembly And Vhdl Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. Using vhdl affords the user concurrent system descriptions. When learning fpga design, there are two languages to choose from, verilog or vhdl. They are. Difference Between Assembly And Vhdl.

From www.coursehero.com

[Solved] Explain the difference between these two VHDL statements and Difference Between Assembly And Vhdl They are called hdls, or hardware. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of digital systems,. The ease of learning verilog or vhdl depends on the individual's background and preferences.. Difference Between Assembly And Vhdl.

From slideplayer.com

VHDL Programming (08 Marks) ppt download Difference Between Assembly And Vhdl When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. Using vhdl affords the user. Difference Between Assembly And Vhdl.

From slideplayer.com

VHDL 1. ver.7a VHDL1 INTRODUCTION TO VHDL (VERYHIGHSPEEDINTEGRATED Difference Between Assembly And Vhdl They are called hdls, or hardware. Assembly languages allow you type instructions from your cpu's instruction set in plain text, use labels and such, and describe the. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the. Difference Between Assembly And Vhdl.

From www.slideserve.com

PPT Sequential VHDL PowerPoint Presentation, free download ID757537 Difference Between Assembly And Vhdl For the first part of your question, about the motivations of using one or the other: There is a fundamental difference between c. The ease of learning verilog or vhdl depends on the individual's background and preferences. They are called hdls, or hardware. Vhdl and verilog are two prominent hardware description languages (hdls) used in the design and verification of. Difference Between Assembly And Vhdl.

From surf-vhdl.com

VHDL Entity and Architecture Pair Difference Between Assembly And Vhdl When learning fpga design, there are two languages to choose from, verilog or vhdl. When looking at verilog and vhdl code at the same time, the most obvious difference is verilog does not have library management while vhdl does include design libraries on the top of the code. Vhdl and verilog are two prominent hardware description languages (hdls) used in. Difference Between Assembly And Vhdl.

From itecnotes.com

Electronic VHDL Concurrent statement comparison Valuable Tech Notes Difference Between Assembly And Vhdl Vhdl is a dataflow language, which means it can simultaneously consider every statement for execution. The ease of learning verilog or vhdl depends on the individual's background and preferences. For the first part of your question, about the motivations of using one or the other: Verilog's syntax is similar to c, making it easier for those with a background in. Difference Between Assembly And Vhdl.