Vhdl Use Buffer Or Inout . Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. I have found that my code is much cleaner if i use the. Therefore it is recommended to put all. They're called tri state buffers if you define a port as inout, you. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Consider the following codes :. I was wondering about the 'buffer' i/o option for entities in the vhdl language.

from vhdlwhiz.com

Consider the following codes :. Therefore it is recommended to put all. I have found that my code is much cleaner if i use the. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: They're called tri state buffers if you define a port as inout, you. I was wondering about the 'buffer' i/o option for entities in the vhdl language.

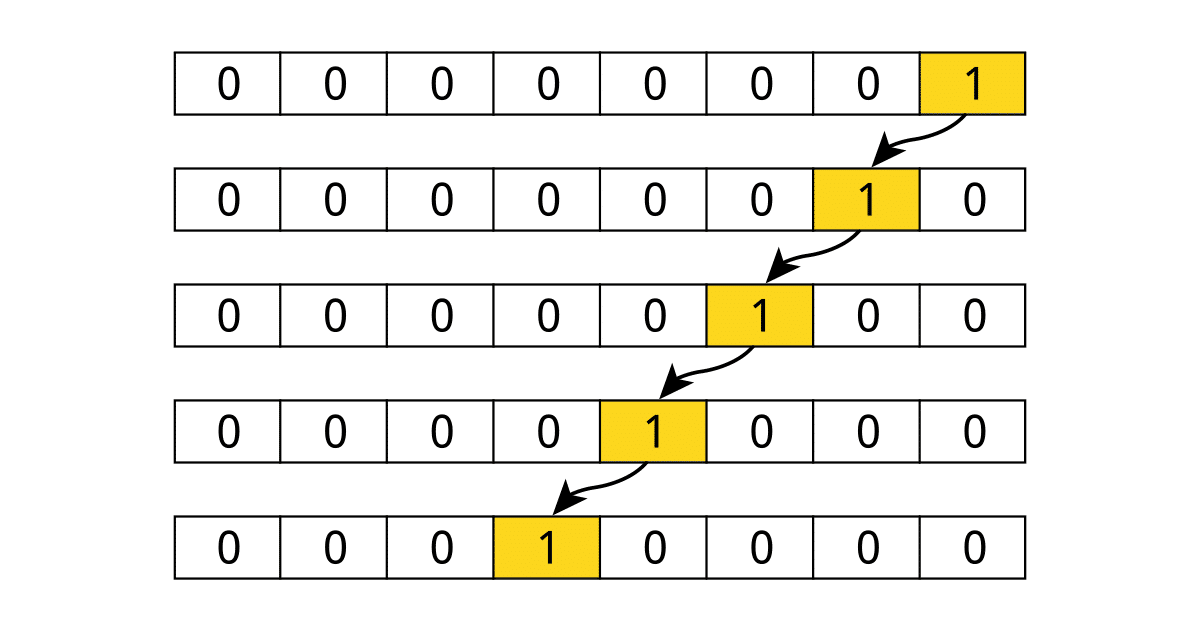

8 ways to create a shift register in VHDL VHDLwhiz

Vhdl Use Buffer Or Inout When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. They're called tri state buffers if you define a port as inout, you. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: I was wondering about the 'buffer' i/o option for entities in the vhdl language. Therefore it is recommended to put all. I have found that my code is much cleaner if i use the. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. Consider the following codes :.

From www.slideserve.com

PPT VHDL 5 FINITE STATE MACHINES (FSM) PowerPoint Presentation, free Vhdl Use Buffer Or Inout They're called tri state buffers if you define a port as inout, you. I have found that my code is much cleaner if i use the. Therefore it is recommended to put all. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. I was wondering about the 'buffer' i/o option for entities in the vhdl language. When i implement a clock. Vhdl Use Buffer Or Inout.

From www.slideserve.com

PPT Introduction to VHDL for Synthesis PowerPoint Presentation, free Vhdl Use Buffer Or Inout The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Therefore it is recommended to put all. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. Consider the following codes :. They're called tri state buffers if you define a. Vhdl Use Buffer Or Inout.

From vhdlwhiz.com

8 ways to create a shift register in VHDL VHDLwhiz Vhdl Use Buffer Or Inout I was wondering about the 'buffer' i/o option for entities in the vhdl language. They're called tri state buffers if you define a port as inout, you. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. Therefore it is recommended to put all. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: I. Vhdl Use Buffer Or Inout.

From www.youtube.com

Using Buffer Ports in VHDL? YouTube Vhdl Use Buffer Or Inout I was wondering about the 'buffer' i/o option for entities in the vhdl language. Consider the following codes :. They're called tri state buffers if you define a port as inout, you. I have found that my code is much cleaner if i use the. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. When i implement a clock divider, i. Vhdl Use Buffer Or Inout.

From susycursos.com

tri state buffer Susana Canel. Curso de VHDL Vhdl Use Buffer Or Inout When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. Consider the following codes :. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. They're called tri state buffers if you define a port as inout, you. I have found that my code is much cleaner if i use. Vhdl Use Buffer Or Inout.

From startingelectronics.org

VHDL Implementing Inverters and Buffers in a CPLD VHDL Language Vhdl Use Buffer Or Inout Therefore it is recommended to put all. I was wondering about the 'buffer' i/o option for entities in the vhdl language. Consider the following codes :. They're called tri state buffers if you define a port as inout, you. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: When i implement a. Vhdl Use Buffer Or Inout.

From mavink.com

Vhdl Conversion Chart Vhdl Use Buffer Or Inout I was wondering about the 'buffer' i/o option for entities in the vhdl language. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a. Vhdl Use Buffer Or Inout.

From slideplayer.com

VHDL 1. ver.7a VHDL1 INTRODUCTION TO VHDL (VERYHIGHSPEEDINTEGRATED Vhdl Use Buffer Or Inout Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. Therefore it is recommended to put all. They're called tri state buffers if you define a port as inout, you. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: I was wondering about the 'buffer' i/o option for entities in the vhdl language. I. Vhdl Use Buffer Or Inout.

From www.semanticscholar.org

Automatic code generation for embedded systems From UML specifications Vhdl Use Buffer Or Inout The following is a simplified example (assume all signals are std_logic) of the situation that bit me: They're called tri state buffers if you define a port as inout, you. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. Consider the following codes :. When i implement a clock divider, i often wonder whether i shold use a buffer or a. Vhdl Use Buffer Or Inout.

From www.youtube.com

Electronics VHDL 'buffer' vs. 'out' YouTube Vhdl Use Buffer Or Inout When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. They're called tri state buffers if you define a port as inout, you. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Consider the following codes :. Use 'buffer' or. Vhdl Use Buffer Or Inout.

From allaboutfpga.com

VHDL 4 to 1 MUX (Multiplexer) Vhdl Use Buffer Or Inout I was wondering about the 'buffer' i/o option for entities in the vhdl language. Consider the following codes :. I have found that my code is much cleaner if i use the. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. Therefore it is. Vhdl Use Buffer Or Inout.

From www.researchgate.net

Block RAM with Data Reuse Input buffer using block RAM organized as a Vhdl Use Buffer Or Inout Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. Consider the following codes :. Therefore it is recommended to put all. I was wondering about the 'buffer' i/o option for entities in the vhdl language. I have found that my code is much cleaner if i use the. When i implement a clock divider, i often wonder whether i shold use. Vhdl Use Buffer Or Inout.

From vhdlwhiz.com

Using variables for registers or memory in VHDL VHDLwhiz Vhdl Use Buffer Or Inout They're called tri state buffers if you define a port as inout, you. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. I was wondering about the 'buffer' i/o option for entities in the vhdl language. Therefore it is recommended to put all. Consider. Vhdl Use Buffer Or Inout.

From dokumen.tips

(PDF) Introduction to VHDLAn attribute is data that are attached to Vhdl Use Buffer Or Inout The following is a simplified example (assume all signals are std_logic) of the situation that bit me: I was wondering about the 'buffer' i/o option for entities in the vhdl language. Consider the following codes :. I have found that my code is much cleaner if i use the. They're called tri state buffers if you define a port as. Vhdl Use Buffer Or Inout.

From www.pldworld.com

VHDL 입문 Vhdl Use Buffer Or Inout Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. They're called tri state buffers if you define a port as inout, you. Therefore it is recommended to put all. I have found that my code is much cleaner if i use the. I was wondering about the 'buffer' i/o option for entities in the vhdl language. The following is a simplified. Vhdl Use Buffer Or Inout.

From www.engineersgarage.com

VHDL Tutorial 4 design, simulate and verify all digital GATE (AND Vhdl Use Buffer Or Inout They're called tri state buffers if you define a port as inout, you. Therefore it is recommended to put all. Consider the following codes :. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. I was wondering about the 'buffer' i/o option for entities in the vhdl language. I have found that my code is much cleaner if i use the.. Vhdl Use Buffer Or Inout.

From webelektronika.com

Buffer készítése VHDL nyelven Vhdl Use Buffer Or Inout I have found that my code is much cleaner if i use the. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Consider the following codes :. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. I was wondering about the 'buffer' i/o option for entities in the vhdl language. They're called tri. Vhdl Use Buffer Or Inout.

From www.slideserve.com

PPT VHDL and Sequential circuit Synthesis PowerPoint Presentation Vhdl Use Buffer Or Inout They're called tri state buffers if you define a port as inout, you. Consider the following codes :. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. I have found that my code is much cleaner if i use the. Therefore it is recommended. Vhdl Use Buffer Or Inout.

From www.youtube.com

Electronics VHDL how to use inout as inout and as normal out? (3 Vhdl Use Buffer Or Inout Consider the following codes :. I have found that my code is much cleaner if i use the. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: I was wondering about the 'buffer' i/o option for entities in the vhdl language. Therefore it is recommended to put all. When i implement a. Vhdl Use Buffer Or Inout.

From link.springer.com

VHDL (Part 1) SpringerLink Vhdl Use Buffer Or Inout When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. Therefore it is recommended to put all. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: They're called tri state buffers if you define a port as inout, you. I. Vhdl Use Buffer Or Inout.

From www.researchgate.net

Instances of VHDL gate family a) 2input AND gate, and b) 3input OR Vhdl Use Buffer Or Inout I have found that my code is much cleaner if i use the. They're called tri state buffers if you define a port as inout, you. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: I was wondering about the 'buffer' i/o option for entities in the vhdl language. Therefore it is. Vhdl Use Buffer Or Inout.

From itecnotes.com

Electronic How to use IO Buffer with defined location in VHDL Vhdl Use Buffer Or Inout I have found that my code is much cleaner if i use the. Therefore it is recommended to put all. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. I was wondering about the 'buffer' i/o option for entities in the vhdl language. The following is a. Vhdl Use Buffer Or Inout.

From slideplayer.com

VHDL 1. ver.7a VHDL1 INTRODUCTION TO VHDL (VERYHIGHSPEEDINTEGRATED Vhdl Use Buffer Or Inout They're called tri state buffers if you define a port as inout, you. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. I was wondering about the 'buffer' i/o option for entities in the vhdl language. Consider the following codes :. The following is a simplified example. Vhdl Use Buffer Or Inout.

From www.semanticscholar.org

Figure 2 from VHDLbased Hardware Design and Simulation of Input Buffer Vhdl Use Buffer Or Inout Therefore it is recommended to put all. I have found that my code is much cleaner if i use the. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. Consider the following codes :. I was wondering about the. Vhdl Use Buffer Or Inout.

From www.engineersgarage.com

VHDL Tutorial 1 Introduction to VHDL Vhdl Use Buffer Or Inout Consider the following codes :. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. I was wondering about the 'buffer' i/o option for entities in the vhdl language. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: They're called tri state buffers if you define a port as inout, you. I have found. Vhdl Use Buffer Or Inout.

From slideplayer.com

VHDL 1. ver.7a VHDL1 INTRODUCTION TO VHDL (VERYHIGHSPEEDINTEGRATED Vhdl Use Buffer Or Inout I was wondering about the 'buffer' i/o option for entities in the vhdl language. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. Consider the following codes :. I have. Vhdl Use Buffer Or Inout.

From www.engineersgarage.com

VHDL Tutorial 5 Design, simulate and verify NAND, NOR, XOR and XNOR Vhdl Use Buffer Or Inout When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. I have found that my code is much cleaner if i use the. Therefore it is recommended to put all. Consider the following codes :. They're called tri state buffers if you define a port as inout, you.. Vhdl Use Buffer Or Inout.

From stackoverflow.com

vhdl clock input to output as a finite state machine Stack Overflow Vhdl Use Buffer Or Inout I have found that my code is much cleaner if i use the. Consider the following codes :. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. They're called tri state buffers if you define a port as inout, you. Therefore it is recommended to put all. The following is a simplified example (assume all signals are std_logic) of the situation. Vhdl Use Buffer Or Inout.

From slidetodoc.com

VHDL 4 ver 7 a VHDL 4 Building Vhdl Use Buffer Or Inout Consider the following codes :. I was wondering about the 'buffer' i/o option for entities in the vhdl language. They're called tri state buffers if you define a port as inout, you. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. The following is a simplified example (assume all signals are std_logic) of the situation that bit me: When i implement. Vhdl Use Buffer Or Inout.

From www.youtube.com

How to create a signal vector in VHDL std_logic_vector YouTube Vhdl Use Buffer Or Inout When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. I have found that my code is much cleaner if i use the. Consider the following codes :. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. They're called tri state buffers if you define a port as inout,. Vhdl Use Buffer Or Inout.

From www.fatalerrors.org

VHDL programming final review Vhdl Use Buffer Or Inout When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. I have found that my code is much cleaner if i use the. I was wondering about the 'buffer' i/o option for entities in the vhdl language. Therefore it is recommended to put all. Consider the following codes. Vhdl Use Buffer Or Inout.

From www.youtube.com

Bidirectional ports inout port in VHDL and Verilog HDL YouTube Vhdl Use Buffer Or Inout When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. Therefore it is recommended to put all. I have found that my code is much cleaner if i use the. I was wondering about the 'buffer' i/o option for entities. Vhdl Use Buffer Or Inout.

From www.allaboutcircuits.com

If Statements and Latch Inference in VHDL Technical Articles Vhdl Use Buffer Or Inout I was wondering about the 'buffer' i/o option for entities in the vhdl language. Consider the following codes :. Therefore it is recommended to put all. They're called tri state buffers if you define a port as inout, you. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. When i implement a clock divider, i often wonder whether i shold use. Vhdl Use Buffer Or Inout.

From vhdlwhiz.com

How to create a ring buffer FIFO in VHDL VHDLwhiz Vhdl Use Buffer Or Inout Consider the following codes :. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. When i implement a clock divider, i often wonder whether i shold use a buffer or a regular output with a signal. I have found that my code is much cleaner if i use the. Therefore it is recommended to put all. The following is a simplified. Vhdl Use Buffer Or Inout.

From vhdl4all.blogspot.com

VHDL vs VERILOG Tristate Buffer ( VHDL ) with Test Bench Vhdl Use Buffer Or Inout The following is a simplified example (assume all signals are std_logic) of the situation that bit me: Therefore it is recommended to put all. Consider the following codes :. I was wondering about the 'buffer' i/o option for entities in the vhdl language. Use 'buffer' or 'inout' [/system_wrapper.vhd:67] but, what's wrong. When i implement a clock divider, i often wonder. Vhdl Use Buffer Or Inout.