System Verilog Clock Generator . in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. 1) convert first assign into initial begin clk = 0; example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: did you know that if else, case blocks can also be used to implement a clock. change the duty cycle of the clock to 60/40 (2ns high/3ns low). if you want to model a clock you can: to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. Put the clock generator in a module with one.

from www.chegg.com

Put the clock generator in a module with one. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. did you know that if else, case blocks can also be used to implement a clock. to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. if you want to model a clock you can: change the duty cycle of the clock to 60/40 (2ns high/3ns low). learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: 1) convert first assign into initial begin clk = 0; in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs.

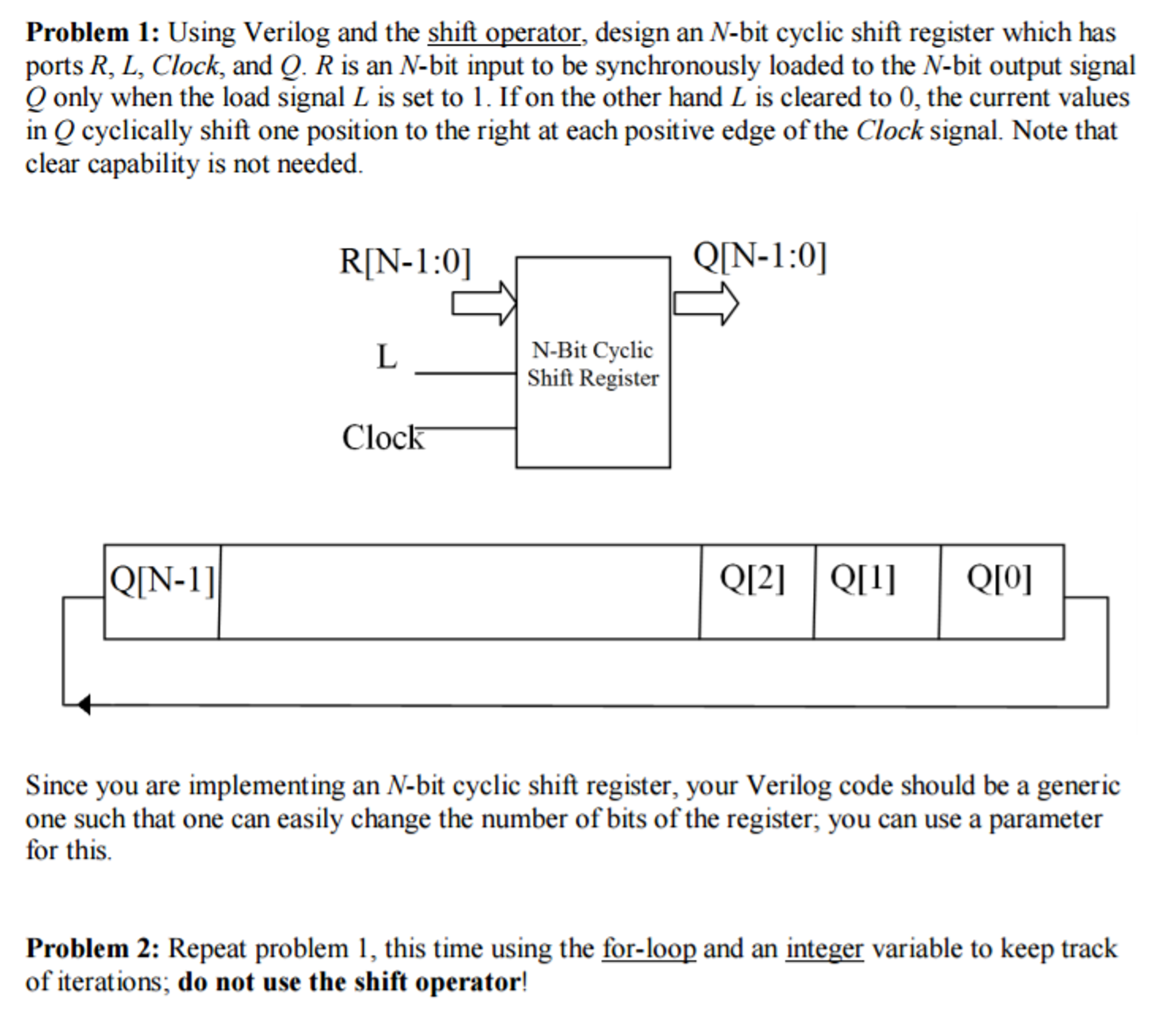

Using Verilog and the shift operator, design an Nbit

System Verilog Clock Generator 1) convert first assign into initial begin clk = 0; learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. Put the clock generator in a module with one. did you know that if else, case blocks can also be used to implement a clock. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: if you want to model a clock you can: change the duty cycle of the clock to 60/40 (2ns high/3ns low). in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. 1) convert first assign into initial begin clk = 0; to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs.

From exojsfvro.blob.core.windows.net

Generating Clock In Verilog at John Saunders blog System Verilog Clock Generator Put the clock generator in a module with one. to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. if you want to model a clock you can: learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. change the duty cycle of the clock. System Verilog Clock Generator.

From www.researchgate.net

Highlevel block diagram showing functional hierarchy of Verilog System Verilog Clock Generator example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: change the duty cycle of the clock to 60/40 (2ns high/3ns low). Put the clock generator in a module with one. if you want to model a clock you can: did you know that if else, case blocks. System Verilog Clock Generator.

From www.youtube.com

Verilog Code of Clock Generator with TB to generate CLK with Varying System Verilog Clock Generator in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. did you know that if else, case blocks can also be used to implement a clock. change the duty cycle of the clock to 60/40 (2ns high/3ns low). clocking blocks have been introduced in systemverilog. System Verilog Clock Generator.

From www.youtube.com

D Flip Flop Verilog Code and Simulation YouTube System Verilog Clock Generator Put the clock generator in a module with one. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. did you know that if else, case blocks can also be used to implement a clock. to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. learn. System Verilog Clock Generator.

From vir-us.tistory.com

[Verilog] Clock generator System Verilog Clock Generator example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Put the clock generator in a module with one. if you want to model a clock you can:. System Verilog Clock Generator.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential System Verilog Clock Generator learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. 1) convert first assign into initial begin clk = 0; did you know that if else, case blocks. System Verilog Clock Generator.

From slideplayer.com

332437 Lecture 9 Verilog Example ppt download System Verilog Clock Generator in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. change the duty cycle of the clock to 60/40 (2ns high/3ns low). did you know that if else, case blocks can also be used to implement a clock. to achieve an 875mhz clock, you need. System Verilog Clock Generator.

From www.slideserve.com

PPT Verilog Function, Task PowerPoint Presentation, free download System Verilog Clock Generator if you want to model a clock you can: 1) convert first assign into initial begin clk = 0; change the duty cycle of the clock to 60/40 (2ns high/3ns low). to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. Put the clock generator in a module with one. example verilog code. System Verilog Clock Generator.

From www.youtube.com

Clock divider by 3 with duty cycle 50 using Verilog YouTube System Verilog Clock Generator in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. change the duty cycle of the clock to 60/40 (2ns high/3ns low). if you want to model a clock you can: Put the clock generator in a module with one. did you know that if. System Verilog Clock Generator.

From www.allaboutcircuits.com

Creating Finite State Machines in Verilog Technical Articles System Verilog Clock Generator if you want to model a clock you can: example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Put the clock generator in a module with one.. System Verilog Clock Generator.

From fercow.weebly.com

Clock divider mux verilog fercow System Verilog Clock Generator 1) convert first assign into initial begin clk = 0; learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. did you know that if else, case blocks can also be used to implement a clock. change the duty cycle of the clock to 60/40 (2ns high/3ns low). . System Verilog Clock Generator.

From www.electronicsforu.com

Software Project Clock Generator Using Verilog Modelsim System Verilog Clock Generator change the duty cycle of the clock to 60/40 (2ns high/3ns low). Put the clock generator in a module with one. 1) convert first assign into initial begin clk = 0; example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: did you know that if else, case blocks. System Verilog Clock Generator.

From www.researchgate.net

Figure A5. VerilogA code of the clock amplitudebased control System Verilog Clock Generator if you want to model a clock you can: did you know that if else, case blocks can also be used to implement a clock. Put the clock generator in a module with one. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. change the duty cycle of. System Verilog Clock Generator.

From hxeuvxfpl.blob.core.windows.net

How To Use Clock In Systemverilog at Rhonda Ratcliffe blog System Verilog Clock Generator 1) convert first assign into initial begin clk = 0; to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. change the duty cycle of the clock to 60/40 (2ns high/3ns low). learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. example verilog code. System Verilog Clock Generator.

From www.chegg.com

Solved Type up Verilog Verilog program use delay to System Verilog Clock Generator in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. if you want to model a clock you can: example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: learn how to create a clock generator module. System Verilog Clock Generator.

From www.youtube.com

25 Verilog Clock Divider YouTube System Verilog Clock Generator in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. did you know that if else, case blocks can also be used to implement a clock. learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. clocking. System Verilog Clock Generator.

From medium.com

System Verilog Tutorial for Beginners by Maven Silicon Medium System Verilog Clock Generator if you want to model a clock you can: Put the clock generator in a module with one. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: did you know. System Verilog Clock Generator.

From www.docsity.com

Generating a ClockVerilog HDL and FPGAsLecture Slides Docsity System Verilog Clock Generator to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. did you know that if else, case blocks can also be used to implement a clock. change the duty cycle of the clock to 60/40 (2ns. System Verilog Clock Generator.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch System Verilog Clock Generator change the duty cycle of the clock to 60/40 (2ns high/3ns low). learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. did you know that if. System Verilog Clock Generator.

From miscircuitos.com

Clock Generator in a FPGA Full code System Verilog Clock Generator 1) convert first assign into initial begin clk = 0; example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: Put the clock generator in a module with one. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. change the duty. System Verilog Clock Generator.

From slideplayer.com

332437 Lecture 9 Verilog Example ppt download System Verilog Clock Generator in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. 1) convert first assign into initial begin clk = 0; did you know that if else, case blocks can also be used to implement a clock. to achieve an 875mhz clock, you need 1.142857143ns, equal to. System Verilog Clock Generator.

From www.softpedia.com

Verilog Testbench Generator 01 JAN 2016 Download, Screenshots System Verilog Clock Generator example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs.. System Verilog Clock Generator.

From exojsfvro.blob.core.windows.net

Generating Clock In Verilog at John Saunders blog System Verilog Clock Generator example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. if you want to model a clock you can: to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps. System Verilog Clock Generator.

From www.tina.com

SystemVerilog Simulation System Verilog Clock Generator did you know that if else, case blocks can also be used to implement a clock. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: Put the clock generator in a. System Verilog Clock Generator.

From github.com

GitHub ayushagarwal0502/CDCSynchronizerSystemVerilog System Verilog Clock Generator in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: 1) convert first assign into initial begin clk = 0; did you know that if else, case blocks. System Verilog Clock Generator.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale System Verilog Clock Generator change the duty cycle of the clock to 60/40 (2ns high/3ns low). to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. did you know that if else, case blocks can also be used to implement a clock. learn how to create a clock generator module in verilog with parameters for frequency, duty. System Verilog Clock Generator.

From www.chegg.com

Solved Create a clock generator module with Verilog which System Verilog Clock Generator to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. change the duty cycle of the clock to 60/40 (2ns high/3ns low). Put the clock generator in a module with one. in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. clocking. System Verilog Clock Generator.

From www.youtube.com

Verilog Tutorial 02 Clock Divider YouTube System Verilog Clock Generator learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. example verilog code to generate 100 hz from 50 mhz with a 50% duty cycle using an accumulator: change the duty cycle of the clock to 60/40 (2ns high/3ns low). to achieve an 875mhz clock, you need 1.142857143ns,. System Verilog Clock Generator.

From poe.com

What is the method for generating a 100MHz clock in Verilog? Poe System Verilog Clock Generator if you want to model a clock you can: did you know that if else, case blocks can also be used to implement a clock. Put the clock generator in a module with one. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. in verilog, a clock generator. System Verilog Clock Generator.

From www.electronicsforu.com

Software Project Clock Generator Using Verilog Modelsim System Verilog Clock Generator if you want to model a clock you can: clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. did you know that if else, case blocks can. System Verilog Clock Generator.

From www.youtube.com

Course Systemverilog Verification 2 L4.1 Clocking Blocks in System Verilog Clock Generator change the duty cycle of the clock to 60/40 (2ns high/3ns low). did you know that if else, case blocks can also be used to implement a clock. learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. to achieve an 875mhz clock, you need 1.142857143ns, equal to. System Verilog Clock Generator.

From www.chegg.com

Using Verilog and the shift operator, design an Nbit System Verilog Clock Generator did you know that if else, case blocks can also be used to implement a clock. if you want to model a clock you can: 1) convert first assign into initial begin clk = 0; learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. example verilog code. System Verilog Clock Generator.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID687888 System Verilog Clock Generator change the duty cycle of the clock to 60/40 (2ns high/3ns low). in verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. to achieve an 875mhz clock,. System Verilog Clock Generator.

From www.youtube.com

21 Verilog Clock Generator YouTube System Verilog Clock Generator did you know that if else, case blocks can also be used to implement a clock. clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. change the duty cycle of the clock to 60/40 (2ns high/3ns low). learn how to create a clock generator module in verilog with. System Verilog Clock Generator.

From www.youtube.com

How to generate clock in Verilog HDL YouTube System Verilog Clock Generator did you know that if else, case blocks can also be used to implement a clock. learn how to create a clock generator module in verilog with parameters for frequency, duty cycle and phase. to achieve an 875mhz clock, you need 1.142857143ns, equal to 1142.857143ps and 1142857.143fs. clocking blocks have been introduced in systemverilog to address. System Verilog Clock Generator.