Clock In Verilog . Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Try moving clk=0 above the forever loop. A clocking block defined between clocking and endcocking does exactly that. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. It is a collection of signals synchronous with a particular clock and. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. Here is the verilog code. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation.

from www.chegg.com

I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. A clocking block defined between clocking and endcocking does exactly that. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Here is the verilog code. Try moving clk=0 above the forever loop. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling.

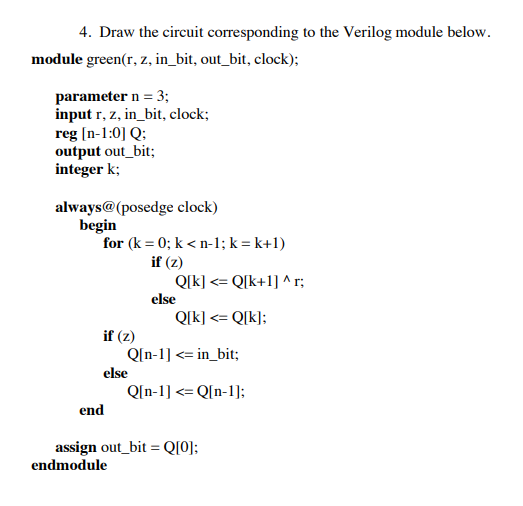

Solved 4. Draw the circuit corresponding to the Verilog

Clock In Verilog Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. Here is the verilog code. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Try moving clk=0 above the forever loop. A clocking block defined between clocking and endcocking does exactly that. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. It is a collection of signals synchronous with a particular clock and. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift.

From picklasopa911.weebly.com

Clock divider mux verilog picklasopa Clock In Verilog To specify synchronization scheme and timing requirements for an interface, a clocking block is used. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. It is a collection of. Clock In Verilog.

From www.youtube.com

25 Verilog Clock Divider YouTube Clock In Verilog Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. A clocking block defined between clocking and endcocking does exactly that. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units,. Clock In Verilog.

From pgandhi189.blogspot.com

VLSI verification blogs Design of frequency divider using modulo Clock In Verilog Try moving clk=0 above the forever loop. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. A clocking block defined between clocking and endcocking does exactly that. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In verilog, a clock generator is a module or. Clock In Verilog.

From www.youtube.com

6 How to Generate a Slow Clock on an FPGA Board? Verilog Stepby Clock In Verilog I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. A clocking block defined between clocking and endcocking. Clock In Verilog.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Clock In Verilog To specify synchronization scheme and timing requirements for an interface, a clocking block is used. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. Here is the verilog code. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. Edit, save, simulate, synthesize. Clock In Verilog.

From exogvchsq.blob.core.windows.net

Verilog Testbench Clock Example at Albert Kellum blog Clock In Verilog Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. A clocking block defined between clocking and endcocking does exactly that. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. Try moving clk=0 above the forever loop. Here is the verilog code. It is a. Clock In Verilog.

From www.transtutors.com

(Get Answer) GR 2400HW 3 Verilog/DigitalDesign/Clocks/Counters/Mux Clock In Verilog Try moving clk=0 above the forever loop. A clocking block defined between clocking and endcocking does exactly that. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. I am. Clock In Verilog.

From hxeuvxfpl.blob.core.windows.net

How To Use Clock In Systemverilog at Rhonda Ratcliffe blog Clock In Verilog To specify synchronization scheme and timing requirements for an interface, a clocking block is used. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. A clocking block defined between clocking and endcocking does exactly that. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing. Clock In Verilog.

From www.docsity.com

Generating a ClockVerilog HDL and FPGAsLecture Slides Docsity Clock In Verilog Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. A clocking block defined between clocking and endcocking does exactly that. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. It is a collection of signals synchronous with a particular clock and. In verilog, a clock generator is. Clock In Verilog.

From vir-us.tistory.com

[Verilog] Clock generator Clock In Verilog A clocking block defined between clocking and endcocking does exactly that. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. It is a collection of signals synchronous with a particular clock and. Here is the. Clock In Verilog.

From exojsfvro.blob.core.windows.net

Generating Clock In Verilog at John Saunders blog Clock In Verilog Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. It is a collection of signals synchronous with a particular clock and. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. Clocking blocks have been introduced in systemverilog to address the problem of specifying the. Clock In Verilog.

From community.cadence.com

Clock Generation in NCVHDL & NCVERILOG Functional Verification Clock In Verilog Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Instead of toggling. Clock In Verilog.

From hetpro-store.com

Verilog Diseño de Contadores y Clocks HeTProTutoriales Clock In Verilog Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. Here is the verilog code. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. In verilog, a clock. Clock In Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID687888 Clock In Verilog Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. A clocking block defined between. Clock In Verilog.

From www.youtube.com

digital clock by verilog code on fpga de2 kit YouTube Clock In Verilog Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. Try moving clk=0 above the forever loop. It is a collection of signals synchronous with a particular clock and. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. I am trying to write. Clock In Verilog.

From www.youtube.com

Verilog Tutorial 02 Clock Divider YouTube Clock In Verilog It is a collection of signals synchronous with a particular clock and. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. A clocking block defined between clocking and endcocking does exactly that. In verilog, a clock generator is a module or block of code that produces clock signals for digital. Clock In Verilog.

From www.researchgate.net

Figure A5. VerilogA code of the clock amplitudebased control Clock In Verilog In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. It is a collection of signals synchronous with a particular clock and. Clocking blocks have been introduced in systemverilog to. Clock In Verilog.

From www.youtube.com

VGA Digital Clock in Verilog on Basys 3 FPGA Vivado YouTube Clock In Verilog Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. I am trying to write a testbench for an. Clock In Verilog.

From electronics.stackexchange.com

verilog Why must While and Forever loops be broken with a (posedge Clock In Verilog I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Learn how to create a verilog module that. Clock In Verilog.

From electrodast.weebly.com

Clock divider verilog electrodast Clock In Verilog Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. Try moving clk=0 above the forever loop. To specify synchronization scheme and timing requirements for an interface, a clocking block is used.. Clock In Verilog.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock In Verilog Here is the verilog code. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. A clocking block defined between clocking and endcocking does exactly that. It is a collection of signals synchronous with a particular clock and. I am trying. Clock In Verilog.

From www.youtube.com

How to generate clock in Verilog HDL Verilog code of clock generator Clock In Verilog Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. It is a collection of signals synchronous with a particular clock and. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. A clocking block defined between clocking and endcocking does exactly that. Try. Clock In Verilog.

From www.youtube.com

Electronics Best way to structure Verilog module to allow for Clock In Verilog Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Here is the verilog code. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. A clocking block defined between clocking and. Clock In Verilog.

From www.youtube.com

Flip Flops and Clocks with Verilog in Quartus/Terasic DE2115 YouTube Clock In Verilog Here is the verilog code. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. To specify synchronization scheme and. Clock In Verilog.

From www.numerade.com

SOLVED Type up Verilog Verilog program use delay to create a pulse Clock In Verilog I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. Try moving clk=0 above the forever loop. A clocking block defined between clocking and endcocking does exactly that. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. To specify synchronization scheme and timing. Clock In Verilog.

From github.com

GitHub prajwalgekkouga/DigitalClockinVerilog Clock In Verilog It is a collection of signals synchronous with a particular clock and. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. A clocking block defined between clocking and endcocking does exactly that. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. In verilog, a. Clock In Verilog.

From www.slideserve.com

PPT Verilog for sequential machines PowerPoint Presentation, free Clock In Verilog Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. A clocking block defined between clocking and endcocking does exactly that. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. To specify synchronization scheme and timing requirements for an interface, a clocking block is. Clock In Verilog.

From www.youtube.com

VERILOG & FPGA Project DIGITAL CLOCK WITH ALARM AND FLEXIBLE TIME Clock In Verilog Try moving clk=0 above the forever loop. To specify synchronization scheme and timing requirements for an interface, a clocking block is used. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. I am. Clock In Verilog.

From exojsfvro.blob.core.windows.net

Generating Clock In Verilog at John Saunders blog Clock In Verilog A clocking block defined between clocking and endcocking does exactly that. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. To specify synchronization scheme and timing requirements for an interface, a clocking block. Clock In Verilog.

From www.chegg.com

Solved 4. Draw the circuit corresponding to the Verilog Clock In Verilog A clocking block defined between clocking and endcocking does exactly that. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Here is the verilog code. It is a collection of signals synchronous with a particular clock and. In verilog, a clock generator is a module or block of code that produces clock signals for digital. Clock In Verilog.

From www.youtube.com

Clock divider by 3 with duty cycle 50 using Verilog YouTube Clock In Verilog Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. Instead. Clock In Verilog.

From www.pinterest.ca

Pin on FPGA projects using Verilog/ Clock In Verilog A clocking block defined between clocking and endcocking does exactly that. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. Learn how to create a verilog module that generates a clock signal with. Clock In Verilog.

From www.youtube.com

How to generate clock in Verilog HDL YouTube Clock In Verilog Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. I am trying to write a testbench for an adder/subtractor, but when it compiles, the clock does not shift. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. Try moving clk=0 above the. Clock In Verilog.

From www.youtube.com

Verilog® `timescale directive Syntax of time_unit argument YouTube Clock In Verilog In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Instead of toggling the clock every #10 you're resetting the clock to 0 every #10 units, and then toggling. Learn how to create a verilog module that generates a clock signal with adjustable frequency, duty cycle and phase. Edit,. Clock In Verilog.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential Clock In Verilog In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Clocking blocks have been introduced in systemverilog to address the problem of specifying the timing and synchronisation. A clocking block defined between clocking and endcocking does exactly that. It is a collection of signals synchronous with a particular clock. Clock In Verilog.