Maximum Clock Frequency Formula . To find the max freq, calculate the longest output path delay. I will explain why and how you can calculate the max clock frequency. Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. 2 nd section contains the basics of “maximum clock frequency”. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. 4.2.1 maximum clock in digital circuits. I will take few examples and try to. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. Tac = tclk−q (a) + tpd (z) + ts (c) = 9 ns + 4 ns + 2 ns = 15 ns. Since the tbc is the largest of the path delays, the. Since digital logic tends to be synchronous circuitry, the. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). Let us calculate the maximum and minimum clock path and data path delays: The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for.

from www.chegg.com

Tac = tclk−q (a) + tpd (z) + ts (c) = 9 ns + 4 ns + 2 ns = 15 ns. Since the tbc is the largest of the path delays, the. 4.2.1 maximum clock in digital circuits. I will take few examples and try to. 2 nd section contains the basics of “maximum clock frequency”. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal to 4/3 * 40 ns, which is.

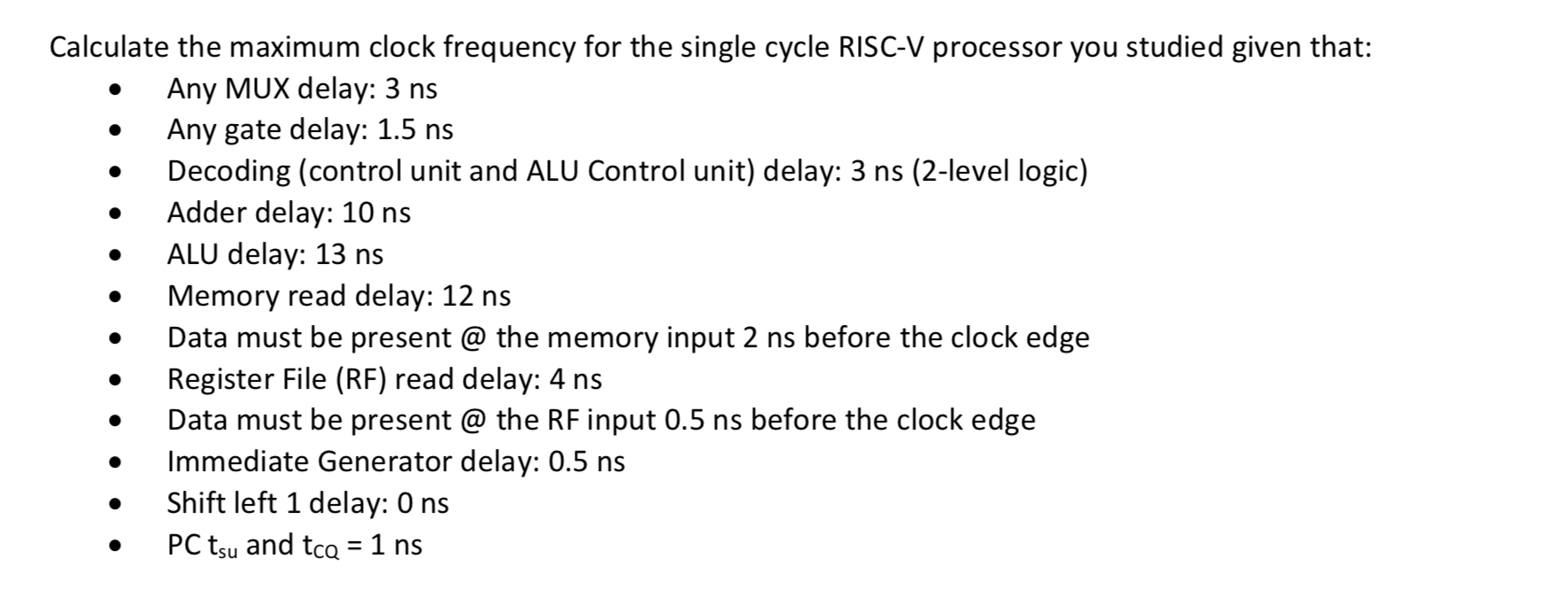

Solved Calculate the maximum clock frequency for the single

Maximum Clock Frequency Formula Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. I will explain why and how you can calculate the max clock frequency. Since digital logic tends to be synchronous circuitry, the. Since the tbc is the largest of the path delays, the. Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. 4.2.1 maximum clock in digital circuits. Let us calculate the maximum and minimum clock path and data path delays: Tac = tclk−q (a) + tpd (z) + ts (c) = 9 ns + 4 ns + 2 ns = 15 ns. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). 2 nd section contains the basics of “maximum clock frequency”. To find the max freq, calculate the longest output path delay. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal to 4/3 * 40 ns, which is. I will take few examples and try to. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns.

From www.chegg.com

Solved Evaluate the maximum clock frequency for the Maximum Clock Frequency Formula The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). The purpose. Maximum Clock Frequency Formula.

From www.researchgate.net

An illustration of clock frequency synchronization and of full clock... Download Scientific Maximum Clock Frequency Formula Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. Since the tbc is the largest of the path delays, the. Let us calculate the maximum and minimum clock path and data path delays: Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal to 4/3 *. Maximum Clock Frequency Formula.

From www.chegg.com

Solved determine the maximum clock frequency in nanoseconds. Maximum Clock Frequency Formula 2 nd section contains the basics of “maximum clock frequency”. Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. 4.2.1 maximum clock in digital circuits. The maximum clock frequency is defined a. Maximum Clock Frequency Formula.

From haipernews.com

How To Calculate Frequency Clock Haiper Maximum Clock Frequency Formula 2 nd section contains the basics of “maximum clock frequency”. Since digital logic tends to be synchronous circuitry, the. I will take few examples and try to. Since the tbc is the largest of the path delays, the. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). Maximum. Maximum Clock Frequency Formula.

From www.slideserve.com

PPT EE 466/586 VLSI Design PowerPoint Presentation, free download ID4642964 Maximum Clock Frequency Formula Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. 2 nd section contains the basics of “maximum clock frequency”. To find the max freq, calculate the longest output path delay. Tac = tclk−q (a) + tpd (z) + ts (c) = 9 ns + 4 ns + 2 ns = 15 ns. Let us. Maximum Clock Frequency Formula.

From www.slideserve.com

PPT Clock in Digital Systems PowerPoint Presentation, free download ID3878457 Maximum Clock Frequency Formula Tac = tclk−q (a) + tpd (z) + ts (c) = 9 ns + 4 ns + 2 ns = 15 ns. I will explain why and how you can calculate the max clock frequency. The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. Since the tbc is the largest of the path delays,. Maximum Clock Frequency Formula.

From www.slideserve.com

PPT STATIC TIMING ANALYSIS PowerPoint Presentation, free download ID776068 Maximum Clock Frequency Formula I will explain why and how you can calculate the max clock frequency. Tac = tclk−q (a) + tpd (z) + ts (c) = 9 ns + 4 ns + 2 ns = 15 ns. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. 2 nd section contains the basics of “maximum clock. Maximum Clock Frequency Formula.

From www.youtube.com

Electronics maximum clock frequency for a sequential circuit YouTube Maximum Clock Frequency Formula Since digital logic tends to be synchronous circuitry, the. Let us calculate the maximum and minimum clock path and data path delays: I will explain why and how you can calculate the max clock frequency. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. Computing a. Maximum Clock Frequency Formula.

From www.numerade.com

SOLVED The angular frequency related with the period of the oscillation is given by 21 0 = T 27 Maximum Clock Frequency Formula The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. To find the max freq, calculate the. Maximum Clock Frequency Formula.

From www.slideserve.com

PPT SEQUENTIAL LOGIC PowerPoint Presentation, free download ID6011398 Maximum Clock Frequency Formula Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. Since digital logic tends to be synchronous circuitry, the. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. I will explain why and how. Maximum Clock Frequency Formula.

From shotonmac.com

Top 5 how to find frequency from wavelength 2022 Maximum Clock Frequency Formula Let us calculate the maximum and minimum clock path and data path delays: Since digital logic tends to be synchronous circuitry, the. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. 2 nd section contains the basics of “maximum clock frequency”. The speed of a logic. Maximum Clock Frequency Formula.

From www.youtube.com

SETUP ANALYSIS MAXIMUM CLOCK FREQUENCY STA 4 Static Timing Analysis YouTube Maximum Clock Frequency Formula Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). 4.2.1 maximum clock in digital circuits. Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal. Maximum Clock Frequency Formula.

From www.youtube.com

Module6_Vid_23_Minimum and Maximum Clock Frequency Part 1 YouTube Maximum Clock Frequency Formula Since digital logic tends to be synchronous circuitry, the. The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. Let us calculate the maximum and minimum clock path and data path delays: Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. Minimum data path delay = 2 +. Maximum Clock Frequency Formula.

From slideplayer.com

IR CON 3to8 Decoder Never Branch Always Branch ppt download Maximum Clock Frequency Formula I will take few examples and try to. Since the tbc is the largest of the path delays, the. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). I will explain why and how you can calculate the max clock frequency. Minimum data path delay = 2 +. Maximum Clock Frequency Formula.

From www.slideserve.com

PPT Chapter 7 PowerPoint Presentation, free download ID5921428 Maximum Clock Frequency Formula Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. Since the tbc is the largest of the path delays, the. Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal to 4/3 * 40 ns, which is. Tac = tclk−q. Maximum Clock Frequency Formula.

From www.chegg.com

Solved Question 4. Maximum operating frequency and clock Maximum Clock Frequency Formula Since the tbc is the largest of the path delays, the. To find the max freq, calculate the longest output path delay. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. Let us calculate the maximum and minimum clock path and data path delays: The maximum clock. Maximum Clock Frequency Formula.

From www.chegg.com

Solved For the circuit given below calculate. Maximum clock Maximum Clock Frequency Formula The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. Since the tbc is the largest of the path delays, the. Let us calculate the maximum and minimum clock path and data path delays: Computing a rigorous maximum clock frequency, we would first determine that the minimum. Maximum Clock Frequency Formula.

From www.chegg.com

Solved 5) What is the maximum clock frequency the following Maximum Clock Frequency Formula The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal to 4/3 * 40 ns, which is. To find the max freq, calculate the longest output path delay. Maximum data path delay = 3 + 12 + 3. Maximum Clock Frequency Formula.

From www.chegg.com

Solved Determine the maximum frequency of the clock signal Maximum Clock Frequency Formula To find the max freq, calculate the longest output path delay. The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. 2 nd section contains the basics of “maximum clock frequency”. I. Maximum Clock Frequency Formula.

From www.chegg.com

Solved For the circuit given below calculate. Maximum clock Maximum Clock Frequency Formula Since digital logic tends to be synchronous circuitry, the. Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for. I will take few examples and try to. To find the max freq,. Maximum Clock Frequency Formula.

From www.chegg.com

Solved Q. Determining the Max. Clock Frequency the Maximum Clock Frequency Formula I will take few examples and try to. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. Let us calculate the maximum and minimum clock path and data path delays: Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal. Maximum Clock Frequency Formula.

From www.slideserve.com

PPT Instructor Justin Hsia PowerPoint Presentation, free download ID2454372 Maximum Clock Frequency Formula Since digital logic tends to be synchronous circuitry, the. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). The purpose of this chapter is to find. Maximum Clock Frequency Formula.

From www.researchgate.net

Cycle count and maximum clock frequency for SPM d and Hybrid 1 (image... Download Table Maximum Clock Frequency Formula Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. Since the tbc is the largest of the path delays, the. I will explain why and how you can calculate the max clock frequency. 2 nd section contains the basics. Maximum Clock Frequency Formula.

From www.chegg.com

3. For the circuit below (40pts) a. Draw the timing Maximum Clock Frequency Formula Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. Since digital logic tends to be synchronous circuitry, the. The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on. Maximum Clock Frequency Formula.

From www.chegg.com

Solved In lecture we examined the 4bit up counter Maximum Clock Frequency Formula 4.2.1 maximum clock in digital circuits. 2 nd section contains the basics of “maximum clock frequency”. Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. I will explain why and how you can calculate the max clock frequency.. Maximum Clock Frequency Formula.

From www.youtube.com

Maximum Clock Frequency Example on Max Clock Frequency vlsipp YouTube Maximum Clock Frequency Formula Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal to 4/3 * 40 ns, which is. The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). I will take few examples and try to. Since digital logic tends to be synchronous. Maximum Clock Frequency Formula.

From www.slideserve.com

PPT Sequential Circuit Timing PowerPoint Presentation, free download ID515323 Maximum Clock Frequency Formula To find the max freq, calculate the longest output path delay. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. Minimum data path delay = 2 + 10 +2 + 7 + 2 = 23ns. Tac = tclk−q (a) + tpd (z) + ts (c) = 9 ns + 4 ns + 2. Maximum Clock Frequency Formula.

From www.chegg.com

Solved Calculate the maximum clock frequency for the single Maximum Clock Frequency Formula Let us calculate the maximum and minimum clock path and data path delays: I will explain why and how you can calculate the max clock frequency. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. I will take few examples and try to. Tac = tclk−q (a) + tpd (z) + ts (c). Maximum Clock Frequency Formula.

From www.youtube.com

Calculation of fundamental period and fundamental frequency of a signal Lecture 3 YouTube Maximum Clock Frequency Formula The speed of a logic block is usually measured in terms of maximum clock frequency (this applies only to synchronous circuits). Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. The purpose of this chapter is to find the maximum clock frequency and adjusted setup and hold times based on propagation delays for.. Maximum Clock Frequency Formula.

From www.slideserve.com

PPT CPE/EE 422/522 Advanced Logic Design L03 PowerPoint Presentation ID883001 Maximum Clock Frequency Formula I will take few examples and try to. 2 nd section contains the basics of “maximum clock frequency”. Let us calculate the maximum and minimum clock path and data path delays: I will explain why and how you can calculate the max clock frequency. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns. Maximum Clock Frequency Formula.

From www.youtube.com

GATE 1990 ECE Maximum clock frequency of Modulo 16 ripple counter YouTube Maximum Clock Frequency Formula The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. 2 nd section contains the basics of “maximum clock frequency”. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. Computing a rigorous maximum clock frequency, we would first determine that the minimum clock period is equal to 4/3. Maximum Clock Frequency Formula.

From www.youtube.com

Minimum Clock Period Maximum Clock Frequency Possible Hold Time Setup Time Clock Maximum Clock Frequency Formula Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. Since digital logic tends to be synchronous circuitry, the. 4.2.1 maximum clock in digital circuits. Tac = tclk−q (a) + tpd (z) + ts (c) = 9 ns + 4 ns + 2 ns = 15 ns. 2. Maximum Clock Frequency Formula.

From www.chegg.com

Solved (b) What is the maximum possible clock frequency with Maximum Clock Frequency Formula Let us calculate the maximum and minimum clock path and data path delays: The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. Since digital logic tends to be synchronous circuitry, the. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. Tac = tclk−q (a) + tpd (z). Maximum Clock Frequency Formula.

From www.slideserve.com

PPT SEQUENTIAL LOGIC PowerPoint Presentation, free download ID335260 Maximum Clock Frequency Formula The maximum clock frequency is defined a $$\frac {1} {t_c}$$ clock delivery and clock skew. Maximum data path delay = 3 + 12 + 3 + 10 + 3 = 31ns. Since the tbc is the largest of the path delays, the. Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2. Maximum Clock Frequency Formula.

From studylib.net

Statistics Maximum clock frequency Maximum Clock Frequency Formula Tbc = tclk−q (b) + tpd (z) + ts (c) = 10 ns + 4 ns + 2 ns = 16 ns. 2 nd section contains the basics of “maximum clock frequency”. I will take few examples and try to. Since the tbc is the largest of the path delays, the. Maximum data path delay = 3 + 12 +. Maximum Clock Frequency Formula.