Digital Glitch Filter Verilog . The proposed solution is based. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. Glitches frequently occur on lines carrying signals from sources such as rf receivers. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. (i found this solution at. But at cdc, or asynchronous design we must verify that the design is glitch free. A repo of basic verilog/systemverilog modules useful in other circuits. While i understand some debouncing filters in vhdl can anyone give me. How can i implement a glitch filter ? Following lattice document describes a glitch filter on page 6.

from cadence.okstate.edu

The proposed solution is based. While i understand some debouncing filters in vhdl can anyone give me. How can i implement a glitch filter ? Glitches frequently occur on lines carrying signals from sources such as rf receivers. (i found this solution at. But at cdc, or asynchronous design we must verify that the design is glitch free. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. Following lattice document describes a glitch filter on page 6. A repo of basic verilog/systemverilog modules useful in other circuits. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low.

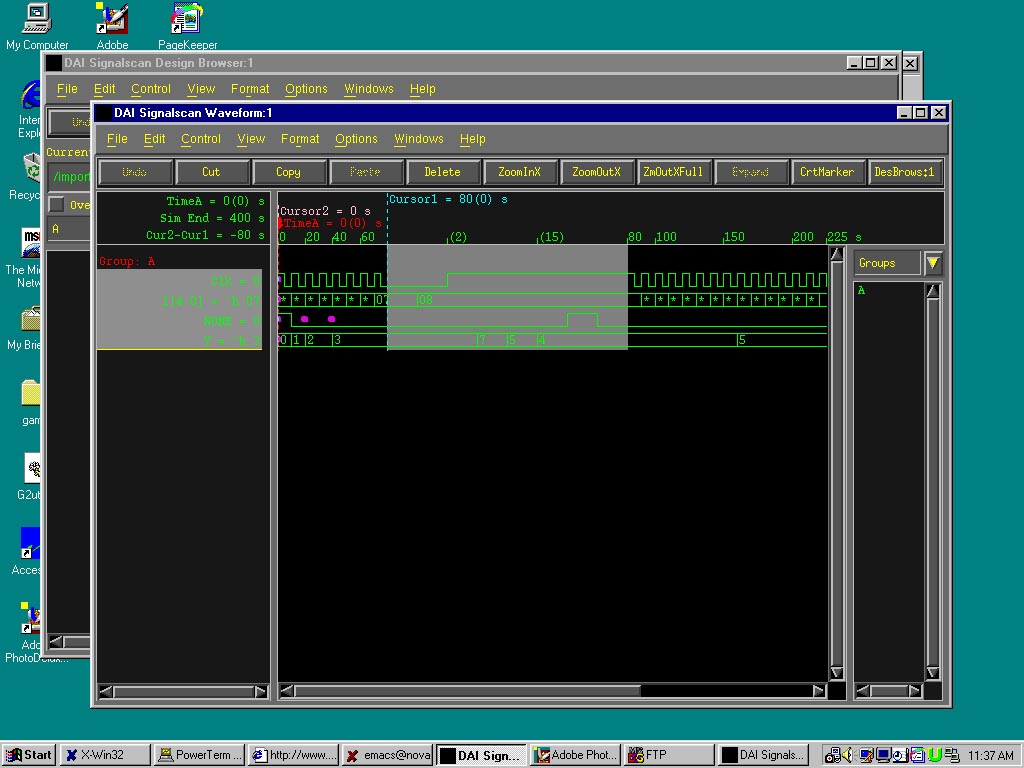

Simulation with VerilogXL

Digital Glitch Filter Verilog Glitches frequently occur on lines carrying signals from sources such as rf receivers. How can i implement a glitch filter ? But at cdc, or asynchronous design we must verify that the design is glitch free. Glitches frequently occur on lines carrying signals from sources such as rf receivers. While i understand some debouncing filters in vhdl can anyone give me. (i found this solution at. The proposed solution is based. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. Following lattice document describes a glitch filter on page 6. A repo of basic verilog/systemverilog modules useful in other circuits.

From www.solomotorcontrollers.com

How to manage Noisy Encoders or Hall sensors? How does SOLO actively Digital Glitch Filter Verilog (i found this solution at. The proposed solution is based. Following lattice document describes a glitch filter on page 6. A repo of basic verilog/systemverilog modules useful in other circuits. How can i implement a glitch filter ? But at cdc, or asynchronous design we must verify that the design is glitch free. While i understand some debouncing filters in. Digital Glitch Filter Verilog.

From www.capcut.com

How To Add Glitch Filter In Your Visuals 3 Easy Ways Digital Glitch Filter Verilog While i understand some debouncing filters in vhdl can anyone give me. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. The proposed solution is based. Glitches frequently occur on lines carrying signals from sources such as rf receivers. But at cdc, or asynchronous design we must verify that. Digital Glitch Filter Verilog.

From slideplayer.com

Verilog Digital System Design Z. Navabi, McGrawHill, ppt download Digital Glitch Filter Verilog (i found this solution at. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. The proposed solution is based. Following lattice document describes a glitch filter on page 6. A repo of basic verilog/systemverilog modules useful in other circuits. Glitches frequently occur on lines carrying signals from sources such. Digital Glitch Filter Verilog.

From uspto.report

Digital glitch filter Patent Grant Lin , et al. Feb [NXP USA, INC.] Digital Glitch Filter Verilog The proposed solution is based. How can i implement a glitch filter ? But at cdc, or asynchronous design we must verify that the design is glitch free. Following lattice document describes a glitch filter on page 6. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. (i found. Digital Glitch Filter Verilog.

From www.freepik.com

Premium AI Image Abstract background inspired by digital glitch Digital Glitch Filter Verilog Glitches frequently occur on lines carrying signals from sources such as rf receivers. A repo of basic verilog/systemverilog modules useful in other circuits. (i found this solution at. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. Following lattice document describes a glitch filter on page 6. How can. Digital Glitch Filter Verilog.

From www.google.ch

Patent US8558579 Digital glitch filter Google Patentsuche Digital Glitch Filter Verilog A repo of basic verilog/systemverilog modules useful in other circuits. How can i implement a glitch filter ? Following lattice document describes a glitch filter on page 6. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. A user asks how to use systemverilog assertion to detect glitch duration. Digital Glitch Filter Verilog.

From vdocuments.mx

NI 9326 Datasheet NI · Programmable Digital Glitch Filter The NI 9326 Digital Glitch Filter Verilog Glitches frequently occur on lines carrying signals from sources such as rf receivers. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. A repo of basic verilog/systemverilog modules useful. Digital Glitch Filter Verilog.

From www.alamy.com

Abstract background, pattern of a digital glitch Stock Photo Alamy Digital Glitch Filter Verilog The proposed solution is based. But at cdc, or asynchronous design we must verify that the design is glitch free. A repo of basic verilog/systemverilog modules useful in other circuits. (i found this solution at. While i understand some debouncing filters in vhdl can anyone give me. How can i implement a glitch filter ? Glitches frequently occur on lines. Digital Glitch Filter Verilog.

From slideplayer.com

Verilog Digital System Design Z. Navabi, McGrawHill, ppt download Digital Glitch Filter Verilog Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. Following lattice document describes a glitch filter on page 6. But at cdc, or asynchronous design we must verify that the design is glitch free. While i understand some debouncing filters in vhdl can anyone give me. A repo of. Digital Glitch Filter Verilog.

From blog.csdn.net

Verilog学习心得之一时钟无缝切换_verilog时钟源选择CSDN博客 Digital Glitch Filter Verilog A repo of basic verilog/systemverilog modules useful in other circuits. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. But at cdc, or asynchronous design we must verify that the design is glitch free. (i found this solution at. Following lattice document describes a glitch filter on page 6.. Digital Glitch Filter Verilog.

From uspto.report

Digital glitch filter Patent Grant Lin , et al. Feb [NXP USA, INC.] Digital Glitch Filter Verilog Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. While i understand some debouncing filters in vhdl can anyone give me. How can i implement a glitch filter ? A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts.. Digital Glitch Filter Verilog.

From semiengineering.com

Which Glitch Is Which? Digital Glitch Filter Verilog A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. While i understand some debouncing filters in vhdl can anyone give me. How can i implement a glitch filter ?. Digital Glitch Filter Verilog.

From community.cadence.com

Typical delay values for reset glitch filter in 28nm. Digital Digital Glitch Filter Verilog While i understand some debouncing filters in vhdl can anyone give me. (i found this solution at. A repo of basic verilog/systemverilog modules useful in other circuits. But at cdc, or asynchronous design we must verify that the design is glitch free. How can i implement a glitch filter ? The proposed solution is based. Glitches frequently occur on lines. Digital Glitch Filter Verilog.

From www.vecteezy.com

Blue cyan digital glitch footage, glitch transition 21438783 Stock Digital Glitch Filter Verilog The proposed solution is based. How can i implement a glitch filter ? While i understand some debouncing filters in vhdl can anyone give me. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. Glitches frequently occur on lines carrying signals from sources such as rf receivers. (i found. Digital Glitch Filter Verilog.

From www.slideserve.com

PPT Digital Logic issues in Embedded Systems PowerPoint Presentation Digital Glitch Filter Verilog A repo of basic verilog/systemverilog modules useful in other circuits. (i found this solution at. The proposed solution is based. Following lattice document describes a glitch filter on page 6. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. While i understand some debouncing filters in vhdl can anyone. Digital Glitch Filter Verilog.

From stock.adobe.com

Glitch effect digital noise background Stock Illustration Adobe Stock Digital Glitch Filter Verilog But at cdc, or asynchronous design we must verify that the design is glitch free. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. While i understand some debouncing filters in vhdl can anyone give me. Glitch filtering is the process of removing unwanted pulses from a digital input. Digital Glitch Filter Verilog.

From www.semanticscholar.org

Figure 2 from Voltage Glitch Filter and Detector with SelfChecking Digital Glitch Filter Verilog Following lattice document describes a glitch filter on page 6. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. Glitches frequently occur on lines carrying signals from sources such as rf receivers. (i found this solution at. A user asks how to use systemverilog assertion to detect glitch duration. Digital Glitch Filter Verilog.

From dokumen.tips

(PDF) NI 9326 Datasheet NI · Programmable Digital Glitch Filter The Digital Glitch Filter Verilog (i found this solution at. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. Glitches frequently occur on lines carrying signals from sources such as rf receivers. The proposed solution is based. But at cdc, or asynchronous design we must verify that the design is glitch free. While i. Digital Glitch Filter Verilog.

From www.youtube.com

Digital Glitch Footage (Flashing Lights Warning) Computer Glitches Digital Glitch Filter Verilog Following lattice document describes a glitch filter on page 6. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. The proposed solution is based. But at cdc, or asynchronous. Digital Glitch Filter Verilog.

From www.beyond-circuits.com

Tutorial 12 Rotary Encoder Beyond Circuits Digital Glitch Filter Verilog Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. (i found this solution at. While i understand some debouncing filters in vhdl can anyone give me. Glitches frequently occur on lines carrying signals from sources such as rf receivers. How can i implement a glitch filter ? A repo. Digital Glitch Filter Verilog.

From www.dreamstime.com

390 Digital Glitch a Glitchy and Digitalinspired Background Featuring Digital Glitch Filter Verilog How can i implement a glitch filter ? A repo of basic verilog/systemverilog modules useful in other circuits. Following lattice document describes a glitch filter on page 6. Glitches frequently occur on lines carrying signals from sources such as rf receivers. The proposed solution is based. While i understand some debouncing filters in vhdl can anyone give me. Glitch filtering. Digital Glitch Filter Verilog.

From www.vectorstock.com

Digital glitch screen effect glitched video Vector Image Digital Glitch Filter Verilog A repo of basic verilog/systemverilog modules useful in other circuits. Following lattice document describes a glitch filter on page 6. (i found this solution at. How can i implement a glitch filter ? Glitches frequently occur on lines carrying signals from sources such as rf receivers. But at cdc, or asynchronous design we must verify that the design is glitch. Digital Glitch Filter Verilog.

From www.dreamstime.com

Software Source Code Over Digital Glitch Effect Stock Photo Image of Digital Glitch Filter Verilog Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. A repo of basic verilog/systemverilog modules useful in other circuits. How can i implement a glitch filter ? Following lattice. Digital Glitch Filter Verilog.

From www.researchgate.net

Dynamic PFD with glitch removal circuit. Download Scientific Diagram Digital Glitch Filter Verilog But at cdc, or asynchronous design we must verify that the design is glitch free. Following lattice document describes a glitch filter on page 6. Glitches frequently occur on lines carrying signals from sources such as rf receivers. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. Glitch filtering. Digital Glitch Filter Verilog.

From www.youtube.com

Electronics Glitch filter implementation YouTube Digital Glitch Filter Verilog While i understand some debouncing filters in vhdl can anyone give me. (i found this solution at. Glitches frequently occur on lines carrying signals from sources such as rf receivers. The proposed solution is based. Following lattice document describes a glitch filter on page 6. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback. Digital Glitch Filter Verilog.

From insider.kelbyone.com

Create a Digital Glitch Effect in by Lesa Snider KelbyOne Digital Glitch Filter Verilog (i found this solution at. Glitches frequently occur on lines carrying signals from sources such as rf receivers. A repo of basic verilog/systemverilog modules useful in other circuits. How can i implement a glitch filter ? The proposed solution is based. While i understand some debouncing filters in vhdl can anyone give me. Glitch filtering is the process of removing. Digital Glitch Filter Verilog.

From stock.adobe.com

Pixel pattern of a digital glitch / Abstract background, pattern of a Digital Glitch Filter Verilog (i found this solution at. Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. A repo of basic verilog/systemverilog modules useful in other circuits. Glitches frequently occur on lines carrying signals from sources such as rf receivers. A user asks how to use systemverilog assertion to detect glitch duration. Digital Glitch Filter Verilog.

From itecnotes.com

Electronic Glitch filter implementation Valuable Tech Notes Digital Glitch Filter Verilog Following lattice document describes a glitch filter on page 6. How can i implement a glitch filter ? A repo of basic verilog/systemverilog modules useful in other circuits. The proposed solution is based. But at cdc, or asynchronous design we must verify that the design is glitch free. Glitches frequently occur on lines carrying signals from sources such as rf. Digital Glitch Filter Verilog.

From electronics.stackexchange.com

digital logic Glitch in circuit consisting of 2 flip flops Digital Glitch Filter Verilog The proposed solution is based. (i found this solution at. While i understand some debouncing filters in vhdl can anyone give me. Following lattice document describes a glitch filter on page 6. How can i implement a glitch filter ? A repo of basic verilog/systemverilog modules useful in other circuits. Glitch filtering is the process of removing unwanted pulses from. Digital Glitch Filter Verilog.

From uspto.report

Digital glitch filter Patent Grant Lin , et al. Feb [NXP USA, INC.] Digital Glitch Filter Verilog The proposed solution is based. Glitches frequently occur on lines carrying signals from sources such as rf receivers. How can i implement a glitch filter ? But at cdc, or asynchronous design we must verify that the design is glitch free. A repo of basic verilog/systemverilog modules useful in other circuits. (i found this solution at. Glitch filtering is the. Digital Glitch Filter Verilog.

From cadence.okstate.edu

Simulation with VerilogXL Digital Glitch Filter Verilog Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. How can i implement a glitch filter ? A repo of basic verilog/systemverilog modules useful in other circuits. Glitches frequently occur on lines carrying signals from sources such as rf receivers. A user asks how to use systemverilog assertion to. Digital Glitch Filter Verilog.

From elements.envato.com

Digital Glitches Seamless Loop, Stock Video Envato Elements Digital Glitch Filter Verilog Glitches frequently occur on lines carrying signals from sources such as rf receivers. But at cdc, or asynchronous design we must verify that the design is glitch free. While i understand some debouncing filters in vhdl can anyone give me. (i found this solution at. The proposed solution is based. How can i implement a glitch filter ? A user. Digital Glitch Filter Verilog.

From www.embedded.com

Asynchronous reset synchronization and distribution Special cases Digital Glitch Filter Verilog A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. Glitches frequently occur on lines carrying signals from sources such as rf receivers. (i found this solution at. But at cdc, or asynchronous design we must verify that the design is glitch free. A repo of basic verilog/systemverilog modules useful. Digital Glitch Filter Verilog.

From itecnotes.com

Electronic Debounce circuit design in Verilog Valuable Tech Notes Digital Glitch Filter Verilog How can i implement a glitch filter ? A repo of basic verilog/systemverilog modules useful in other circuits. A user asks how to use systemverilog assertion to detect glitch duration and gets feedback from other users and experts. The proposed solution is based. But at cdc, or asynchronous design we must verify that the design is glitch free. (i found. Digital Glitch Filter Verilog.

From docs.madmachine.io

How did I debug I2C communication failure? MadMachine Digital Glitch Filter Verilog Glitch filtering is the process of removing unwanted pulses from a digital input signal that is usually high or low. How can i implement a glitch filter ? Following lattice document describes a glitch filter on page 6. (i found this solution at. While i understand some debouncing filters in vhdl can anyone give me. The proposed solution is based.. Digital Glitch Filter Verilog.