Frequency Divider Vhdl Code . A cleaner solution for a clock divider would be: Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Integer range 0 to c_count_max :=. Can i do it with integer type or do i need something else to run the decimal number? In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. I want to divide the clock frequency divide by 5. It should generate clock enables instead. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. Generally, using logic to create a divided clock is not recommended in an fpga.

from vhdlwhiz.com

In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Generally, using logic to create a divided clock is not recommended in an fpga. It should generate clock enables instead. Integer range 0 to c_count_max :=. Can i do it with integer type or do i need something else to run the decimal number? I want to divide the clock frequency divide by 5. A cleaner solution for a clock divider would be: You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the.

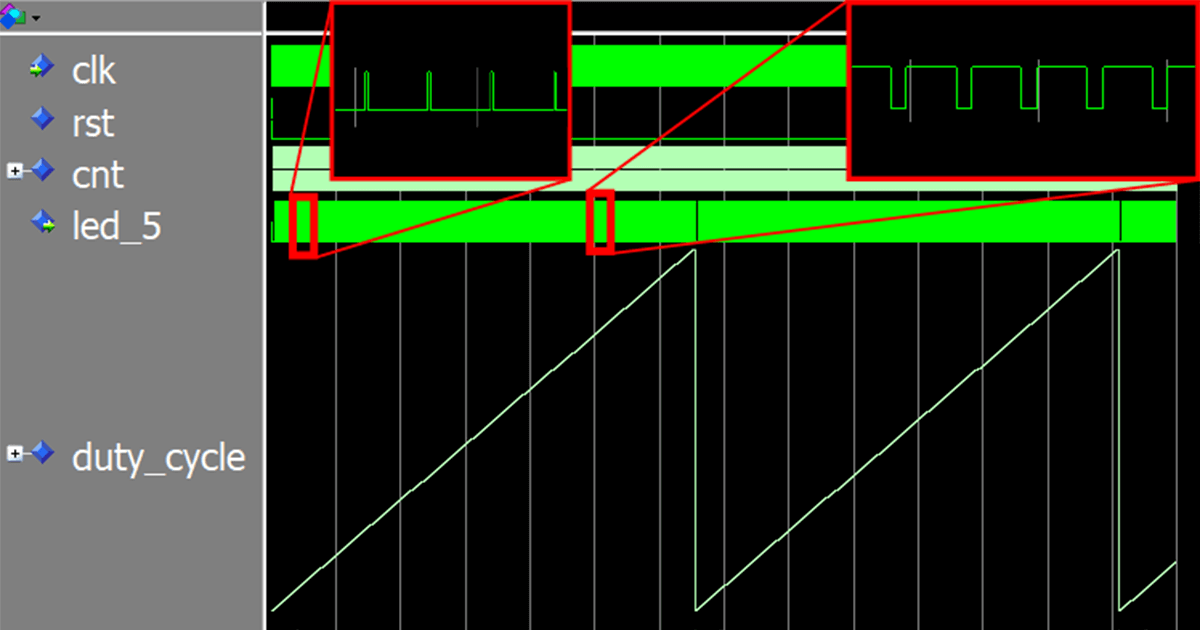

How to create a PWM controller in VHDL VHDLwhiz

Frequency Divider Vhdl Code Generally, using logic to create a divided clock is not recommended in an fpga. Can i do it with integer type or do i need something else to run the decimal number? I want to divide the clock frequency divide by 5. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. A cleaner solution for a clock divider would be: It should generate clock enables instead. In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. Generally, using logic to create a divided clock is not recommended in an fpga. Integer range 0 to c_count_max :=. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the.

From github.com

GitHub lincanbin/VHDLFrequencyDivider Quartus 9.0 Project of Frequency Divider Vhdl Code In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. A cleaner solution for a clock divider would be: Generally, using logic to create a divided clock is not recommended in an fpga. Vhdl. Frequency Divider Vhdl Code.

From www.circuits-diy.com

Frequency Divider Circuit Frequency Divider Vhdl Code You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. I want to divide the clock frequency divide by 5. Integer range 0 to c_count_max :=. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. A cleaner solution for. Frequency Divider Vhdl Code.

From stackoverflow.com

8 bit 8 bit Frequency Divider VHDL Stack Overflow Frequency Divider Vhdl Code Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Can i do it with integer type or do i need something else to run the decimal number? I want to divide the clock frequency divide by 5. Integer range 0 to c_count_max :=. Generally, using logic to create a divided clock is not recommended in. Frequency Divider Vhdl Code.

From www.vrogue.co

Frequency Divider Circuit Using 555 And 4017 Using 55 vrogue.co Frequency Divider Vhdl Code Generally, using logic to create a divided clock is not recommended in an fpga. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Integer range 0 to c_count_max :=.. Frequency Divider Vhdl Code.

From www.youtube.com

VHDL Lecture 24 Lab 8 Clock Divider and Counters Explanation YouTube Frequency Divider Vhdl Code Can i do it with integer type or do i need something else to run the decimal number? A cleaner solution for a clock divider would be: Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Generally, using logic to create a divided clock is not recommended in an fpga. It should generate clock enables. Frequency Divider Vhdl Code.

From www.edn.com

VHDL code implements 50dutycycle divider EDN Frequency Divider Vhdl Code Can i do it with integer type or do i need something else to run the decimal number? In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. You can use the code above. Frequency Divider Vhdl Code.

From fixlibrarygedwaaldebx.z21.web.core.windows.net

Clock Divider Circuit Diagram Frequency Divider Vhdl Code Generally, using logic to create a divided clock is not recommended in an fpga. Integer range 0 to c_count_max :=. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the.. Frequency Divider Vhdl Code.

From www.chegg.com

Redesign this divider circuit and VHDL Frequency Divider Vhdl Code In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. Generally, using logic to create a divided clock is not recommended in an fpga. Vhdl and verilog implementations for a clock frequency divider implemented. Frequency Divider Vhdl Code.

From www.chegg.com

Solved Write The VHDL Code For A 41 Multiplexer. You Can... Frequency Divider Vhdl Code Integer range 0 to c_count_max :=. Can i do it with integer type or do i need something else to run the decimal number? Generally, using logic to create a divided clock is not recommended in an fpga. It should generate clock enables instead. I want to divide the clock frequency divide by 5. You can use the code above. Frequency Divider Vhdl Code.

From www.chegg.com

8bit frequency divider 1. Write a VHDL file or Frequency Divider Vhdl Code Can i do it with integer type or do i need something else to run the decimal number? Generally, using logic to create a divided clock is not recommended in an fpga. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. In the. Frequency Divider Vhdl Code.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Frequency Divider Vhdl Code It should generate clock enables instead. Integer range 0 to c_count_max :=. Generally, using logic to create a divided clock is not recommended in an fpga. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. Can i do it with integer type or. Frequency Divider Vhdl Code.

From www.scribd.com

VHDL Code For Clock Divider (Frequency Divider) PDF Vhdl Field Frequency Divider Vhdl Code In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Generally, using logic to create a divided clock is not. Frequency Divider Vhdl Code.

From www.chegg.com

Describe the clock divider circuit in VHDL using the Frequency Divider Vhdl Code Integer range 0 to c_count_max :=. I want to divide the clock frequency divide by 5. In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. You can use the code above for your. Frequency Divider Vhdl Code.

From jjmk.dk

Solution VHDL Mux Display Frequency Divider Vhdl Code You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. Can i do it with integer type or do i need something else to run the decimal number? Integer range 0 to c_count_max :=. Generally, using logic to create a divided clock is not. Frequency Divider Vhdl Code.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Frequency Divider Vhdl Code Can i do it with integer type or do i need something else to run the decimal number? Vhdl and verilog implementations for a clock frequency divider implemented at a component level. In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in. Frequency Divider Vhdl Code.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Frequency Divider Vhdl Code I want to divide the clock frequency divide by 5. Can i do it with integer type or do i need something else to run the decimal number? Integer range 0 to c_count_max :=. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the.. Frequency Divider Vhdl Code.

From eevibes.com

What are the Divider Circuits? VHDL Code for the Divider Circuits EE Frequency Divider Vhdl Code Vhdl and verilog implementations for a clock frequency divider implemented at a component level. In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. Integer range 0 to c_count_max :=. I want to divide. Frequency Divider Vhdl Code.

From www.allaboutcircuits.com

Basic Binary Division The Algorithm and the VHDL Code Technical Articles Frequency Divider Vhdl Code A cleaner solution for a clock divider would be: In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. It should generate clock enables instead. Generally, using logic to create a divided clock is. Frequency Divider Vhdl Code.

From www.youtube.com

VHDL BASIC Tutorial Clock Divider YouTube Frequency Divider Vhdl Code I want to divide the clock frequency divide by 5. Can i do it with integer type or do i need something else to run the decimal number? You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. Generally, using logic to create a. Frequency Divider Vhdl Code.

From www.youtube.com

Electronics clock frequency divide by 5 vhdl (2 Solutions!!) YouTube Frequency Divider Vhdl Code In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. Generally, using logic to create a divided clock is not recommended in an fpga. Can i do it with integer type or do i. Frequency Divider Vhdl Code.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Frequency Divider Vhdl Code In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. It should generate clock enables instead. Integer range 0 to c_count_max :=. A cleaner solution for a clock divider would be: Generally, using logic. Frequency Divider Vhdl Code.

From www.researchgate.net

Quadrature generator / frequency divider using two D flipflops Frequency Divider Vhdl Code In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. Generally, using logic to create a divided clock is not recommended in an fpga. It should generate clock enables instead. You can use the. Frequency Divider Vhdl Code.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Frequency Divider Vhdl Code Integer range 0 to c_count_max :=. I want to divide the clock frequency divide by 5. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. A cleaner solution for a clock divider would be: You can use the code above for your vhdl clock design if you need a clock divider by an integer in. Frequency Divider Vhdl Code.

From www.youtube.com

VHDL Lecture 23 Lab 8 Clock Dividers and Counters YouTube Frequency Divider Vhdl Code In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. A cleaner solution for a clock divider would be: I want to divide the clock frequency divide by 5. Can i do it with. Frequency Divider Vhdl Code.

From www.slideserve.com

PPT Integration of entities in VHDL PowerPoint Presentation, free Frequency Divider Vhdl Code A cleaner solution for a clock divider would be: It should generate clock enables instead. I want to divide the clock frequency divide by 5. Integer range 0 to c_count_max :=. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Can i do it with integer type or do i need something else to run. Frequency Divider Vhdl Code.

From jimmy-embedded-c-n-vhdl.blogspot.com

Technology Simplified VHDL code for Clock Divider Frequency Divider Vhdl Code It should generate clock enables instead. A cleaner solution for a clock divider would be: I want to divide the clock frequency divide by 5. Generally, using logic to create a divided clock is not recommended in an fpga. Integer range 0 to c_count_max :=. Can i do it with integer type or do i need something else to run. Frequency Divider Vhdl Code.

From www.edaboard.com

Frequency Divider in VHDL Forum for Electronics Frequency Divider Vhdl Code Integer range 0 to c_count_max :=. Can i do it with integer type or do i need something else to run the decimal number? It should generate clock enables instead. I want to divide the clock frequency divide by 5. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. A cleaner solution for a clock. Frequency Divider Vhdl Code.

From vhdlwhiz.com

How to create a PWM controller in VHDL VHDLwhiz Frequency Divider Vhdl Code Generally, using logic to create a divided clock is not recommended in an fpga. Can i do it with integer type or do i need something else to run the decimal number? You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. It should. Frequency Divider Vhdl Code.

From www.youtube.com

25 Verilog Clock Divider YouTube Frequency Divider Vhdl Code Generally, using logic to create a divided clock is not recommended in an fpga. I want to divide the clock frequency divide by 5. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. Can i do it with integer type or do i. Frequency Divider Vhdl Code.

From www.embeddedrelated.com

VHDL tutorial combining clocked and sequential logic Gene Breniman Frequency Divider Vhdl Code Integer range 0 to c_count_max :=. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Generally, using logic to create a divided clock is not recommended in an fpga.. Frequency Divider Vhdl Code.

From www.scribd.com

Frequency Divider Using VHDL PDF Field Programmable Gate Array Frequency Divider Vhdl Code I want to divide the clock frequency divide by 5. Generally, using logic to create a divided clock is not recommended in an fpga. A cleaner solution for a clock divider would be: Can i do it with integer type or do i need something else to run the decimal number? It should generate clock enables instead. Integer range 0. Frequency Divider Vhdl Code.

From www.youtube.com

Frequency Divider Vhdl (Model sim) YouTube Frequency Divider Vhdl Code It should generate clock enables instead. A cleaner solution for a clock divider would be: In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in by 2 as explained in the main vhdl. Integer range 0 to c_count_max :=. I want to. Frequency Divider Vhdl Code.

From www.slideserve.com

PPT Integration of entities in VHDL PowerPoint Presentation, free Frequency Divider Vhdl Code It should generate clock enables instead. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Can i do it with integer type or do i need something else to. Frequency Divider Vhdl Code.

From pgandhi189.blogspot.com

VLSI verification blogs Design of frequency divider using modulo Frequency Divider Vhdl Code Can i do it with integer type or do i need something else to run the decimal number? Vhdl and verilog implementations for a clock frequency divider implemented at a component level. In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out is obtained by dividing the frequency of clk_in. Frequency Divider Vhdl Code.

From www.researchgate.net

Combinational Divider in VHDL Using this combinational divider, test Frequency Divider Vhdl Code Generally, using logic to create a divided clock is not recommended in an fpga. You can use the code above for your vhdl clock design if you need a clock divider by an integer in your design without using the. In the vhdl code for simulation purposes, the divisor is set to be 1 so the clock frequency of clk_out. Frequency Divider Vhdl Code.