Data Memory Barrier Arm . Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. Without dmb, the processor could reorder a. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. In reality, atomic instructions are used in pair with barrier. Depending on the barrier type,. The arm architecture defines barrier instructions to force memory access ordering. The dmb in particular prevents memory access reordering around the dmb. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction.

from community.arm.com

Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The arm architecture defines barrier instructions to force memory access ordering. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The dmb in particular prevents memory access reordering around the dmb. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. In reality, atomic instructions are used in pair with barrier. Depending on the barrier type,. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Without dmb, the processor could reorder a. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction.

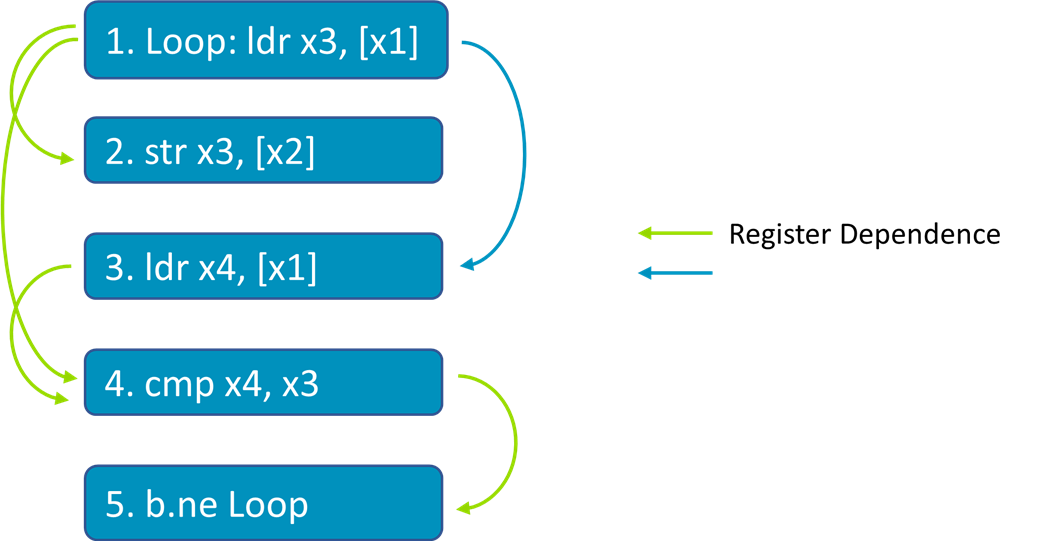

Eliminating memory barriers with the Execution Dependence Extension

Data Memory Barrier Arm Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The arm architecture defines barrier instructions to force memory access ordering. Without dmb, the processor could reorder a. In reality, atomic instructions are used in pair with barrier. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Depending on the barrier type,. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The dmb in particular prevents memory access reordering around the dmb. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction.

From secureopeners.com

HySecurity StrongArm M50 CE Hydraulic DualArm AntiRam Barrier Arm Data Memory Barrier Arm Depending on the barrier type,. The arm architecture defines barrier instructions to force memory access ordering. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Memory barriers can be triggered by hardware operations within the processor. Data Memory Barrier Arm.

From www.vxworks.net

Arm体系结构之内存序与内存屏障 Data Memory Barrier Arm Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. Without dmb, the processor could reorder a. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The arm architecture defines barrier instructions to force. Data Memory Barrier Arm.

From www.youtube.com

12 ft Sectional Barrier Gate Arm Assembly Instructions Easy Data Memory Barrier Arm The dmb in particular prevents memory access reordering around the dmb. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The arm architecture defines barrier instructions to force memory access ordering. Depending on the barrier type,. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. In reality, atomic. Data Memory Barrier Arm.

From open4tech.com

Direct Memory Access (DMA) in Embedded Systems Open4Tech Data Memory Barrier Arm The arm architecture defines barrier instructions to force memory access ordering. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The dmb in particular prevents memory access reordering around the dmb. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. Without dmb, the processor could reorder a.. Data Memory Barrier Arm.

From brandiscrafts.com

Arm Memory Barrier? 13 Most Correct Answers Data Memory Barrier Arm The arm architecture defines barrier instructions to force memory access ordering. Without dmb, the processor could reorder a. Depending on the barrier type,. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. In reality, atomic instructions are used in pair with barrier. The dmb in particular prevents memory access reordering around the dmb.. Data Memory Barrier Arm.

From zhuanlan.zhihu.com

内存屏障Memory Barrier a Hardware View 知乎 Data Memory Barrier Arm In reality, atomic instructions are used in pair with barrier. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Armv6 also introduced. Data Memory Barrier Arm.

From stebilex.com

HySecurity StrongArm Barrier M50 in UAE & Qatar Data Memory Barrier Arm The arm architecture defines barrier instructions to force memory access ordering. In reality, atomic instructions are used in pair with barrier. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Armv6 also introduced the new data memory barrier. Data Memory Barrier Arm.

From www.externalworksindex.co.uk

FB automatic drop arm barrier (up to 9m span) Frontier Pitts ESI Data Memory Barrier Arm Depending on the barrier type,. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. In reality, atomic instructions are used in pair with barrier. Without dmb, the processor could reorder a. Data memory barrier (dmb) prevents. Data Memory Barrier Arm.

From linuxdevices.org

Nextgen ARM cores break memory barrier, add hypervisor support Data Memory Barrier Arm Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. In reality, atomic instructions are used in pair with barrier. The dmb in particular prevents memory access reordering around the dmb. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The data memory barrier (dmb) prevents the reordering of. Data Memory Barrier Arm.

From gateopenersafety.com

GateArms+ Barrier Arm Joint Connection Kit For Joining Two Barrier Data Memory Barrier Arm Without dmb, the processor could reorder a. In reality, atomic instructions are used in pair with barrier. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The arm architecture defines barrier instructions to force memory access ordering. The dmb. Data Memory Barrier Arm.

From www.youtube.com

Barrier Arm LED Light Installation Guide StepbyStep Tutorial All Data Memory Barrier Arm The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The arm architecture defines barrier instructions to force memory access ordering. Depending on the barrier type,. In reality, atomic instructions are used in pair with barrier. Data. Data Memory Barrier Arm.

From blog.csdn.net

ARM基础(5):内存屏障的必要性、内存类型和内存排序_arm 内存屏障CSDN博客 Data Memory Barrier Arm Depending on the barrier type,. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. In reality, atomic instructions are used in pair with barrier. Without dmb, the processor could reorder a. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The arm architecture defines barrier instructions to force. Data Memory Barrier Arm.

From zhuanlan.zhihu.com

理解 Memory barrier(内存屏障) 知乎 Data Memory Barrier Arm The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Depending on the barrier type,. The dmb in particular prevents memory access reordering around. Data Memory Barrier Arm.

From community.arm.com

Eliminating memory barriers with the Execution Dependence Extension Data Memory Barrier Arm In reality, atomic instructions are used in pair with barrier. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Depending. Data Memory Barrier Arm.

From secureopeners.com

HySecurity StrongArm M30 NP Adjustable Manual DualArm AntiRam Barrier Arm Data Memory Barrier Arm The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The arm architecture defines barrier instructions to force memory access ordering. Data memory. Data Memory Barrier Arm.

From aijishu.com

Arm架构下的Synchronization概述和案例分析白皮书 | 附下载 极术社区 连接开发者与智能计算生态 Data Memory Barrier Arm In reality, atomic instructions are used in pair with barrier. The dmb in particular prevents memory access reordering around the dmb. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Depending on the barrier type,. Memory barriers can be. Data Memory Barrier Arm.

From docslib.org

ARM CortexM Programming Guide to Memory Barrier Instructions Data Memory Barrier Arm Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. In reality, atomic instructions are used in pair with barrier. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The arm architecture defines barrier instructions to force memory access ordering. Armv6 also introduced the new data memory. Data Memory Barrier Arm.

From www.linkedin.com

DAY 13 of learning ARM LanguageA Brief Guide for Understanding DSB Data Memory Barrier Arm Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Depending on the barrier type,. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Armv6 also introduced the new data memory barrier. Data Memory Barrier Arm.

From brandiscrafts.com

Arm Memory Barrier? 13 Most Correct Answers Data Memory Barrier Arm Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. Without dmb, the processor could reorder a. Depending on the barrier type,. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. In. Data Memory Barrier Arm.

From www.vxworks.net

Arm体系结构之内存序与内存屏障 Data Memory Barrier Arm The arm architecture defines barrier instructions to force memory access ordering. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. The dmb in particular prevents memory access reordering around the dmb. Depending on the barrier type,. Data memory. Data Memory Barrier Arm.

From afana.me

Memory Barriers in · Nadeem Afana's Blog Data Memory Barrier Arm The arm architecture defines barrier instructions to force memory access ordering. The dmb in particular prevents memory access reordering around the dmb. Depending on the barrier type,. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Without dmb, the processor could reorder a. In reality, atomic instructions are used in pair with barrier. Memory barriers. Data Memory Barrier Arm.

From www.edsuk.com

Manual Barrier Arm EDS UK Data Memory Barrier Arm The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Without dmb, the processor could reorder a. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The dmb in particular prevents memory access reordering around the dmb. In reality, atomic instructions are used in pair with. Data Memory Barrier Arm.

From gateopenersafety.com

GateArms+ AutoControl MIB30 Barrier Arm Operator Compatible Data Memory Barrier Arm Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Without dmb, the processor could reorder a. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The arm architecture defines barrier instructions. Data Memory Barrier Arm.

From blog.csdn.net

内存barrier_cache barrierCSDN博客 Data Memory Barrier Arm The dmb in particular prevents memory access reordering around the dmb. Depending on the barrier type,. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. In reality, atomic instructions are used in pair with barrier. The arm. Data Memory Barrier Arm.

From brandiscrafts.com

Arm Memory Barrier? 13 Most Correct Answers Data Memory Barrier Arm Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Armv6 also introduced the new data memory barrier and flush prefetch. Data Memory Barrier Arm.

From totalsecuritywarehouse.com

Barrier Arm, alum, 14', 3" rnd, red/wht Total Security Warehouse Data Memory Barrier Arm In reality, atomic instructions are used in pair with barrier. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. The dsb instruction. Data Memory Barrier Arm.

From www.affordableopeners.com

HySecurity StrongArm M50 AntiRam Barrier Arm Data Memory Barrier Arm Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. The arm architecture defines barrier instructions to force memory access ordering. In reality, atomic instructions are used in pair with barrier. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Depending on the barrier type,. The dmb in particular. Data Memory Barrier Arm.

From www.slideserve.com

PPT ARM Introduction & Instruction Set Architecture PowerPoint Data Memory Barrier Arm In reality, atomic instructions are used in pair with barrier. The dmb in particular prevents memory access reordering around the dmb. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The arm architecture defines barrier instructions to force memory access ordering. Armv6 also introduced the new data memory barrier and flush prefetch buffer. Data Memory Barrier Arm.

From www.vanguardgroup.co.nz

Bionik Automated Barrier Arm Vanguard NZ Data Memory Barrier Arm Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Without dmb, the processor could reorder a. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Armv6 also introduced the. Data Memory Barrier Arm.

From www.barriersdirect.co.uk

Automatic Barrier Electric Barriers Barriers Direct Barriers Direct Data Memory Barrier Arm The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Data memory barrier (dmb) prevents reordering of data accesses instructions across. Data Memory Barrier Arm.

From www.researchgate.net

Memory Barrier with Reallocation Mechanism Download Scientific Diagram Data Memory Barrier Arm The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Without dmb, the processor could reorder a. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Armv6 also introduced the new data memory. Data Memory Barrier Arm.

From community.arm.com

Eliminating memory barriers with the Execution Dependence Extension Data Memory Barrier Arm Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. In reality, atomic instructions are used in pair with barrier. The dmb in particular prevents memory access reordering around the dmb. The dsb instruction is a special memory barrier,. Data Memory Barrier Arm.

From www.hampden.co.nz

Automated Barrier Arms — High Security Perimeter Specialist NZ Hampden Data Memory Barrier Arm The dsb instruction is a special memory barrier, that synchronizes the execution stream with memory accesses. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. The dmb in particular prevents memory access reordering around the dmb. The data memory barrier (dmb) prevents the reordering of specified explicit data accesses across the barrier instruction. Armv6 also. Data Memory Barrier Arm.

From www.youtube.com

ARM M3 Instruction barrier and memory barrier instructions YouTube Data Memory Barrier Arm The arm architecture defines barrier instructions to force memory access ordering. Depending on the barrier type,. In reality, atomic instructions are used in pair with barrier. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Data memory barrier (dmb) prevents reordering of data accesses instructions across the dmb instruction. The dmb in particular. Data Memory Barrier Arm.

From blog.csdn.net

Memory Barrier是啥CSDN博客 Data Memory Barrier Arm The dmb in particular prevents memory access reordering around the dmb. In reality, atomic instructions are used in pair with barrier. Armv6 also introduced the new data memory barrier and flush prefetch buffer cp15 operations. Memory barriers can be triggered by hardware operations within the processor or by memory barrier instructions. Without dmb, the processor could reorder a. The data. Data Memory Barrier Arm.