Clock Distribution Power . The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. Power consumption is the most critical metric for a clock distribution network. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the.

from www.slideserve.com

Power consumption is the most critical metric for a clock distribution network. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around.

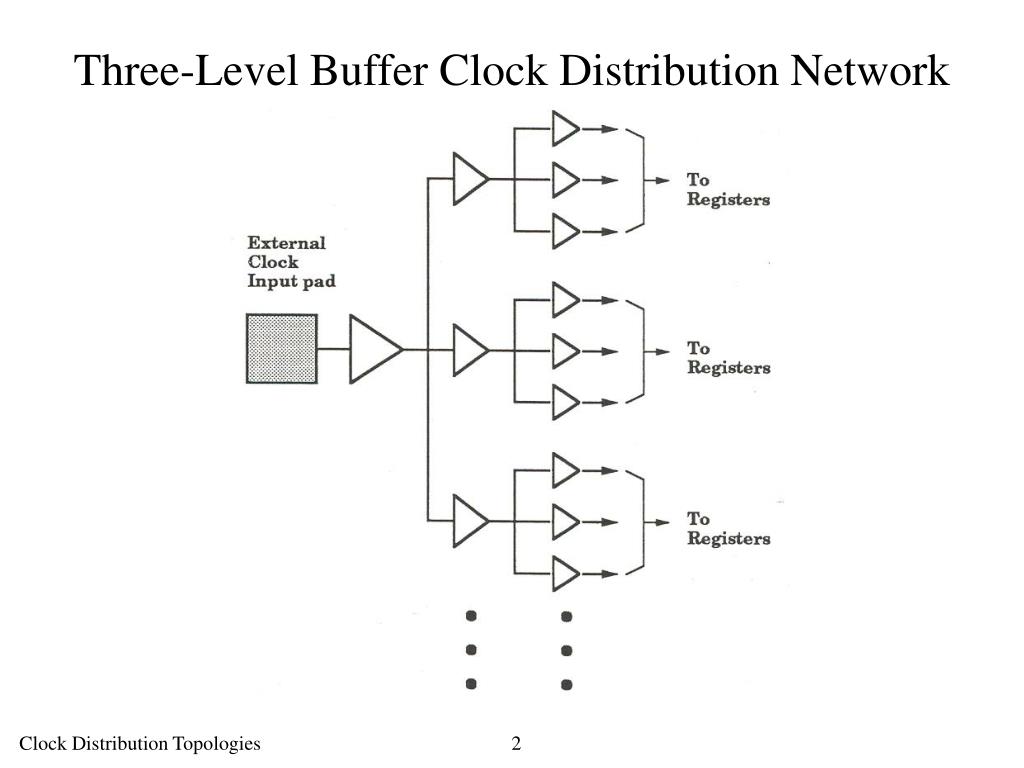

PPT Clock Distribution Topologies PowerPoint Presentation, free

Clock Distribution Power From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. Power consumption is the most critical metric for a clock distribution network.

From www.slideserve.com

PPT CMS GCT Hardware Wheel Card PowerPoint Presentation ID5093093 Clock Distribution Power From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. Power consumption is the most critical metric for a clock distribution network. Following these guidelines. Clock Distribution Power.

From www.indiamart.com

LowPower Clock Distribution Using a CurrentPulsed Clocked at Rs 10000 Clock Distribution Power The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. Power consumption is the most critical metric for a clock distribution network. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. From a power standpoint,. Clock Distribution Power.

From www.slideserve.com

PPT Inductor Design for Global Resonant Clock Distribution in a 28nm Clock Distribution Power • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. From a power standpoint, you save clock distribution power, so it. Clock Distribution Power.

From www.grassvalley.com

Densité Video Distribution Analog Grass Valley Clock Distribution Power The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. The clock skew within a clock distribution network is,. Clock Distribution Power.

From www.mdpi.com

Electronics Free FullText A 6Bit 20 GS/s TimeInterleaved Two Clock Distribution Power The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock.. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. Power consumption is the most critical metric for a clock distribution network. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. Following these guidelines. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. Following these guidelines can simultaneously reduce power supply. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID Clock Distribution Power Power consumption is the most critical metric for a clock distribution network. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm. Clock Distribution Power.

From www.slideserve.com

PPT Reconfigurable Clock Distribution Circuitry PowerPoint Clock Distribution Power Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around.. Clock Distribution Power.

From slideplayer.com

L22 Clock Issues in Deep Submircron Design ppt download Clock Distribution Power From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. • power distribution is now a complex task in deep submicron • clock design is. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. Power consumption is the most critical metric for a clock distribution network. • power distribution is now a complex task. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. Power consumption is the most critical metric for a clock distribution network. The network supports uniform power distribution with less than 1 db. Clock Distribution Power.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Distribution Power Power consumption is the most critical metric for a clock distribution network. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit. Clock Distribution Power.

From www.meinbergglobal.com

Application of the GPS Antenna Distributor Clock Distribution Power From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. The network supports uniform power distribution with less than 1 db variation across a 3. Clock Distribution Power.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Distribution Power The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. Power consumption is the most critical metric for a clock distribution network. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. From a power standpoint,. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power Power consumption is the most critical metric for a clock distribution network. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution from Past to Present PowerPoint Presentation Clock Distribution Power Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit. Clock Distribution Power.

From www.researchgate.net

Tree structure of a clock distribution network. Download High Clock Distribution Power The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. Power consumption is the most critical metric for a clock distribution network. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. The network supports uniform power distribution with less than 1 db. Clock Distribution Power.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Distribution Power The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. From a power standpoint, you save clock distribution power, so it tends to be good, but. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Distribution Power Power consumption is the most critical metric for a clock distribution network. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. From a power standpoint,. Clock Distribution Power.

From www.researchgate.net

Global clock distribution network, consisting of 16 resonant clock Clock Distribution Power The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. Power consumption is the most critical metric for a clock distribution network. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. The. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID Clock Distribution Power Power consumption is the most critical metric for a clock distribution network. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in. Clock Distribution Power.

From www.researchgate.net

CMOS clock generation. (a) CML to CMOS conversion. (b) Dutycycle Clock Distribution Power Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm. Clock Distribution Power.

From semiengineering.com

Clocks Getting Skewed Up Clock Distribution Power The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. From a power standpoint, you save clock distribution power, so it tends to be good, but. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power The clock skew within a clock distribution network is, in particular, an important factor that affects timing margins and circuit operation. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. • power distribution is now a complex task in deep submicron • clock design is. Clock Distribution Power.

From www.researchgate.net

(PDF) Low Power at Different levels of VLSI Design an clock Clock Distribution Power Power consumption is the most critical metric for a clock distribution network. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. The network supports uniform. Clock Distribution Power.

From www.semanticscholar.org

Figure 6 from Comparison between Low Power Clock Distribution Schemes Clock Distribution Power • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. The network supports uniform power distribution with less. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution Topologies PowerPoint Presentation, free Clock Distribution Power Power consumption is the most critical metric for a clock distribution network. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. From a power standpoint, you save clock distribution power,. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. From a power standpoint, you save clock distribution power, so it tends to be good, but the latency to get things through a chip. Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. Power consumption is the most critical metric for a. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID Clock Distribution Power • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. From a power standpoint, you save clock distribution power,. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Distribution Power • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. Power consumption is the most critical metric for a. Clock Distribution Power.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Clock Distribution Power Following these guidelines can simultaneously reduce power supply noise sensitivity and power consumption of the clock. Power consumption is the most critical metric for a clock distribution network. • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. From a power standpoint,. Clock Distribution Power.

From www.youtube.com

Clock Distribution H Tree Clock Distribution Network Three Level Clock Distribution Power • power distribution is now a complex task in deep submicron • clock design is also a complex issue in dsm due to rc delay components in the. The network supports uniform power distribution with less than 1 db variation across a 3 × 3 mm2 active chip area and around. The clock skew within a clock distribution network is,. Clock Distribution Power.