Use Of Virtual Clock In Synthesis . So from this blog, you can answer the below set of questions: Using a virtual clock is just one of the methods to constrain the inputs and outputs. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. How to constrain the input, output and internal path of a single clock design. A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. A virtual clock is a clock that exists but is not associated with any pin or port of the design. It is used as a reference in timing analysis to specify the input and output delays relative to a clock. When do we must use virtual clocks?. It allows designers to analyze and optimize the. Q1) what is the generated clock? When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. Can anyone provide a simple example how to use virtual clocks for synthesis / sta?

from www.slideserve.com

When do we must use virtual clocks?. A virtual clock is a clock that exists but is not associated with any pin or port of the design. It allows designers to analyze and optimize the. When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. Q1) what is the generated clock? It is used as a reference in timing analysis to specify the input and output delays relative to a clock. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. So from this blog, you can answer the below set of questions: Can anyone provide a simple example how to use virtual clocks for synthesis / sta? How to constrain the input, output and internal path of a single clock design.

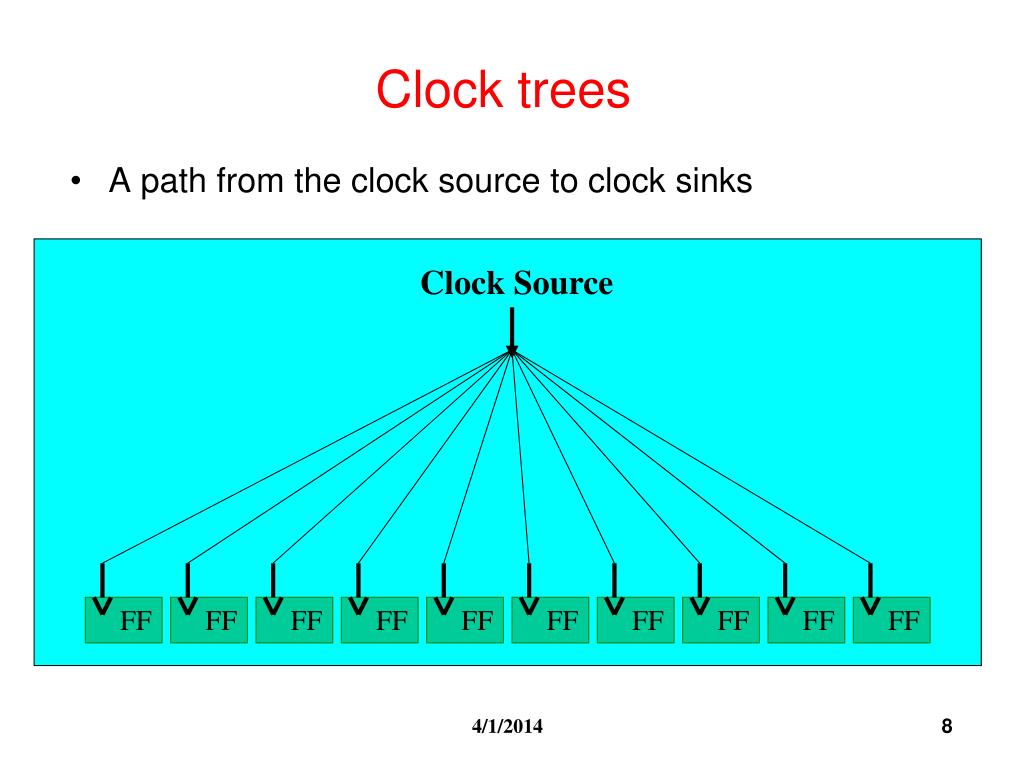

PPT Clock Network Synthesis PowerPoint Presentation, free download

Use Of Virtual Clock In Synthesis Using a virtual clock is just one of the methods to constrain the inputs and outputs. It is used as a reference in timing analysis to specify the input and output delays relative to a clock. Can anyone provide a simple example how to use virtual clocks for synthesis / sta? It allows designers to analyze and optimize the. Using a virtual clock is just one of the methods to constrain the inputs and outputs. How to constrain the input, output and internal path of a single clock design. A virtual clock is a clock that exists but is not associated with any pin or port of the design. Q1) what is the generated clock? When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. When do we must use virtual clocks?. So from this blog, you can answer the below set of questions: A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior.

From gamesmartz.com

Synthesis Definition & Image GameSmartz Use Of Virtual Clock In Synthesis A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. So from this blog, you can answer the below set of questions: Can anyone provide a simple example how to use virtual clocks for synthesis / sta? A. Use Of Virtual Clock In Synthesis.

From www.researchgate.net

Flow chart of virtual viewpoint synthesis algorithm based on image Use Of Virtual Clock In Synthesis It allows designers to analyze and optimize the. Can anyone provide a simple example how to use virtual clocks for synthesis / sta? It is used as a reference in timing analysis to specify the input and output delays relative to a clock. When do we must use virtual clocks?. Q1) what is the generated clock? A virtual clock is. Use Of Virtual Clock In Synthesis.

From www.slideserve.com

PPT An Efficient Clustering Algorithm For Low Power Clock Tree Use Of Virtual Clock In Synthesis So from this blog, you can answer the below set of questions: How to constrain the input, output and internal path of a single clock design. When do we must use virtual clocks?. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. A virtual clock is used as a reference to. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis A virtual clock is a clock that exists but is not associated with any pin or port of the design. It is used as a reference in timing analysis to specify the input and output delays relative to a clock. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. When we. Use Of Virtual Clock In Synthesis.

From www.pinterest.com

Interactive clock analog clock digital movable teaching clock Use Of Virtual Clock In Synthesis Q1) what is the generated clock? A virtual clock is a clock that exists but is not associated with any pin or port of the design. Using a virtual clock is just one of the methods to constrain the inputs and outputs. Can anyone provide a simple example how to use virtual clocks for synthesis / sta? It allows designers. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

CLOCK_TREE_SYNTHESIS(pavan) VLSI Guru Use Of Virtual Clock In Synthesis It allows designers to analyze and optimize the. Can anyone provide a simple example how to use virtual clocks for synthesis / sta? It is used as a reference in timing analysis to specify the input and output delays relative to a clock. Using a virtual clock is just one of the methods to constrain the inputs and outputs. Q1). Use Of Virtual Clock In Synthesis.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Use Of Virtual Clock In Synthesis A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. It allows designers to analyze and optimize. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis It is used as a reference in timing analysis to specify the input and output delays relative to a clock. When do we must use virtual clocks?. A virtual clock is a clock that exists but is not associated with any pin or port of the design. Using a virtual clock is just one of the methods to constrain the. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

CLOCK_TREE_SYNTHESIS(pavan) VLSI Guru Use Of Virtual Clock In Synthesis When do we must use virtual clocks?. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. Can anyone provide a simple example how to use virtual clocks for synthesis / sta? Using a virtual clock is just one of the methods to constrain the inputs and outputs. When we constrain our. Use Of Virtual Clock In Synthesis.

From www.researchgate.net

Clock Tree Synthesis Flow Download Scientific Diagram Use Of Virtual Clock In Synthesis How to constrain the input, output and internal path of a single clock design. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. It is used as a reference in timing analysis to specify the input and output delays relative to a clock. A virtual clock is used as a reference. Use Of Virtual Clock In Synthesis.

From www.mathlearningcenter.org

Math Clock The Math Learning Center Use Of Virtual Clock In Synthesis When do we must use virtual clocks?. When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. It allows designers to analyze and optimize the. A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it. Use Of Virtual Clock In Synthesis.

From www.fernekes.com

Virtual Clock Manhattan, New York, Bangkok Fernekes Designs Inc. Use Of Virtual Clock In Synthesis It is used as a reference in timing analysis to specify the input and output delays relative to a clock. So from this blog, you can answer the below set of questions: Q1) what is the generated clock? The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. It allows designers to. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis So from this blog, you can answer the below set of questions: It allows designers to analyze and optimize the. Can anyone provide a simple example how to use virtual clocks for synthesis / sta? A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with. Use Of Virtual Clock In Synthesis.

From www.slideserve.com

PPT Clock Network Synthesis PowerPoint Presentation, free download Use Of Virtual Clock In Synthesis When do we must use virtual clocks?. So from this blog, you can answer the below set of questions: The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. How to constrain the input, output and internal path of a single clock design. It allows designers to analyze and optimize the. Can. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. How to constrain the input, output and internal path of a single clock design. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. Using a virtual clock is just one. Use Of Virtual Clock In Synthesis.

From gridfiti.com

15+ Aesthetic Online Clock sites, Extensions & Apps (Full Screen) Use Of Virtual Clock In Synthesis It allows designers to analyze and optimize the. A virtual clock is a clock that exists but is not associated with any pin or port of the design. Can anyone provide a simple example how to use virtual clocks for synthesis / sta? A virtual clock is used as a reference to constrain the interface pins by relating the arrivals. Use Of Virtual Clock In Synthesis.

From www.fernekes.com

Virtual Clock Manhattan, New York, Bangkok Fernekes Designs Inc. Use Of Virtual Clock In Synthesis When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. When do we must use virtual clocks?. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. Q1) what is the generated clock? How to constrain the input, output and internal. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis It allows designers to analyze and optimize the. It is used as a reference in timing analysis to specify the input and output delays relative to a clock. When do we must use virtual clocks?. When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. The virtual clock helps. Use Of Virtual Clock In Synthesis.

From www.alamy.com

A threedimensional virtual alarm clock is projected by the screen of a Use Of Virtual Clock In Synthesis Using a virtual clock is just one of the methods to constrain the inputs and outputs. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. A virtual clock is a clock that exists but is not associated with any pin or port of the design. A virtual clock is used as. Use Of Virtual Clock In Synthesis.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Use Of Virtual Clock In Synthesis How to constrain the input, output and internal path of a single clock design. Q1) what is the generated clock? A virtual clock is a clock that exists but is not associated with any pin or port of the design. Using a virtual clock is just one of the methods to constrain the inputs and outputs. It is used as. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. Q1) what is the generated clock? Using a virtual clock is just one of the methods to constrain the inputs and. Use Of Virtual Clock In Synthesis.

From www.youtube.com

Virtual Clock Static Timing Analysis YouTube Use Of Virtual Clock In Synthesis Using a virtual clock is just one of the methods to constrain the inputs and outputs. A virtual clock is a clock that exists but is not associated with any pin or port of the design. When do we must use virtual clocks?. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing. Use Of Virtual Clock In Synthesis.

From www.timetrakgo.com

3 Benefits of Using a Virtual Time Clock for Your Business TimeTrakGO Use Of Virtual Clock In Synthesis When do we must use virtual clocks?. Using a virtual clock is just one of the methods to constrain the inputs and outputs. A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. The virtual clock helps in. Use Of Virtual Clock In Synthesis.

From www.youtube.com

Synthesis/STA virtual clock concept YouTube Use Of Virtual Clock In Synthesis The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. A virtual clock is a clock that exists but is. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. Using a virtual clock is just one of the methods to constrain the inputs and outputs. It allows designers to analyze and optimize the. The virtual clock helps. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. When do we must use virtual clocks?. It is used as a reference in timing analysis to specify the input and output delays relative to a clock. Using a virtual clock is just one of the methods to constrain the inputs and. Use Of Virtual Clock In Synthesis.

From www.mathlearningcenter.org

Math Clock The Math Learning Center Use Of Virtual Clock In Synthesis So from this blog, you can answer the below set of questions: The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. Using a virtual clock is just one of the methods to constrain the inputs and outputs. When we constrain our design using two create_clock commands for clka and clkb, the. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis A virtual clock is a clock that exists but is not associated with any pin or port of the design. A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. It is used as a reference in timing. Use Of Virtual Clock In Synthesis.

From www.youtube.com

Understanding Clock Tree Synthesis (CTS) in VLSI A Comprehensive Guide Use Of Virtual Clock In Synthesis When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with. Use Of Virtual Clock In Synthesis.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Use Of Virtual Clock In Synthesis Q1) what is the generated clock? How to constrain the input, output and internal path of a single clock design. When we constrain our design using two create_clock commands for clka and clkb, the synthesis tool by default considers the two. A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

CLOCK_TREE_SYNTHESIS(pavan) VLSI Guru Use Of Virtual Clock In Synthesis It allows designers to analyze and optimize the. The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. A virtual clock is a clock that exists but is not associated with any pin or port of the design. Can anyone provide a simple example how to use virtual clocks for synthesis /. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Use Of Virtual Clock In Synthesis A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. Q1) what is the generated clock? The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. It allows designers to. Use Of Virtual Clock In Synthesis.

From medium.com

A Virtual Analog Clock Created with Python by Aryaman Kukal Use Of Virtual Clock In Synthesis A virtual clock is a clock that exists but is not associated with any pin or port of the design. A virtual clock is used as a reference to constrain the interface pins by relating the arrivals at input/output ports with respect to it with the help of input and output delays. How to constrain the input, output and internal. Use Of Virtual Clock In Synthesis.

From www.vlsiguru.com

CLOCK_TREE_SYNTHESIS(pavan) VLSI Guru Use Of Virtual Clock In Synthesis It is used as a reference in timing analysis to specify the input and output delays relative to a clock. Can anyone provide a simple example how to use virtual clocks for synthesis / sta? Using a virtual clock is just one of the methods to constrain the inputs and outputs. When we constrain our design using two create_clock commands. Use Of Virtual Clock In Synthesis.

From vlsiuniverse.blogspot.com

Virtual clock example VLSI n EDA Use Of Virtual Clock In Synthesis The virtual clock helps in the physical design process by providing an abstraction of the circuit’s timing behavior. How to constrain the input, output and internal path of a single clock design. It allows designers to analyze and optimize the. When do we must use virtual clocks?. It is used as a reference in timing analysis to specify the input. Use Of Virtual Clock In Synthesis.