What Is Digital Clock In Vlsi . The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. It is used during the physical design process to evaluate and. In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock The clock is a narrow pulse A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock.

from siliconvlsi.com

A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock It is used during the physical design process to evaluate and. The clock is a narrow pulse By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and.

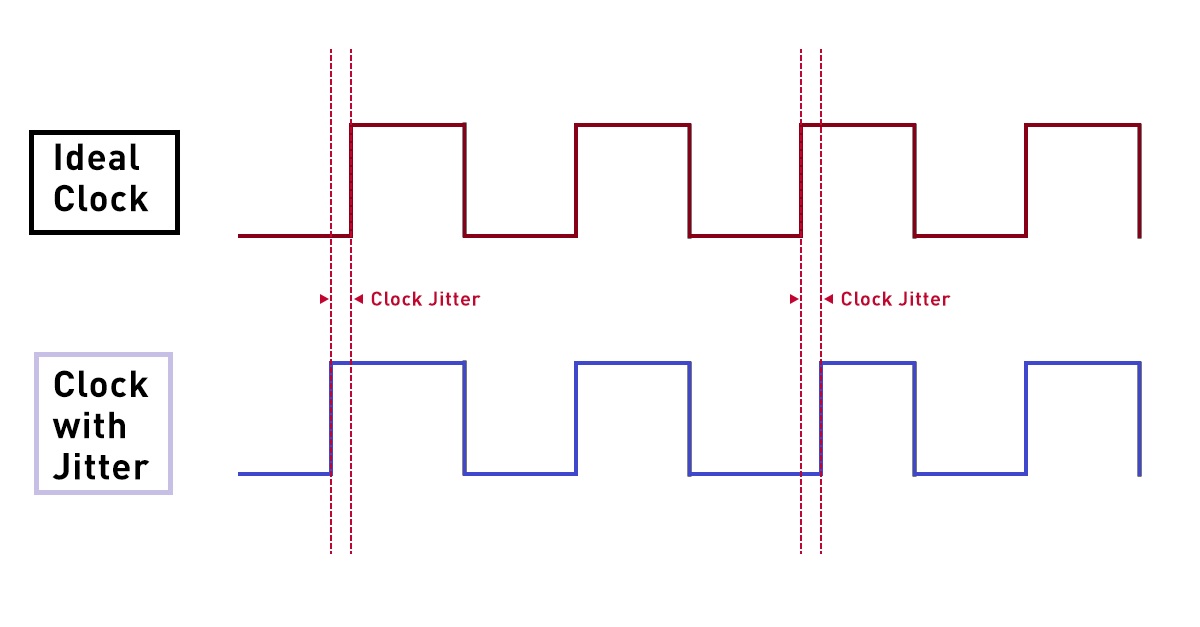

What do you mean by clock Jitter? Siliconvlsi

What Is Digital Clock In Vlsi The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. It is used during the physical design process to evaluate and. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. The clock is a narrow pulse A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock.

From www.vlsiguru.com

pdbasicsClocktreesynthesis vlsi What Is Digital Clock In Vlsi The clock is a narrow pulse A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. Inputs that come from other synchronous systems are based. What Is Digital Clock In Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis vlsi What Is Digital Clock In Vlsi The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. The clock is a narrow pulse By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. In sta it is used for specifying the input and output delays signal coming from or going to a block that. What Is Digital Clock In Vlsi.

From www.youtube.com

Digital Clock VLSI Design Lab Columbia University 2016 YouTube What Is Digital Clock In Vlsi The clock is a narrow pulse Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock It is used during the physical design process to evaluate and. In sta it is used for specifying the input and output delays signal coming from or going to a block that. What Is Digital Clock In Vlsi.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design What Is Digital Clock In Vlsi The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. The clock is a narrow pulse By adopting synchronous design principles, engineers can create. What Is Digital Clock In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Digital Clock In Vlsi In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. The clock is a narrow. What Is Digital Clock In Vlsi.

From www.youtube.com

Understanding Clock Tree Synthesis (CTS) in VLSI A Comprehensive Guide What Is Digital Clock In Vlsi In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. It is used during the physical design process to evaluate and. The clock is a narrow pulse Inputs that come from other synchronous systems are based on a different system clock, which is typically. What Is Digital Clock In Vlsi.

From vlsi-freaks.blogspot.com

VLSI freaks virtual clocks and their usage What Is Digital Clock In Vlsi It is used during the physical design process to evaluate and. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock In sta it is used for specifying the input and. What Is Digital Clock In Vlsi.

From vlsiconceptsforyou.blogspot.com

VLSI Concepts Different Types of Clock Tree Structure What Is Digital Clock In Vlsi Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. In sta it is used. What Is Digital Clock In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Digital Clock In Vlsi A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. The virtual clock, also known. What Is Digital Clock In Vlsi.

From nguyenquanicd.blogspot.com

[STA] Các thông số của clock trong phân tích timing VLSI TECHNOLOGY What Is Digital Clock In Vlsi It is used during the physical design process to evaluate and. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. The clock is a narrow pulse In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock.. What Is Digital Clock In Vlsi.

From vlsimaster.com

Generated Clock and Virtual Clock VLSI Master What Is Digital Clock In Vlsi It is used during the physical design process to evaluate and. In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. Inputs that come from other synchronous. What Is Digital Clock In Vlsi.

From candisqlorinda.pages.dev

Vlsi Soc 2024 Lok Nadya What Is Digital Clock In Vlsi The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. It is used during the physical design process to evaluate and. The clock is a narrow pulse In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock.. What Is Digital Clock In Vlsi.

From exobgkjhn.blob.core.windows.net

Timing Report Analysis In Vlsi at Peggy Simpson blog What Is Digital Clock In Vlsi Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. It is used during the physical design process to. What Is Digital Clock In Vlsi.

From www.youtube.com

Introduction to Clocks YouTube What Is Digital Clock In Vlsi In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock The clock is a narrow pulse It is used during the physical. What Is Digital Clock In Vlsi.

From exomtfjnf.blob.core.windows.net

What Is Clock Latency In Vlsi at Shelly Hines blog What Is Digital Clock In Vlsi The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. It is used during the physical design process to evaluate and. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock The clock is a narrow pulse By adopting synchronous design. What Is Digital Clock In Vlsi.

From www.youtube.com

Clock Distribution in Physical Design of VLSI YouTube What Is Digital Clock In Vlsi By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock In sta it is used for specifying the input and output delays signal coming from or going to a block that does. What Is Digital Clock In Vlsi.

From vlsitutorials.com

logicallyexclusiveclocksexample31 VLSI Tutorials What Is Digital Clock In Vlsi The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. It is used during the physical design process to evaluate and. By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. The clock is a narrow pulse A clock that is not connected to any pin or. What Is Digital Clock In Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru What Is Digital Clock In Vlsi By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. The clock is a narrow pulse The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system. What Is Digital Clock In Vlsi.

From www.youtube.com

Integrated Clock Gating Cell ICG Cell in VLSI Clock Gating Cell What Is Digital Clock In Vlsi A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. It is used during the. What Is Digital Clock In Vlsi.

From www.vlsijunction.com

VLSI Physical Design Clock Skew What Is Digital Clock In Vlsi It is used during the physical design process to evaluate and. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock The clock is a narrow pulse In sta it is used for specifying the input and output delays signal coming from or going to a block that. What Is Digital Clock In Vlsi.

From siliconvlsi.com

What do you mean by clock Jitter? Siliconvlsi What Is Digital Clock In Vlsi In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. It is used during the physical design process to evaluate and. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. The clock is a narrow pulse. What Is Digital Clock In Vlsi.

From teamvlsi.com

Integrated Clock Gating (ICG) Cell in VLSI Team VLSI What Is Digital Clock In Vlsi The clock is a narrow pulse In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual. What Is Digital Clock In Vlsi.

From vlsiuniverse.blogspot.com

Virtual clock STA VLSI n EDA What Is Digital Clock In Vlsi A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. It is used during the physical design process to evaluate and. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your. What Is Digital Clock In Vlsi.

From vlsitutorials.com

Onchip Clock Controller VLSI Tutorials What Is Digital Clock In Vlsi In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock By adopting synchronous design principles, engineers can create optimized circuits that meet. What Is Digital Clock In Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru What Is Digital Clock In Vlsi The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. Inputs that come from other synchronous systems are based on a different system clock, which is typically. What Is Digital Clock In Vlsi.

From www.physicaldesign4u.com

OCV (On Chip Variation) and CRPR (Clock Reconvergence Pessimism Removal What Is Digital Clock In Vlsi In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. Inputs. What Is Digital Clock In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Digital Clock In Vlsi It is used during the physical design process to evaluate and. In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. The virtual clock, also known as the. What Is Digital Clock In Vlsi.

From www.youtube.com

Pulse Synchronizer CDC Toggle Flop synchronization Fast to Slow What Is Digital Clock In Vlsi The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. Inputs that come from other synchronous systems are based on a different system clock,. What Is Digital Clock In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design What Is Digital Clock In Vlsi It is used during the physical design process to evaluate and. The clock is a narrow pulse By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. Inputs that come from other synchronous systems are based on. What Is Digital Clock In Vlsi.

From www.youtube.com

Clock Domain Crossing Handshake Synchronizer CDC Technique VLSI What Is Digital Clock In Vlsi The clock is a narrow pulse By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock In sta it is used for specifying the input and output delays signal coming from or. What Is Digital Clock In Vlsi.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch What Is Digital Clock In Vlsi In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your system clock The virtual clock, also known as the logical clock, is a representation. What Is Digital Clock In Vlsi.

From www.youtube.com

CDC Synchronizer 2 flop synchronizer Two flop synchronizer 2 stage What Is Digital Clock In Vlsi It is used during the physical design process to evaluate and. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. Inputs that come. What Is Digital Clock In Vlsi.

From vlsitutorials.com

generatedclocks VLSI Tutorials What Is Digital Clock In Vlsi It is used during the physical design process to evaluate and. A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a virtual clock. Inputs that come from other synchronous systems are based on a different system clock, which is typically asynchronous to your. What Is Digital Clock In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints What Is Digital Clock In Vlsi By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. The clock is a narrow pulse In sta it is used for specifying the input and output delays signal coming from or going to a block that does not contain any clock. Inputs that come from other synchronous systems are based on a different. What Is Digital Clock In Vlsi.

From vlsitutorials.com

multisyncclockdesign VLSI Tutorials What Is Digital Clock In Vlsi By adopting synchronous design principles, engineers can create optimized circuits that meet stringent timing requirements and. The virtual clock, also known as the logical clock, is a representation of the circuit’s timing behavior. A clock that is not connected to any pin or port logically to the design and also doesn’t exist physically in the design is known as a. What Is Digital Clock In Vlsi.