Esd Cell In Vlsi . Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. In the next part (vlsi: Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd (electrostatic discharge) is a common phenomenon that can cause significant. Esd is critical for electronic devices. In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Physical design (pd p3.2) —. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. As example, integrated circuits (ics) can be affected at silicon level by esd.

from medium.com

In the next part (vlsi: Esd is critical for electronic devices. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. As example, integrated circuits (ics) can be affected at silicon level by esd. Esd (electrostatic discharge) is a common phenomenon that can cause significant. Physical design (pd p3.2) —. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to.

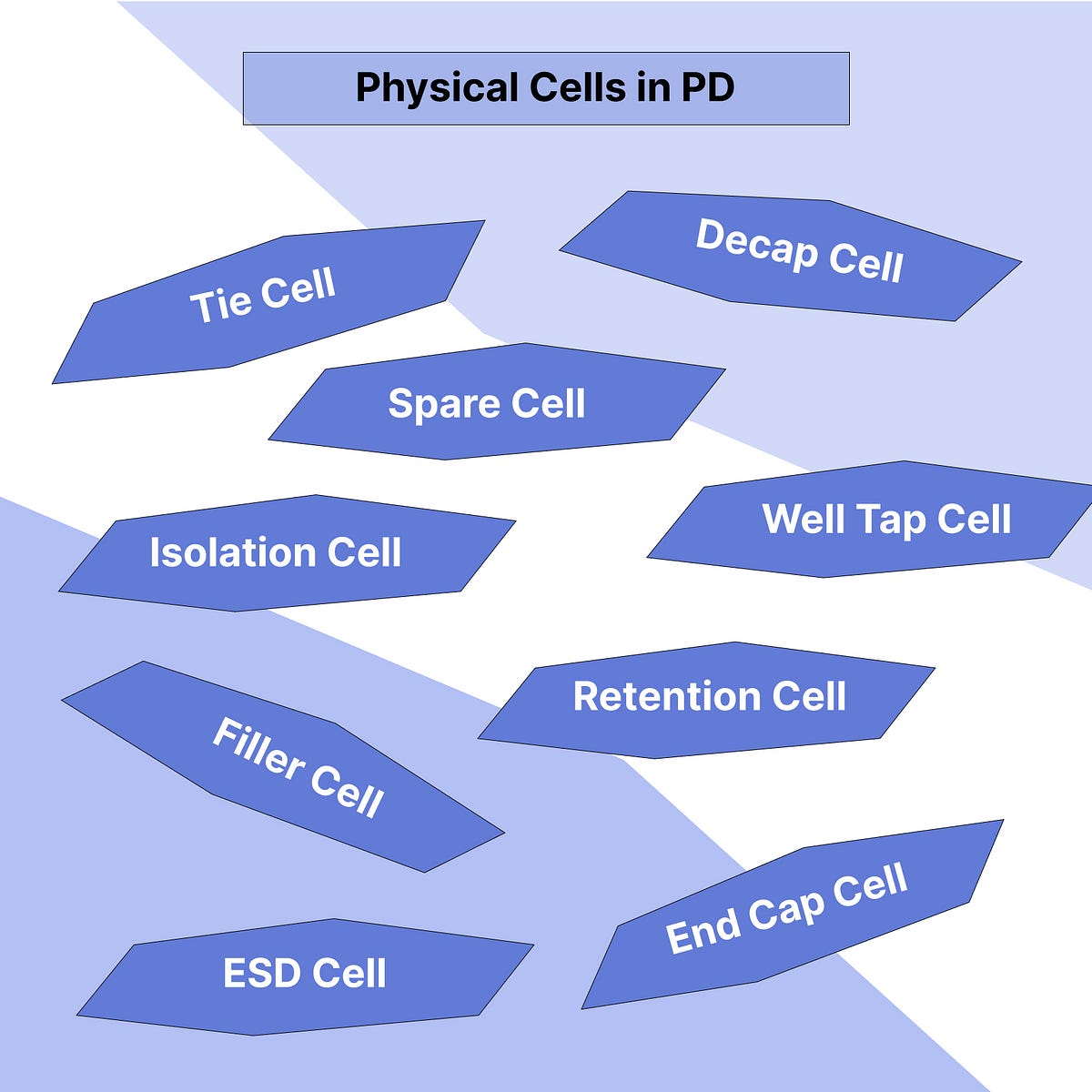

VLSI Physical Design (PD P3.2) — Physical Cells in PD by Kushagra

Esd Cell In Vlsi Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. In the next part (vlsi: Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Physical design (pd p3.2) —. As example, integrated circuits (ics) can be affected at silicon level by esd. Esd is critical for electronic devices. Esd (electrostatic discharge) is a common phenomenon that can cause significant. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell.

From www.mdpi.com

Electronics Free FullText A True ProcessHeterogeneous Stacked Esd Cell In Vlsi Esd is critical for electronic devices. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. In the next part (vlsi: As example, integrated circuits (ics) can be affected at silicon level by esd. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to.. Esd Cell In Vlsi.

From www.slideserve.com

PPT VLSI Digital System Design PowerPoint Presentation, free download Esd Cell In Vlsi Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Physical design (pd p3.2) —. Esd is critical for electronic devices. Esd (electrostatic discharge) is a common phenomenon that. Esd Cell In Vlsi.

From asic-soc.blogspot.kr

ASICSystem on ChipVLSI Design Standard cell based ASIC design Esd Cell In Vlsi In the next part (vlsi: Esd (electrostatic discharge) is a common phenomenon that can cause significant. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. In this article,. Esd Cell In Vlsi.

From semiengineering.com

How Robust Is Your ESD Protection? Are You Sure? Esd Cell In Vlsi Esd is critical for electronic devices. As example, integrated circuits (ics) can be affected at silicon level by esd. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. In this article, we will discuss the tie cell, endcap cell, decap cell, and. Esd Cell In Vlsi.

From www.bondline.co.uk

What Are the Common Sources of ESD Damage? Bondline Esd Cell In Vlsi Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Physical design (pd p3.2) —. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close.. Esd Cell In Vlsi.

From www.slideshare.net

Placement and routing in full custom physical design Esd Cell In Vlsi Esd (electrostatic discharge) is a common phenomenon that can cause significant. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Physical design (pd p3.2) —. Esd is critical for electronic devices. In the next part (vlsi: Esd occurs when two bodies at different potentials come in direct. Esd Cell In Vlsi.

From www.mdpi.com

Electronics Free FullText Layout Strengthening the ESD Performance Esd Cell In Vlsi Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. In the next part (vlsi: As example, integrated circuits (ics) can be affected at silicon level by esd. Esd is critical for electronic devices. In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Electro static discharge (esd) is sudden. Esd Cell In Vlsi.

From www.mdpi.com

Electronics Free FullText CDM Protection Test Structure for I/O Esd Cell In Vlsi Physical design (pd p3.2) —. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. Esd is critical for electronic devices. In the next part (vlsi: Electrostatic discharge (esd),. Esd Cell In Vlsi.

From medium.com

VLSI Physical Design (PD P3.2) — Physical Cells in PD by Kushagra Esd Cell In Vlsi Physical design (pd p3.2) —. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Esd (electrostatic discharge) is a common phenomenon that can cause significant. As example, integrated circuits (ics) can be affected at silicon level by esd. Esd occurs when two bodies at different potentials come. Esd Cell In Vlsi.

From siliconvlsi.com

What is ESD in VLSI? Siliconvlsi Esd Cell In Vlsi As example, integrated circuits (ics) can be affected at silicon level by esd. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd (electrostatic discharge) is a common phenomenon that can cause significant.. Esd Cell In Vlsi.

From siliconvlsi.com

Working of ESD Clamp Circuit in VLSI Siliconvlsi Esd Cell In Vlsi Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Esd is critical for electronic devices. Esd (electrostatic discharge) protection refers to the design techniques used to. Esd Cell In Vlsi.

From www.semanticscholar.org

Figure 13 from ESD failure mechanisms of analog I/O cells in 0.18/spl Esd Cell In Vlsi As example, integrated circuits (ics) can be affected at silicon level by esd. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Esd is critical for electronic devices. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged. Esd Cell In Vlsi.

From slidetodoc.com

Final Lesson ESD Summary VLSI Technologies ESD The Esd Cell In Vlsi Esd is critical for electronic devices. Physical design (pd p3.2) —. Esd (electrostatic discharge) is a common phenomenon that can cause significant. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. As example, integrated circuits (ics) can be affected at silicon level by esd. Electro static discharge (esd) is sudden flow of static electricity between. Esd Cell In Vlsi.

From www.youtube.com

Exploring the ESD Phenomenon in VLSI Causes, Effects, and Prevention Esd Cell In Vlsi In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. In the next part (vlsi: Physical design (pd p3.2) —. As example, integrated circuits (ics) can be affected at silicon level by esd. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between. Esd Cell In Vlsi.

From www.youtube.com

What Is Electrostatic Discharge (ESD)? YouTube Esd Cell In Vlsi As example, integrated circuits (ics) can be affected at silicon level by esd. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Electro static discharge (esd) is sudden. Esd Cell In Vlsi.

From www.semanticscholar.org

Figure 12 from ESD failure mechanisms of analog I/O cells in 0.18/spl Esd Cell In Vlsi Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. Esd is critical for electronic devices. In the next part (vlsi: Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between. Esd Cell In Vlsi.

From www.mdpi.com

Electronics Free FullText ESD Design and Analysis by Drain Esd Cell In Vlsi Physical design (pd p3.2) —. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. As example, integrated circuits (ics) can be affected at silicon level by. Esd Cell In Vlsi.

From www.mdpi.com

Electronics Free FullText Heterogeneous and Monolithic 3D Esd Cell In Vlsi Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd is critical for electronic devices. Physical design (pd p3.2) —. In the next part (vlsi: Esd occurs when two bodies at different potentials. Esd Cell In Vlsi.

From www.mdpi.com

Electronics Free FullText CDM Protection Test Structure for I/O Esd Cell In Vlsi Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Electrostatic discharge (esd), electrical overstress (eos), and latchup. Esd Cell In Vlsi.

From www.researchgate.net

Schematic of the lowpower and highspeed levelshifter [9] Download Esd Cell In Vlsi Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that. Esd Cell In Vlsi.

From cushychicken.github.io

NAND Flash device architecture overview pt 1 Esd Cell In Vlsi Esd is critical for electronic devices. In the next part (vlsi: In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Esd (electrostatic discharge) is a common phenomenon that can cause significant. Physical design (pd p3.2) —. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd (electrostatic discharge). Esd Cell In Vlsi.

From www.semanticscholar.org

Figure 3 from Design of ESD protection cell for dualband RF Esd Cell In Vlsi As example, integrated circuits (ics) can be affected at silicon level by esd. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Electro static discharge (esd) is sudden. Esd Cell In Vlsi.

From www.mdpi.com

Electronics Free FullText CDM Protection Test Structure for I/O Esd Cell In Vlsi In the next part (vlsi: Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. As example, integrated circuits (ics) can be affected at silicon level by esd. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. In this article, we will discuss. Esd Cell In Vlsi.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Package, Power, and I/O Esd Cell In Vlsi Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd is critical for electronic devices. Physical design (pd p3.2) —. As example, integrated circuits (ics) can be affected at silicon level by esd. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time.. Esd Cell In Vlsi.

From www.techsimplifiedtv.in

Electro Static Discharge in VLSI TechSimplifiedTV.in Esd Cell In Vlsi Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Physical design (pd p3.2) —. Esd is critical for electronic devices. Esd (electrostatic discharge) protection refers to the design. Esd Cell In Vlsi.

From www.youtube.com

Tie Cell in ASIC Design Use of Tie cell Schematic and Layout of Tie Esd Cell In Vlsi Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. Esd is critical for electronic devices. Esd (electrostatic discharge) is. Esd Cell In Vlsi.

From www.vlsi-expert.com

VLSI Concepts November 2014 Esd Cell In Vlsi Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Esd (electrostatic discharge) protection refers to the design techniques used to. Esd Cell In Vlsi.

From www.youtube.com

Exploring the Advanced LevelShifter Cell in VLSI A Comprehensive Esd Cell In Vlsi Esd (electrostatic discharge) is a common phenomenon that can cause significant. Esd is critical for electronic devices. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. In the next part (vlsi: Physical design (pd p3.2) —. As example, integrated circuits (ics) can be affected at silicon level. Esd Cell In Vlsi.

From www.mdpi.com

Electronics Free FullText The ESD Characteristics of a pMOS Esd Cell In Vlsi Esd (electrostatic discharge) is a common phenomenon that can cause significant. In the next part (vlsi: Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. As example, integrated circuits (ics) can be affected at silicon level by esd. Esd occurs when two bodies at different potentials come in direct contact or if there is a. Esd Cell In Vlsi.

From www.pcbaaa.com

Electrostatic discharge (ESD) protection in electronics IBE Electronics Esd Cell In Vlsi In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. In the next part (vlsi: Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Physical design (pd. Esd Cell In Vlsi.

From siliconvlsi.com

Working of ESD Clamp Circuit in VLSI Siliconvlsi Esd Cell In Vlsi Esd (electrostatic discharge) is a common phenomenon that can cause significant. Esd is critical for electronic devices. In the next part (vlsi: In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two. Esd Cell In Vlsi.

From www.youtube.com

VLSI Lecture7 CMOS Twin tub process YouTube Esd Cell In Vlsi In this article, we will discuss the tie cell, endcap cell, decap cell, and spare cell. Esd is critical for electronic devices. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Esd (electrostatic. Esd Cell In Vlsi.

From siliconvlsi.com

ESD Protection Guidelines Siliconvlsi Esd Cell In Vlsi Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. Esd is critical for electronic devices. Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in. Esd Cell In Vlsi.

From www.semanticscholar.org

Figure 3 from Overview on ESD protection design for mixedvoltage I/O Esd Cell In Vlsi Electrostatic discharge (esd), electrical overstress (eos), and latchup have been an issue in devices,. Esd occurs when two bodies at different potentials come in direct contact or if there is a high electrostatic field between two objects that are in close. Physical design (pd p3.2) —. As example, integrated circuits (ics) can be affected at silicon level by esd. Esd. Esd Cell In Vlsi.

From semiengineering.com

Scaling Bump Pitches In Advanced Packaging Esd Cell In Vlsi Physical design (pd p3.2) —. Esd is critical for electronic devices. Esd (electrostatic discharge) protection refers to the design techniques used to prevent damage to. Esd (electrostatic discharge) is a common phenomenon that can cause significant. Electro static discharge (esd) is sudden flow of static electricity between two electrically charged objects for a very short duration of time. Electrostatic discharge. Esd Cell In Vlsi.