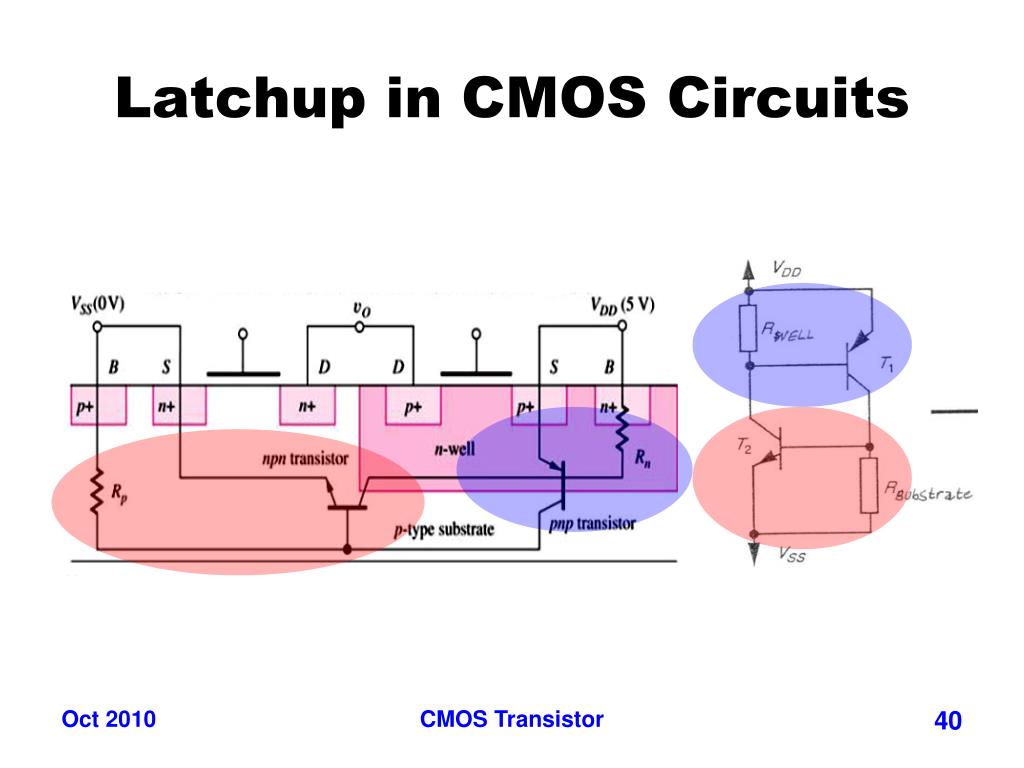

What Is Latch Up In Cmos . It resulted in circuits either malfunctioning or consuming. To understand latch up we need to understand. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and the parasitic components.

from www.slideserve.com

The above circuit shows a cmos inverter circuit and the parasitic components. Early cmos processes suffered a reliability concern that became known as latchup. To understand latch up we need to understand. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). It resulted in circuits either malfunctioning or consuming.

PPT CMOS Transistor and Circuits PowerPoint Presentation, free

What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. To understand latch up we need to understand. The above circuit shows a cmos inverter circuit and the parasitic components. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early cmos processes suffered a reliability concern that became known as latchup.

From www.youtube.com

Latch up in CMOS , Latch up in CMOS ,Latch up in VLSI Design, Latch up What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early cmos processes suffered a reliability concern that became known as latchup. To understand latch up we need to understand. The. What Is Latch Up In Cmos.

From www.studocu.com

Latchup in CMOS circuits CMOS Inverter The inverter is the very What Is Latch Up In Cmos To understand latch up we need to understand. It resulted in circuits either malfunctioning or consuming. Early cmos processes suffered a reliability concern that became known as latchup. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). The. What Is Latch Up In Cmos.

From buzztech.in

LatchUp Problem in CMOS VLSI Design Buzztech What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. The above circuit shows a cmos inverter circuit and the parasitic components. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). To understand latch up we need to understand. Early. What Is Latch Up In Cmos.

From www.scribd.com

LatchUp in CMOS PDF What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. To understand latch up we need to understand. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early cmos processes suffered a reliability concern that became. What Is Latch Up In Cmos.

From www.slideserve.com

PPT CMOS Transistor and Circuits PowerPoint Presentation, free What Is Latch Up In Cmos Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). It resulted in circuits either malfunctioning or consuming. To understand latch up we need to understand. Early cmos processes suffered a reliability concern that became known as latchup. The. What Is Latch Up In Cmos.

From siliconvlsi.com

Latchup in CMOS circuits Siliconvlsi What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. Early cmos processes suffered a reliability concern that became known as latchup. To understand latch up we need to understand. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From siliconvlsi.com

LatchUp Prevention Techniques Siliconvlsi What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early cmos processes suffered a reliability concern that became. What Is Latch Up In Cmos.

From www.youtube.com

LATCHUP IN CMOS CIRCUITS YouTube What Is Latch Up In Cmos Early cmos processes suffered a reliability concern that became known as latchup. It resulted in circuits either malfunctioning or consuming. The above circuit shows a cmos inverter circuit and the parasitic components. To understand latch up we need to understand. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From vlsi-soc.blogspot.com

VLSI SoC Design LatchUp in CMOS What Is Latch Up In Cmos To understand latch up we need to understand. Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and the parasitic components. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From www.youtube.com

Latch up in CMOS circuit Latch up Explore the way YouTube What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). It resulted in circuits either malfunctioning or consuming. To understand latch up we need to understand. Early. What Is Latch Up In Cmos.

From www.semanticscholar.org

Figure 6 from Unexpected LatchUp Through CMOS TripleWell Structures What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and the parasitic components. To understand latch up we need to understand. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From www.bilibili.com

Latch Up in CMOS, Latch up in CMOS Inverter, Latch up prevention steps What Is Latch Up In Cmos To understand latch up we need to understand. The above circuit shows a cmos inverter circuit and the parasitic components. It resulted in circuits either malfunctioning or consuming. Early cmos processes suffered a reliability concern that became known as latchup. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From www.youtube.com

What are Setup and Hold Times of a CMOS Latch? Explanation YouTube What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. Early cmos processes suffered a reliability concern that became known as latchup. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply). What Is Latch Up In Cmos.

From www.youtube.com

Understanding the CMOS LatchUp Phenomenon in VLSI What You Need to What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. To understand latch up we need to understand. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early. What Is Latch Up In Cmos.

From www.chegg.com

Solved b) The circuit diagram for CMOS Latchup is shown What Is Latch Up In Cmos Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). It resulted in circuits either malfunctioning or consuming. To understand latch up we need to understand. Early cmos processes suffered a reliability concern that became known as latchup. The. What Is Latch Up In Cmos.

From www.semanticscholar.org

Figure 1 from AN600 Understanding LatchUp in Advanced CMOS Logic What Is Latch Up In Cmos Early cmos processes suffered a reliability concern that became known as latchup. To understand latch up we need to understand. The above circuit shows a cmos inverter circuit and the parasitic components. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply). What Is Latch Up In Cmos.

From www.slideserve.com

PPT LatchUP PowerPoint Presentation, free download ID5779057 What Is Latch Up In Cmos To understand latch up we need to understand. The above circuit shows a cmos inverter circuit and the parasitic components. Early cmos processes suffered a reliability concern that became known as latchup. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply). What Is Latch Up In Cmos.

From www.semanticscholar.org

Figure 3 from Mechanism of snapback failure induced by the latchup What Is Latch Up In Cmos To understand latch up we need to understand. It resulted in circuits either malfunctioning or consuming. Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and the parasitic components. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From www.youtube.com

Latchup prevention in CMOS Various techniques for latchup What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. The above circuit shows a cmos inverter circuit and the parasitic components. Early cmos processes suffered a reliability concern that became known as latchup. To understand latch up we need to understand. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From anysilicon.com

What is LatchUp and How to Test It AnySilicon What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. The above circuit shows a cmos inverter circuit and the parasitic components. Early cmos processes suffered a reliability concern that became known as latchup. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply). What Is Latch Up In Cmos.

From www.edn.com

Power management can cause latchup in CMOS chips EDN What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and the parasitic components. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply). What Is Latch Up In Cmos.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Lecture 16 Circuit Pitfalls What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and the parasitic components. To understand latch up we need to understand. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From www.youtube.com

Latchup Prevention in CMOS/MOSFETs VLSI Design Dr. Sohaib A. Qazi What Is Latch Up In Cmos To understand latch up we need to understand. Early cmos processes suffered a reliability concern that became known as latchup. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). The. What Is Latch Up In Cmos.

From www.scribd.com

LATCH UP CMOS Inverter PDF Bipolar Junction Transistor Cmos What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). To understand latch up we need to understand. The above circuit shows a cmos inverter circuit and the parasitic components. Early. What Is Latch Up In Cmos.

From www.youtube.com

Latch up in CMOS circuits SCR VLSI Lec23 YouTube What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. The above circuit shows a cmos inverter circuit and the parasitic components. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early cmos processes suffered a reliability concern that became. What Is Latch Up In Cmos.

From studylib.net

LatchUp and its Prevention What Is Latch Up In Cmos To understand latch up we need to understand. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). The above circuit shows a cmos inverter circuit and the parasitic components. Early. What Is Latch Up In Cmos.

From www.researchgate.net

(PDF) Overview on LatchUp Prevention in CMOS Integrated Circuits by What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). To understand latch up we need to understand. Early. What Is Latch Up In Cmos.

From www.slideserve.com

PPT LatchUP PowerPoint Presentation, free download ID5779057 What Is Latch Up In Cmos To understand latch up we need to understand. It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early cmos processes suffered a reliability concern that became known as latchup. The. What Is Latch Up In Cmos.

From siliconvlsi.com

What is latchup in CMOS and its prevention Techniques Siliconvlsi What Is Latch Up In Cmos Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and the parasitic components. To understand latch up we need to understand. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply). What Is Latch Up In Cmos.

From www.semanticscholar.org

Figure 1.1 from TransientInduced Latchup in CMOS Integrated Circuits What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. Early cmos processes suffered a reliability concern that became known as latchup. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). The above circuit shows a cmos inverter circuit and. What Is Latch Up In Cmos.

From www.techsimplifiedtv.in

CMOS LatchUp TechSimplifiedTV.in What Is Latch Up In Cmos To understand latch up we need to understand. The above circuit shows a cmos inverter circuit and the parasitic components. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). It resulted in circuits either malfunctioning or consuming. Early. What Is Latch Up In Cmos.

From www.chegg.com

Figure 1 shows a CMOS latch design. In the inverter, What Is Latch Up In Cmos The above circuit shows a cmos inverter circuit and the parasitic components. To understand latch up we need to understand. It resulted in circuits either malfunctioning or consuming. Early cmos processes suffered a reliability concern that became known as latchup. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.

From mycodingclassmatenotebook.blogspot.com

VLSI (CMOS LATCH UP) What Is Latch Up In Cmos It resulted in circuits either malfunctioning or consuming. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and. What Is Latch Up In Cmos.

From www.youtube.com

What is CMOS tech. Latch up Triggering and Latch up Prevention YouTube What Is Latch Up In Cmos Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment of low resistance conducting path between vdd (supply) and gnd (ground). To understand latch up we need to understand. Early cmos processes suffered a reliability concern that became known as latchup. The above circuit shows a cmos inverter circuit and. What Is Latch Up In Cmos.

From www.scribd.com

VLSI SoC Design LatchUp in CMOS PDF Bipolar Junction Transistor What Is Latch Up In Cmos Early cmos processes suffered a reliability concern that became known as latchup. To understand latch up we need to understand. It resulted in circuits either malfunctioning or consuming. The above circuit shows a cmos inverter circuit and the parasitic components. Latchup is a condition in which the parasitic components such as pnp and npn transistors give rise to the establishment. What Is Latch Up In Cmos.