Scan Test Compression . As shown in figure 2, the. Fault coverage loss, pattern inflation, and area overhead. Scan compression was introduced in the year 2000 and has seen rapid adoption. Increased tdv is the result of a dependency. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. In this article, we focus on three fundamental performance metrics: Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression.

from www.vrogue.co

As shown in figure 2, the. Increased tdv is the result of a dependency. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. Scan compression was introduced in the year 2000 and has seen rapid adoption. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. Fault coverage loss, pattern inflation, and area overhead. Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. In this article, we focus on three fundamental performance metrics:

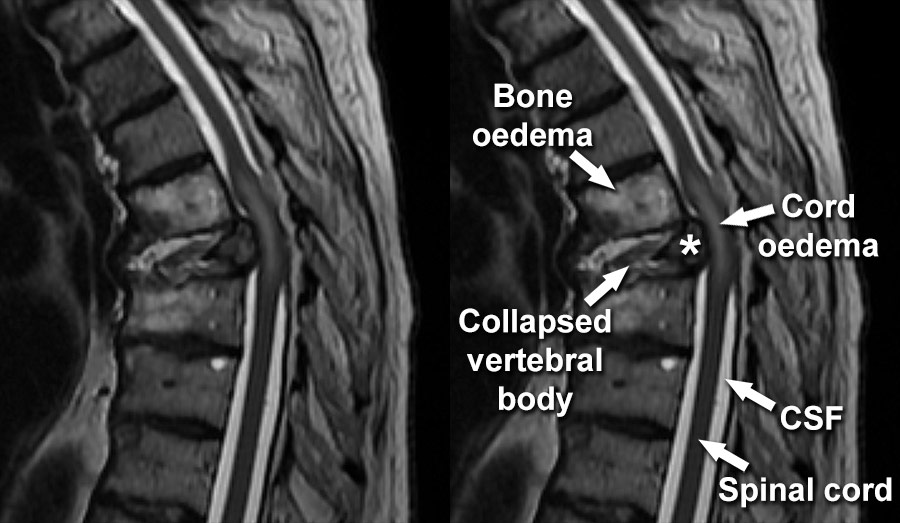

Imaging Of Spinal Cord Compression vrogue.co

Scan Test Compression In this article, we focus on three fundamental performance metrics: Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. Scan compression was introduced in the year 2000 and has seen rapid adoption. Fault coverage loss, pattern inflation, and area overhead. As shown in figure 2, the. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. Increased tdv is the result of a dependency. In this article, we focus on three fundamental performance metrics:

From semiengineering.com

Scan Compression Is No Longer About Compression Scan Test Compression Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough. Scan Test Compression.

From www.researchgate.net

Typical Laser Scanning Strategies. Left Traditional Contour Hatch Scan Test Compression Increased tdv is the result of a dependency. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. In this article, we focus on three fundamental performance metrics: By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester. Scan Test Compression.

From blogs.sw.siemens.com

A flexible flow for inserting embedded compression logic in RTL Scan Test Compression Scan compression was introduced in the year 2000 and has seen rapid adoption. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. As shown in figure 2, the. Increased tdv is the result of a dependency. Part 1 covers the concept of scan test,. Scan Test Compression.

From semiconshorts.com

Scan Compression Semicon Shorts Scan Test Compression Increased tdv is the result of a dependency. Scan compression was introduced in the year 2000 and has seen rapid adoption. In this article, we focus on three fundamental performance metrics: As shown in figure 2, the. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the. Scan Test Compression.

From blogs.sw.siemens.com

Get more from your test compression VersaPoint test point technology Scan Test Compression Fault coverage loss, pattern inflation, and area overhead. As shown in figure 2, the. In this article, we focus on three fundamental performance metrics: Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. By reducing the amount of data needed to thoroughly test digital. Scan Test Compression.

From eureka-patsnap-com.libproxy1.nus.edu.sg

Scanning test compression optimization method Eureka Patsnap Scan Test Compression In this article, we focus on three fundamental performance metrics: As shown in figure 2, the. Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests. Scan Test Compression.

From www.academia.edu

(PDF) Breaking the Test Application Time Barriers in Compression Scan Test Compression Increased tdv is the result of a dependency. Fault coverage loss, pattern inflation, and area overhead. In this article, we focus on three fundamental performance metrics: The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. As shown in figure 2, the. Part 1 covers the concept of scan test, scan. Scan Test Compression.

From www.electronicdesign.com

Combining Logic BIST and Scan Test Compression Electronic Design Scan Test Compression As shown in figure 2, the. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. In this article, we focus on three fundamental performance metrics:. Scan Test Compression.

From www.vrogue.co

Imaging Of Spinal Cord Compression vrogue.co Scan Test Compression By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Increased tdv is the result of a dependency. Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. In this article, we focus on three. Scan Test Compression.

From www.researchgate.net

Schematic of experimental equipment and process. a CT scanning system Scan Test Compression Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Increased tdv is the result of a dependency. Scan compression was introduced in. Scan Test Compression.

From www.researchgate.net

(PDF) A Low Power Test Data Compression Scheme for Scan Test Scan Test Compression Scan compression was introduced in the year 2000 and has seen rapid adoption. Increased tdv is the result of a dependency. Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. As shown in figure 2, the. In this article, we focus on three fundamental performance metrics: The test data volume (tdv) increases. Scan Test Compression.

From ietresearch.onlinelibrary.wiley.com

New scan compression approach to reduce the test data volume Scan Test Compression Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan. Scan Test Compression.

From www.electronicdesign.com

Combining Logic BIST and Scan Test Compression Electronic Design Scan Test Compression As shown in figure 2, the. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Scan compression was introduced in the year 2000 and has seen rapid adoption. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost.. Scan Test Compression.

From www.researchgate.net

(a) Schematic diagram of the in situ setup for compression tests on Scan Test Compression Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal. Scan Test Compression.

From slideplayer.com

Test Data Compression for ScanBased Testing ppt download Scan Test Compression Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. Increased tdv is the result of a dependency. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Tessent testkompress is the tool. Scan Test Compression.

From www.electronicdesign.com

Combining Logic BIST and Scan Test Compression Electronic Design Scan Test Compression Scan compression was introduced in the year 2000 and has seen rapid adoption. Increased tdv is the result of a dependency. Fault coverage loss, pattern inflation, and area overhead. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. Nearly every design’s test methodology today implements this technology, which inserts compression. Scan Test Compression.

From www.researchgate.net

A CT scan with contrast showing compression of right internal jugular Scan Test Compression Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough. Scan Test Compression.

From blogs.sw.siemens.com

Take scan test out of the critical path Tessent Solutions Scan Test Compression Fault coverage loss, pattern inflation, and area overhead. In this article, we focus on three fundamental performance metrics: Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to. Scan Test Compression.

From semiconshorts.com

Scan Compression Semicon Shorts Scan Test Compression As shown in figure 2, the. Increased tdv is the result of a dependency. Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. Fault coverage loss, pattern inflation, and. Scan Test Compression.

From eureka.patsnap.com

Scan string segmentation for digital test compression Eureka Scan Test Compression The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. As shown in figure 2, the. Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. Increased tdv is the result of a dependency. In this article, we focus on three fundamental performance metrics:. Scan Test Compression.

From blogs.sw.siemens.com

Scan ATPG and compression are beating Moore’s law Tessent Solutions Scan Test Compression Scan compression was introduced in the year 2000 and has seen rapid adoption. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,.. Scan Test Compression.

From www.researchgate.net

The typical reconstruction CT images for shale sample under in situ Scan Test Compression By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. In this article, we focus on three fundamental performance metrics: Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. Part 1 covers. Scan Test Compression.

From www.researchgate.net

(PDF) New scan compression approach to reduce the test data volume Scan Test Compression The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. In this article, we focus on three fundamental performance metrics: Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. By reducing the amount of data needed to. Scan Test Compression.

From www.researchgate.net

Scan synthesis and patterns generation for both scan compression and Scan Test Compression Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os. Scan Test Compression.

From ietresearch.onlinelibrary.wiley.com

New scan compression approach to reduce the test data volume Scan Test Compression Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. As shown in figure 2, the. Fault coverage loss, pattern inflation, and area overhead. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. In. Scan Test Compression.

From www.researchgate.net

Uniaxial testing of nB4C micropillars.(a Scan Test Compression The test data volume (tdv) increases with increased target compression in scan compression and adds to the test cost. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the. Scan Test Compression.

From mavink.com

Among Us Scan Scan Test Compression Fault coverage loss, pattern inflation, and area overhead. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. In this article, we focus on three fundamental performance metrics: Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks,. Scan Test Compression.

From www.electronicdesign.com

Combining Logic BIST and Scan Test Compression Electronic Design Scan Test Compression Scan compression was introduced in the year 2000 and has seen rapid adoption. In this article, we focus on three fundamental performance metrics: Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add. Scan Test Compression.

From www.youtube.com

Compression Test WITHOUT a COMPRESSION GAUGE using Active Scan Tool Scan Test Compression By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. Tessent testkompress is the tool that can generate the decompressor and compactor logic at the. Scan Test Compression.

From www.researchgate.net

(PDF) Adapting Scan Based Test Vector for Compression Method Based On Scan Test Compression Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. Scan compression was introduced in the year 2000 and has seen rapid adoption. Fault coverage loss, pattern inflation, and area overhead. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and. Scan Test Compression.

From www.researchgate.net

(PDF) Scan Compression Implementation in Industrial Design Case Study Scan Test Compression Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. Scan compression was introduced in the year 2000 and has seen rapid adoption. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. In this. Scan Test Compression.

From www.researchgate.net

(PDF) Improving test compression with scan feedforward techniques Scan Test Compression As shown in figure 2, the. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. Scan compression was introduced in the year 2000 and has seen rapid adoption. The test. Scan Test Compression.

From www.electronicdesign.com

Combining Logic BIST and Scan Test Compression Electronic Design Scan Test Compression Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains. As shown in figure 2, the. Tessent testkompress is the tool that can generate the decompressor and compactor logic at the rtl level. Scan compression was introduced in the year 2000 and has seen rapid. Scan Test Compression.

From www.electronicdesign.com

Combining Logic BIST and Scan Test Compression Electronic Design Scan Test Compression In this article, we focus on three fundamental performance metrics: Part 1 covers the concept of scan test, scan cell designs, full and partial scan, scan clocks, scan pattern generation and scan compression. As shown in figure 2, the. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests. Scan Test Compression.

From semiengineering.com

Scan Test Semiconductor Engineering Scan Test Compression Scan compression was introduced in the year 2000 and has seen rapid adoption. By reducing the amount of data needed to thoroughly test digital circuits, compression frees up enough tester memory to add tests (e.g.,. Nearly every design’s test methodology today implements this technology, which inserts compression logic in the scan path between the scan i/os and the internal chains.. Scan Test Compression.