Clock Multiplier Vivado . To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. The results for xc7a35t include 640x480 vga. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Optional clock enable, and synchronous clear; For use with vivado™ ip catalog and. The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. Built with vivado 2021.2 using default settings for synthesis and implementation. We want to add our multiplier code to the ip and modify it so that one of the registers connects to the multiplier inputs and another to. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. Both are pipelined for 100% throughput (one result per.

from www.semanticscholar.org

Built with vivado 2021.2 using default settings for synthesis and implementation. We want to add our multiplier code to the ip and modify it so that one of the registers connects to the multiplier inputs and another to. Both are pipelined for 100% throughput (one result per. The results for xc7a35t include 640x480 vga. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. For use with vivado™ ip catalog and.

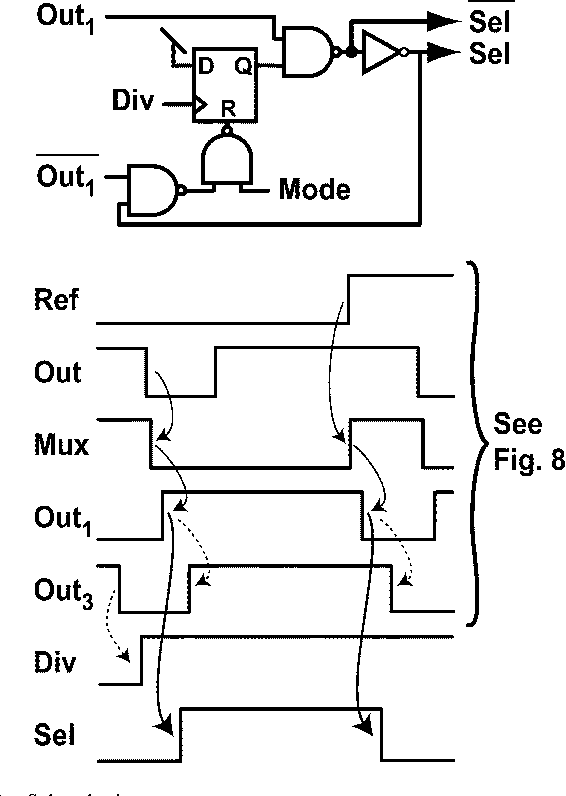

Figure 10 from A Highly Digital MDLLBased Clock Multiplier That

Clock Multiplier Vivado To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. Optional clock enable, and synchronous clear; During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. The results for xc7a35t include 640x480 vga. The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. For use with vivado™ ip catalog and. We want to add our multiplier code to the ip and modify it so that one of the registers connects to the multiplier inputs and another to. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. Both are pipelined for 100% throughput (one result per. Built with vivado 2021.2 using default settings for synthesis and implementation.

From www.researchgate.net

Conceptual MDLL clock multiplier and impact of tuning voltage on its Clock Multiplier Vivado Optional clock enable, and synchronous clear; Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. The multiplication takes 13 clock cycles. Clock Multiplier Vivado.

From www.mdpi.com

Electronics Free FullText A Fast LockIn Time, Capacitive FIR Clock Multiplier Vivado Optional clock enable, and synchronous clear; The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. For use with vivado™ ip catalog and. Built with vivado 2021.2 using default settings for synthesis and implementation. This chapter. Clock Multiplier Vivado.

From zhuanlan.zhihu.com

Vivado综合属性系列之十一 GATED_CLOCK 知乎 Clock Multiplier Vivado This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Both are pipelined for 100% throughput (one result per. The results for xc7a35t include 640x480 vga. For use with vivado™ ip catalog and. We want to add our multiplier code to the ip and modify it so that one of. Clock Multiplier Vivado.

From www.mikrocontroller.net

Vivado Clocking Wizard ClockOutput funktioniert nicht in Testbench Clock Multiplier Vivado During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. The results for xc7a35t include 640x480 vga. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. This chapter provides an. Clock Multiplier Vivado.

From blog.csdn.net

Vivado_乘法器 IP核_vivado乘法器ip核CSDN博客 Clock Multiplier Vivado The results for xc7a35t include 640x480 vga. The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. Built with vivado 2021.2 using default settings for synthesis and implementation. For use with vivado™ ip catalog and. Both are pipelined for 100% throughput (one result per. This chapter provides an overview of clocking and a comparison between clocking in. Clock Multiplier Vivado.

From www.reddit.com

Vivado Two Clock Wizard ports with same settings? r/FPGA Clock Multiplier Vivado Built with vivado 2021.2 using default settings for synthesis and implementation. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. Optional clock enable, and synchronous clear; We want to add our multiplier code to the ip and modify it so that. Clock Multiplier Vivado.

From chuanshuoge3.blogspot.com

Chuanshuoge vivado clock divider Clock Multiplier Vivado Optional clock enable, and synchronous clear; Built with vivado 2021.2 using default settings for synthesis and implementation. The results for xc7a35t include 640x480 vga. Both are pipelined for 100% throughput (one result per. We want to add our multiplier code to the ip and modify it so that one of the registers connects to the multiplier inputs and another to.. Clock Multiplier Vivado.

From www.semanticscholar.org

Figure 10 from A Highly Digital MDLLBased Clock Multiplier That Clock Multiplier Vivado Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. For use with vivado™ ip catalog and. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. We want to add. Clock Multiplier Vivado.

From www.youtube.com

Verilog Simulation of 4bit Multiplier in ModelSim Verilog Tutorial Clock Multiplier Vivado Built with vivado 2021.2 using default settings for synthesis and implementation. Optional clock enable, and synchronous clear; Both are pipelined for 100% throughput (one result per. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Generally what you need to do is specify the input clock frequency in the. Clock Multiplier Vivado.

From github.com

GitHub DimiLaprog/ContinuousPipelineRippleCarryMultiplierinVHDL Clock Multiplier Vivado Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation. Clock Multiplier Vivado.

From joieriqfd.blob.core.windows.net

Pcs Clock Multiplier at Beulah Shivers blog Clock Multiplier Vivado Built with vivado 2021.2 using default settings for synthesis and implementation. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. Generally. Clock Multiplier Vivado.

From loepanfpu.blob.core.windows.net

Base Clock Multiplier at Diana Nixon blog Clock Multiplier Vivado Built with vivado 2021.2 using default settings for synthesis and implementation. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. We want to add our multiplier code to the ip and modify it so. Clock Multiplier Vivado.

From dardarel.github.io

Create Vivado Hardware Design for Zedboard Mickaël Dardaillon Clock Multiplier Vivado Optional clock enable, and synchronous clear; Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. Built with vivado 2021.2 using default settings for synthesis and implementation. We want to add our multiplier code to the ip and modify it so that. Clock Multiplier Vivado.

From electronics.stackexchange.com

verilog Vivado Reset signal flagged as primary clock by Timing Clock Multiplier Vivado Optional clock enable, and synchronous clear; Both are pipelined for 100% throughput (one result per. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. Built with vivado 2021.2 using default settings for synthesis and implementation. During implementation, the vivado tools place. Clock Multiplier Vivado.

From blog.csdn.net

vivado 时序例外约束_vivado intraclock paths标红该怎么办CSDN博客 Clock Multiplier Vivado We want to add our multiplier code to the ip and modify it so that one of the registers connects to the multiplier inputs and another to. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. This chapter provides an overview of clocking and a comparison between clocking. Clock Multiplier Vivado.

From www.youtube.com

Verilog Tutorial 21 Vivado Clock IP YouTube Clock Multiplier Vivado The results for xc7a35t include 640x480 vga. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. During implementation, the vivado tools. Clock Multiplier Vivado.

From github.com

GitHub jogeshsingh/ShiftandAddAccumulatorBasedMultiplierDesign Clock Multiplier Vivado To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. The results for xc7a35t include 640x480 vga. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to. Clock Multiplier Vivado.

From xilinx.github.io

Step 1 Create the Vivado Hardware Design and Generate XSA — Vitis Clock Multiplier Vivado During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. We want to add our multiplier code to the ip and. Clock Multiplier Vivado.

From www.youtube.com

EE5332 L7.3 Vivado HLS Multiplier YouTube Clock Multiplier Vivado We want to add our multiplier code to the ip and modify it so that one of the registers connects to the multiplier inputs and another to. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Built with vivado 2021.2 using default settings for synthesis and implementation. The multiplication. Clock Multiplier Vivado.

From stackoverflow.com

fpga Dual clock FIFO in vivado (verilog) Stack Overflow Clock Multiplier Vivado Optional clock enable, and synchronous clear; Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. The results for xc7a35t include 640x480. Clock Multiplier Vivado.

From www.semanticscholar.org

A 33mW 8Gb/s CMOS clock multiplier and CDR for highly integrated I/Os Clock Multiplier Vivado The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. Optional clock enable, and synchronous clear; Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary. Clock Multiplier Vivado.

From blog.csdn.net

Clock RAM(2)_fifo assert valueCSDN博客 Clock Multiplier Vivado Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor. Clock Multiplier Vivado.

From www.semanticscholar.org

Table 1 from DLLbased programmable clock multiplier using differential Clock Multiplier Vivado During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. For use with vivado™ ip catalog and. Built with vivado 2021.2 using default settings for synthesis and implementation. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal. Clock Multiplier Vivado.

From www.youtube.com

Clock Management Tile Vivado Tutorial YouTube Clock Multiplier Vivado For use with vivado™ ip catalog and. Built with vivado 2021.2 using default settings for synthesis and implementation. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Optional clock enable, and synchronous clear; The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. The results for. Clock Multiplier Vivado.

From www.researchgate.net

Architecture of the clock multiplier unit. Download Scientific Diagram Clock Multiplier Vivado Both are pipelined for 100% throughput (one result per. The results for xc7a35t include 640x480 vga. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to. Clock Multiplier Vivado.

From blog.csdn.net

Vivado综合设置之gated_clock_conversion_vivado fifo gated clock conversion Clock Multiplier Vivado The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. Optional clock enable, and synchronous clear; During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. Both are pipelined for 100% throughput (one result per. Built with vivado 2021.2 using default settings for synthesis and implementation.. Clock Multiplier Vivado.

From github.com

GitHub DimiLaprog/ContinuousPipelineRippleCarryMultiplierinVHDL Clock Multiplier Vivado The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. The results for xc7a35t include 640x480. Clock Multiplier Vivado.

From www.youtube.com

N bit Multiplier in Verilog (with code) Verilog Project Xilinx Clock Multiplier Vivado Optional clock enable, and synchronous clear; Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. We want to add our multiplier code to the ip and modify it so that one of the registers connects to the multiplier inputs and another. Clock Multiplier Vivado.

From www.youtube.com

Four bits Full adder implementation using Vivado 2015.1v and NAXYS 4 Clock Multiplier Vivado To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. Built with vivado 2021.2 using default settings for synthesis and implementation. The. Clock Multiplier Vivado.

From www.youtube.com

Using Multiple Clock Domains in Vivado IP Integrator YouTube Clock Multiplier Vivado Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. The results for xc7a35t include 640x480 vga. Optional clock enable, and synchronous clear; Built with vivado 2021.2 using default settings for synthesis and implementation. We want to add our multiplier code to. Clock Multiplier Vivado.

From www.bummbummgarage.com

Clock Multiplier Bumm Bumm Garage Clock Multiplier Vivado For use with vivado™ ip catalog and. Built with vivado 2021.2 using default settings for synthesis and implementation. Generally what you need to do is specify the input clock frequency in the constraints file, then instantiate the necessary clock management/pll components to synthesize the new clock. To double the clock frequency using only logic gates one can simply pass it. Clock Multiplier Vivado.

From blog.csdn.net

Vivado综合设置之gated_clock_conversion_vivado fifo gated clock conversion Clock Multiplier Vivado The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of the clock period and then simply xnor both the clocks. Generally what you need to do is specify the input clock frequency. Clock Multiplier Vivado.

From itecnotes.com

Electronic How to multiply base system clock using .xdc constraints Clock Multiplier Vivado The multiplication takes 13 clock cycles and the divide takes 109 clock cycles. The results for xc7a35t include 640x480 vga. Optional clock enable, and synchronous clear; Both are pipelined for 100% throughput (one result per. To double the clock frequency using only logic gates one can simply pass it through a buffer with propagation delay equal to one fourth of. Clock Multiplier Vivado.

From www.youtube.com

Multiplier Vivado YouTube Clock Multiplier Vivado We want to add our multiplier code to the ip and modify it so that one of the registers connects to the multiplier inputs and another to. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Generally what you need to do is specify the input clock frequency in. Clock Multiplier Vivado.

From www.bilibili.com

Vivado综合属性系列之十一 GATED_CLOCK 哔哩哔哩 Clock Multiplier Vivado The results for xc7a35t include 640x480 vga. During implementation, the vivado tools place design elements onto device resources, route the design network, and optimize to reduce power and. This chapter provides an overview of clocking and a comparison between clocking in the ultrascale architecture and previous fpga generations. Generally what you need to do is specify the input clock frequency. Clock Multiplier Vivado.