Frequency Divider Counter Vhdl . You want to divide a clock of 24mhz, being 24000000 hz, to 1 hz. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. The frequency divider is a simple component which objective is to reduce the input frequency. So you create a counter that will count up every rising edge of the clkin (24. Integer range 0 to c_count_max :=. For example, for your case, the number of. Vhdl code consist of clock and reset input, divided clock as output. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock period has passed. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. A cleaner solution for a clock divider would be: The component is implemented through the use of the scaling factor and a. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock.

from www.edaboard.com

Vhdl code consist of clock and reset input, divided clock as output. A cleaner solution for a clock divider would be: The frequency divider is a simple component which objective is to reduce the input frequency. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock period has passed. So you create a counter that will count up every rising edge of the clkin (24. For example, for your case, the number of. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. Integer range 0 to c_count_max :=.

Frequency Divider in VHDL Forum for Electronics

Frequency Divider Counter Vhdl The frequency divider is a simple component which objective is to reduce the input frequency. Vhdl code consist of clock and reset input, divided clock as output. Integer range 0 to c_count_max :=. The component is implemented through the use of the scaling factor and a. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. The frequency divider is a simple component which objective is to reduce the input frequency. A cleaner solution for a clock divider would be: So you create a counter that will count up every rising edge of the clkin (24. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock period has passed. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. For example, for your case, the number of. You want to divide a clock of 24mhz, being 24000000 hz, to 1 hz.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Frequency Divider Counter Vhdl In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Integer range 0 to c_count_max :=. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Vhdl and verilog implementations for a clock frequency divider implemented at a. Frequency Divider Counter Vhdl.

From www.youtube.com

Frequency Divider Counters YouTube Frequency Divider Counter Vhdl Vhdl code consist of clock and reset input, divided clock as output. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. The component is implemented through the use of the scaling factor and a. Vhdl and verilog implementations for a clock frequency divider implemented. Frequency Divider Counter Vhdl.

From www.youtube.com

Counter as Frequency Divider Divided by Even integer (step by step Frequency Divider Counter Vhdl For example, for your case, the number of. Vhdl code consist of clock and reset input, divided clock as output. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock period has passed. If you generalize the clock divider by two, a smart and efficient divider is the. Frequency Divider Counter Vhdl.

From fixlibrarygedwaaldebx.z21.web.core.windows.net

Clock Divider Circuit Diagram Frequency Divider Counter Vhdl Vhdl code consist of clock and reset input, divided clock as output. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Clock. Frequency Divider Counter Vhdl.

From pgandhi189.blogspot.com

VLSI verification blogs Design of frequency divider using modulo Frequency Divider Counter Vhdl The frequency divider is a simple component which objective is to reduce the input frequency. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock period. Frequency Divider Counter Vhdl.

From www.scribd.com

VHDL Code For Clock Divider (Frequency Divider) PDF Vhdl Field Frequency Divider Counter Vhdl I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. For example, for your case, the number of. Integer range 0 to c_count_max :=. The. Frequency Divider Counter Vhdl.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Frequency Divider Counter Vhdl The frequency divider is a simple component which objective is to reduce the input frequency. Vhdl code consist of clock and reset input, divided clock as output. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. You want to divide a clock of 24mhz, being 24000000 hz, to 1 hz. For. Frequency Divider Counter Vhdl.

From mca-logicdesign.blogspot.com

Frequency Divider & Counters Frequency Divider Counter Vhdl The component is implemented through the use of the scaling factor and a. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. Integer range 0 to c_count_max :=. A cleaner solution for a clock divider would be: I wrote this code for dividing the clock an a nexys4 fpga that has. Frequency Divider Counter Vhdl.

From github.com

GitHub lincanbin/VHDLFrequencyDivider Quartus 9.0 Project of Frequency Divider Counter Vhdl The frequency divider is a simple component which objective is to reduce the input frequency. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. A cleaner solution for a clock divider would be: The second way is to use a counter to count the number of faster clock pulses until half. Frequency Divider Counter Vhdl.

From edu.svet.gob.gt

Frequency Divider Using 7490 Decade Counter Full Project Frequency Divider Counter Vhdl The component is implemented through the use of the scaling factor and a. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock. Frequency Divider Counter Vhdl.

From www.slideserve.com

PPT VHDL PowerPoint Presentation, free download ID226593 Frequency Divider Counter Vhdl So you create a counter that will count up every rising edge of the clkin (24. Integer range 0 to c_count_max :=. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The second way is to use a counter to count the number of faster clock pulses until half. Frequency Divider Counter Vhdl.

From www.youtube.com

Electronics clock frequency divide by 5 vhdl (2 Solutions!!) YouTube Frequency Divider Counter Vhdl I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. The component is. Frequency Divider Counter Vhdl.

From www.slideserve.com

PPT Integration of entities in VHDL PowerPoint Presentation, free Frequency Divider Counter Vhdl If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. A cleaner solution for a clock divider would be: The frequency divider is. Frequency Divider Counter Vhdl.

From robybunt.blogspot.com

Frequency Division and Counting Super Case Frequency Divider Counter Vhdl I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. Vhdl and verilog implementations for a clock frequency divider implemented at a component level. So you create a counter that will count up every rising edge of the clkin (24. The frequency divider is a. Frequency Divider Counter Vhdl.

From www.slideserve.com

PPT Integration of entities in VHDL PowerPoint Presentation, free Frequency Divider Counter Vhdl If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. A cleaner solution for a clock divider would be: Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. So you create a counter that will count up every rising. Frequency Divider Counter Vhdl.

From www.electroniclinic.com

How to design digital clock using counters decoders and displays Frequency Divider Counter Vhdl In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock. Frequency Divider Counter Vhdl.

From www.youtube.com

Frequency counter designed in VHDL on DE270 board YouTube Frequency Divider Counter Vhdl Vhdl code consist of clock and reset input, divided clock as output. You want to divide a clock of 24mhz, being 24000000 hz, to 1 hz. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. If you generalize the clock divider by two, a smart and efficient divider is. Frequency Divider Counter Vhdl.

From www.circuitdiagram.co

Frequency Divider Circuit Using Jk Flip Flop Circuit Diagram Frequency Divider Counter Vhdl For example, for your case, the number of. The component is implemented through the use of the scaling factor and a. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. The second way is to use a counter to count the number of faster. Frequency Divider Counter Vhdl.

From www.youtube.com

Counter as Frequency Divider Divided by Odd integer (step by step Frequency Divider Counter Vhdl Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. So you create a counter that will count up every rising edge of the clkin (24. Vhdl code consist of clock and reset input, divided clock as output. The frequency divider is a simple component which objective is to reduce the input. Frequency Divider Counter Vhdl.

From www.youtube.com

Electronics Quartus 2 VHDL Clock Frequency Divider can't determine Frequency Divider Counter Vhdl Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. For example, for your case, the number of. Vhdl code consist of clock and reset input, divided clock as output. You want. Frequency Divider Counter Vhdl.

From www.nu-tech.us

Integrated Circuit CMOS Frequency Divider/counter For VCR 8lead DIP Frequency Divider Counter Vhdl Vhdl and verilog implementations for a clock frequency divider implemented at a component level. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and. Frequency Divider Counter Vhdl.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL Frequency Divider Counter Vhdl I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. Vhdl code consist of clock and reset input, divided clock as output. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Vhdl. Frequency Divider Counter Vhdl.

From www.scribd.com

Frequency Divider Using VHDL PDF Field Programmable Gate Array Frequency Divider Counter Vhdl A cleaner solution for a clock divider would be: In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock period has passed. If you generalize the clock divider. Frequency Divider Counter Vhdl.

From www.numerade.com

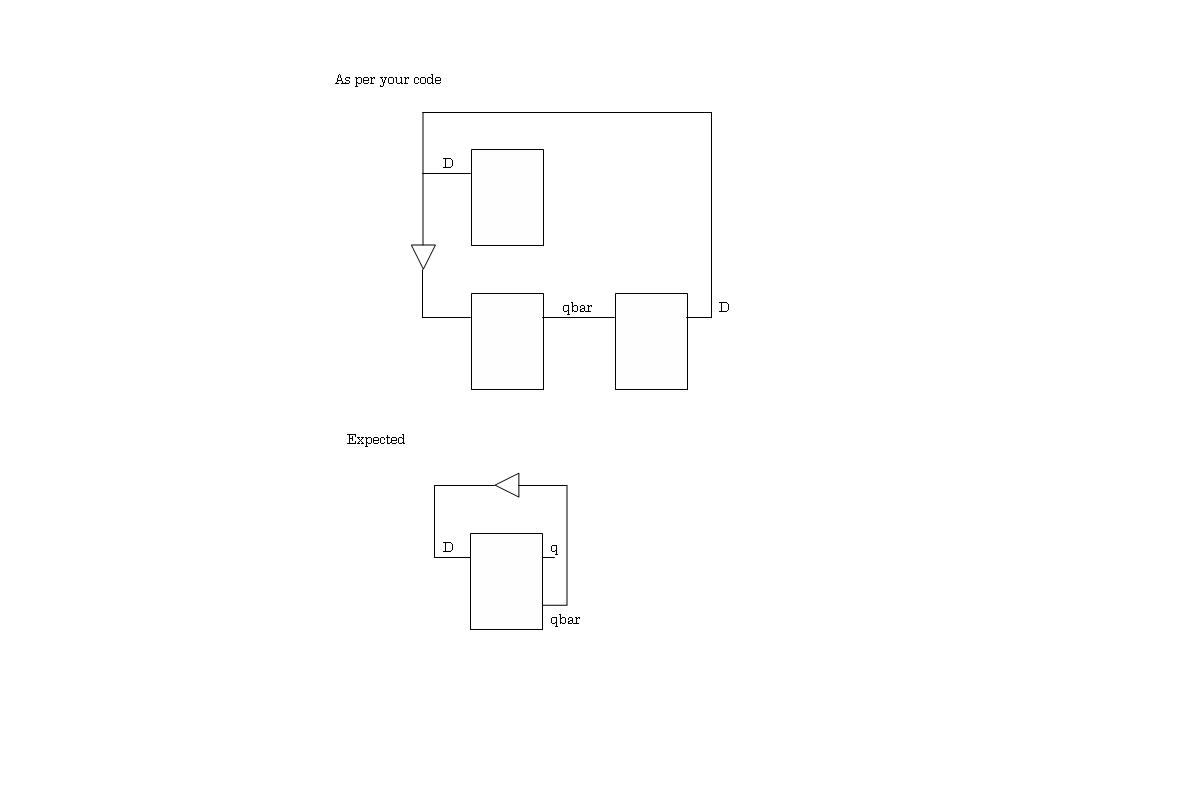

SOLVED need this written in VHDL please Figure 1 shows the circuit Frequency Divider Counter Vhdl In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Integer range 0 to c_count_max :=. A cleaner solution for a clock divider would be: If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. I wrote this. Frequency Divider Counter Vhdl.

From www.youtube.com

VHDL Lecture 24 Lab 8 Clock Divider and Counters Explanation YouTube Frequency Divider Counter Vhdl If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock period has passed. Vhdl and verilog implementations for a clock frequency divider implemented at a component. Frequency Divider Counter Vhdl.

From www.edn.com

VHDL code implements 50dutycycle divider EDN Frequency Divider Counter Vhdl If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. The frequency divider is a simple component which objective is to reduce the input frequency. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. So you create. Frequency Divider Counter Vhdl.

From www.circuitdiagram.co

Frequency Divider Circuit Using Jk Flip Flop Circuit Diagram Frequency Divider Counter Vhdl In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Vhdl code consist of clock and reset input, divided clock as output. The frequency divider is a simple. Frequency Divider Counter Vhdl.

From www.chegg.com

8bit frequency divider 1. Write a VHDL file or Frequency Divider Counter Vhdl A cleaner solution for a clock divider would be: Integer range 0 to c_count_max :=. You want to divide a clock of 24mhz, being 24000000 hz, to 1 hz. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. Clock divider is also known as. Frequency Divider Counter Vhdl.

From www.rfcafe.com

IC Frequency Dividers & Counters, January 1969 Electronics World RF Cafe Frequency Divider Counter Vhdl Vhdl and verilog implementations for a clock frequency divider implemented at a component level. For example, for your case, the number of. A cleaner solution for a clock divider would be: In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Clock divider is also known as frequency divider, which. Frequency Divider Counter Vhdl.

From www.cse.psu.edu

CMPEN 271 Homework Frequency Divider Counter Vhdl In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Integer range 0 to c_count_max :=. So you create a counter that will count up every rising edge of the clkin (24. The frequency divider is a simple component which objective is to reduce the input frequency. You want to. Frequency Divider Counter Vhdl.

From www.rfcafe.com

IC Frequency Dividers & Counters, January 1969 Electronics World RF Cafe Frequency Divider Counter Vhdl Vhdl code consist of clock and reset input, divided clock as output. A cleaner solution for a clock divider would be: You want to divide a clock of 24mhz, being 24000000 hz, to 1 hz. For example, for your case, the number of. The frequency divider is a simple component which objective is to reduce the input frequency. I wrote. Frequency Divider Counter Vhdl.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Frequency Divider Counter Vhdl In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Vhdl code consist of clock and reset input, divided clock as output. You want to divide a clock of 24mhz, being 24000000 hz, to 1 hz. The component is implemented through the use of the scaling factor and a. The. Frequency Divider Counter Vhdl.

From www.youtube.com

Frequency Divider Vhdl (Model sim) YouTube Frequency Divider Counter Vhdl I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. The frequency divider is a simple component which objective is to reduce the input frequency. Vhdl code consist of clock and reset input, divided clock as output. If you generalize the clock divider by two,. Frequency Divider Counter Vhdl.

From www.edaboard.com

Frequency Divider in VHDL Forum for Electronics Frequency Divider Counter Vhdl You want to divide a clock of 24mhz, being 24000000 hz, to 1 hz. A cleaner solution for a clock divider would be: For example, for your case, the number of. The second way is to use a counter to count the number of faster clock pulses until half of your slower clock period has passed. Vhdl code consist of. Frequency Divider Counter Vhdl.

From www.youtube.com

VHDL BASIC Tutorial Clock Divider YouTube Frequency Divider Counter Vhdl Integer range 0 to c_count_max :=. Vhdl code consist of clock and reset input, divided clock as output. So you create a counter that will count up every rising edge of the clkin (24. I wrote this code for dividing the clock an a nexys4 fpga that has its integrated clock at 100mhz frequency by default , and i. If. Frequency Divider Counter Vhdl.