What Is Patch Wire In Vlsi . A wire has high capacitance to. Vlsi design, fall 2020 10. The wire load model also maps the estimated length of. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. Wires cmos vlsi design 4th ed. One of the direction is considered as. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires.

from enfow.github.io

One of the direction is considered as. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. A wire has high capacitance to. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Vlsi design, fall 2020 10. The wire load model also maps the estimated length of. We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and.

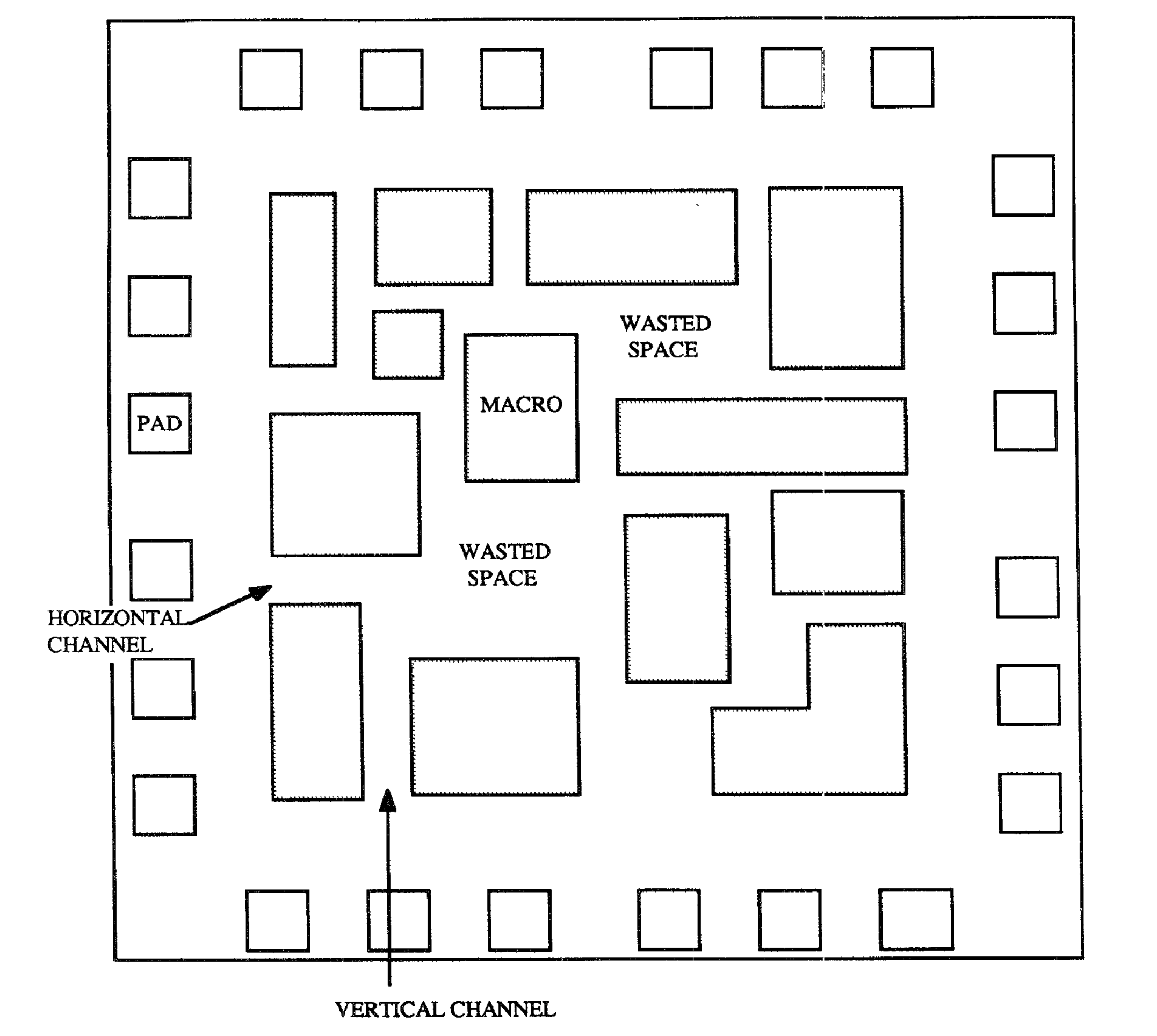

VLSI Cell Placement Technique · Enfow's Blog

What Is Patch Wire In Vlsi The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Wires cmos vlsi design 4th ed. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. One of the direction is considered as. Vlsi design, fall 2020 10. The wire load model also maps the estimated length of. A wire has high capacitance to. We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and.

From siliconvlsi.com

Types of Shielding in VLSI Siliconvlsi What Is Patch Wire In Vlsi The wire load model also maps the estimated length of. 21 crosstalk a capacitor does not like to change its voltage instantaneously. A wire has high capacitance to. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Vlsi interconnect issues are addressed in this book from a. What Is Patch Wire In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Net Delay or Interconnect Delay or What Is Patch Wire In Vlsi We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Interconnects in cmos technology 2 wire geometry pitch = w + s. What Is Patch Wire In Vlsi.

From www.youtube.com

VLSI Design Layout of Static CMOS Circuits YouTube What Is Patch Wire In Vlsi Vlsi design, fall 2020 10. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. Wires cmos vlsi design 4th ed. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. The wire load model depends upon the. What Is Patch Wire In Vlsi.

From siliconvlsi.com

What Is Routing In VLSI Physical Design? Siliconvlsi What Is Patch Wire In Vlsi Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. A wire. What Is Patch Wire In Vlsi.

From www.cbtnuggets.com

What is a Patch Panel, and What is It Used For? What Is Patch Wire In Vlsi One of the direction is considered as. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. Wires cmos vlsi design 4th ed. Vlsi design,. What Is Patch Wire In Vlsi.

From www.vlsi-expert.com

Metal Wire Orientation (HVH or VHV) VLSI Concepts What Is Patch Wire In Vlsi Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. A wire has high capacitance to. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. One of the direction is considered as. Lump wire resistance of each. What Is Patch Wire In Vlsi.

From teamx.emulationzone.org

VLSI Layout What Is Patch Wire In Vlsi 21 crosstalk a capacitor does not like to change its voltage instantaneously. One of the direction is considered as. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Lump wire resistance of each segment into a single r and the global capacitance into a single c •. What Is Patch Wire In Vlsi.

From enfow.github.io

VLSI Cell Placement Technique · Enfow's Blog What Is Patch Wire In Vlsi Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. A wire has high capacitance to. One of the direction is considered as. Lump wire resistance of each segment into a single r and the global. What Is Patch Wire In Vlsi.

From slidetodoc.com

Introduction to CMOS VLSI Design Lecture 6 Wires What Is Patch Wire In Vlsi 21 crosstalk a capacitor does not like to change its voltage instantaneously. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Vlsi design, fall 2020 10. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<<. What Is Patch Wire In Vlsi.

From www.slideserve.com

PPT VLSI Interconnects PowerPoint Presentation, free download ID What Is Patch Wire In Vlsi Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and. 21 crosstalk a capacitor does not like to change its voltage instantaneously.. What Is Patch Wire In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Wire load models What Is Patch Wire In Vlsi 21 crosstalk a capacitor does not like to change its voltage instantaneously. Wires cmos vlsi design 4th ed. We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. A wire has. What Is Patch Wire In Vlsi.

From www.slidemake.com

CMOS Inverter Using VLSI Presentation What Is Patch Wire In Vlsi One of the direction is considered as. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. 21 crosstalk a capacitor does not like to change its voltage instantaneously. A wire has high capacitance to. The wire load model also maps the estimated length of. Lump wire resistance of each segment into a single r and. What Is Patch Wire In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Wire load models for synthesis What Is Patch Wire In Vlsi Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. The wire load model also maps the estimated length of. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. We. What Is Patch Wire In Vlsi.

From www.slideserve.com

PPT VLSI Interconnects PowerPoint Presentation, free download ID What Is Patch Wire In Vlsi The wire load model also maps the estimated length of. A wire has high capacitance to. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Wires cmos vlsi design 4th ed. One of the direction is considered as. Lump wire resistance of each segment into a single r and the global capacitance into a single c •. What Is Patch Wire In Vlsi.

From present5.com

KLMH VLSI Physical Design From Graph Partitioning What Is Patch Wire In Vlsi 21 crosstalk a capacitor does not like to change its voltage instantaneously. A wire has high capacitance to. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal. What Is Patch Wire In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Wire load models for synthesis What Is Patch Wire In Vlsi Vlsi design, fall 2020 10. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. One of the direction is considered as. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. A wire has high capacitance to.. What Is Patch Wire In Vlsi.

From www.slideserve.com

PPT VLSI Interconnects PowerPoint Presentation, free download ID What Is Patch Wire In Vlsi Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. One of the direction is considered as. Wires cmos vlsi design 4th ed. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. We center. What Is Patch Wire In Vlsi.

From www.slideserve.com

PPT VLSI Interconnects PowerPoint Presentation, free download ID What Is Patch Wire In Vlsi Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Wires cmos vlsi design 4th ed. Vlsi interconnect issues are addressed in this book from. What Is Patch Wire In Vlsi.

From www.slideserve.com

PPT CSCI660 Introduction to VLSI Design PowerPoint Presentation What Is Patch Wire In Vlsi A wire has high capacitance to. Wires cmos vlsi design 4th ed. One of the direction is considered as. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. The wire load model also. What Is Patch Wire In Vlsi.

From backendesign.blogspot.com

VLSI Backend Design 2016 What Is Patch Wire In Vlsi We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. One of the direction is considered as. 21 crosstalk a capacitor does not like to. What Is Patch Wire In Vlsi.

From www.slideshare.net

Packaging of vlsi devices What Is Patch Wire In Vlsi Wires cmos vlsi design 4th ed. A wire has high capacitance to. Vlsi design, fall 2020 10. One of the direction is considered as. 21 crosstalk a capacitor does not like to change its voltage instantaneously. We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion,. What Is Patch Wire In Vlsi.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Interconnect wire PowerPoint What Is Patch Wire In Vlsi The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. Interconnects in cmos technology 2 wire geometry pitch = w + s. What Is Patch Wire In Vlsi.

From slidetodoc.com

Introduction to CMOS VLSI Design Lecture 6 Wires What Is Patch Wire In Vlsi One of the direction is considered as. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. Vlsi interconnect issues are addressed. What Is Patch Wire In Vlsi.

From technobyte.org

Introduction to JTAG Boundary Scan Structured techniques in DFT (VLSI) What Is Patch Wire In Vlsi We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Wires cmos vlsi design 4th ed. One of the direction is considered as. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's. What Is Patch Wire In Vlsi.

From dokumen.tips

(PPT) Lecture 14 Wires. CMOS VLSI DesignCMOS VLSI Design 4th Ed. 14 What Is Patch Wire In Vlsi We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Vlsi design, fall 2020 10. Wires cmos vlsi design 4th ed. The. What Is Patch Wire In Vlsi.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Interconnect wire PowerPoint What Is Patch Wire In Vlsi 21 crosstalk a capacitor does not like to change its voltage instantaneously. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. The wire load model also maps. What Is Patch Wire In Vlsi.

From www.studocu.com

VLSI6 Lecture notes 6 6 Wire s Introduction Interconnect What Is Patch Wire In Vlsi The wire load model also maps the estimated length of. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. Interconnects in cmos technology 2 wire geometry. What Is Patch Wire In Vlsi.

From www.vlsi-expert.com

Single VIA, VIA array, Stacked VIA VLSI Concepts What Is Patch Wire In Vlsi Vlsi design, fall 2020 10. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. 21 crosstalk a capacitor does not like to change its. What Is Patch Wire In Vlsi.

From www.slideserve.com

PPT ECE 681 VLSI Design Automation PowerPoint Presentation, free What Is Patch Wire In Vlsi 21 crosstalk a capacitor does not like to change its voltage instantaneously. Cross (perpendicular) metal wire orientation gives minimum capacitance and that's the reason it's recommended. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. Vlsi interconnect issues are addressed in this book from a design viewpoint,. What Is Patch Wire In Vlsi.

From www.youtube.com

𝐖𝐢𝐫𝐞 𝐋𝐨𝐚𝐝 𝐌𝐨𝐝𝐞𝐥 (𝐖𝐋𝐌) 𝐢𝐧 𝐒𝐓𝐀/𝐕𝐋𝐒𝐈 𝐰/ 𝐄𝐱𝐚𝐦𝐩𝐥𝐞𝐬 vlsiexcellence YouTube What Is Patch Wire In Vlsi One of the direction is considered as. Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout of metal wires. A wire has high capacitance to. Lump wire resistance of each. What Is Patch Wire In Vlsi.

From www.vlsi-expert.com

Single VIA, VIA array, Stacked VIA VLSI Concepts What Is Patch Wire In Vlsi Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. The wire load model also maps the estimated length of. Wires cmos vlsi design 4th. What Is Patch Wire In Vlsi.

From present5.com

KLMH VLSI Physical Design From Graph Partitioning What Is Patch Wire In Vlsi Interconnects in cmos technology 2 wire geometry pitch = w + s aspect ratio, ar = t/w old processes had ar<< 1. 21 crosstalk a capacitor does not like to change its voltage instantaneously. The wire load model also maps the estimated length of. One of the direction is considered as. A wire has high capacitance to. We center on. What Is Patch Wire In Vlsi.

From www.vlsi-expert.com

Single VIA, VIA array, Stacked VIA VLSI Concepts What Is Patch Wire In Vlsi Wires cmos vlsi design 4th ed. We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing, repeater insertion, and. 21 crosstalk a capacitor does not like to change its voltage instantaneously. Vlsi interconnect issues are addressed in this book from a design viewpoint, focusing primarily on the layout. What Is Patch Wire In Vlsi.

From vlsi.eelabs.technion.ac.il

DualBand Patch Antenna using Phase Change Material Based Switches VLSI What Is Patch Wire In Vlsi The wire load model also maps the estimated length of. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. Wires cmos vlsi design 4th ed. We center on global wiring layers (e.g., m4 and m5 in a 6lm process), and interconnect tuning issues related to bus routing,. What Is Patch Wire In Vlsi.

From www.vlsisystemdesign.com

VLSI System Design What Is Patch Wire In Vlsi Lump wire resistance of each segment into a single r and the global capacitance into a single c • this is called a. Vlsi design, fall 2020 10. The wire load model depends upon the area of the block, and designs with different areas may choose different wire load models. A wire has high capacitance to. The wire load model. What Is Patch Wire In Vlsi.