Signed Numbers Systemverilog . It seems like verilog is strongly inclined towards unsigned numbers. Any of the following yield an unsigned value: The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. If your design requires negative values, you need to handle signed numbers. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. %d, acc) it prints the unsigned. The bit values stay the same, subtraction and. I came across following problem while trying to understand how shift operators work with signed numbers in sv. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. Any operation on two operands,.

from verificationguide.com

Any of the following yield an unsigned value: I came across following problem while trying to understand how shift operators work with signed numbers in sv. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. %d, acc) it prints the unsigned. The bit values stay the same, subtraction and. Any operation on two operands,. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. If your design requires negative values, you need to handle signed numbers. It seems like verilog is strongly inclined towards unsigned numbers.

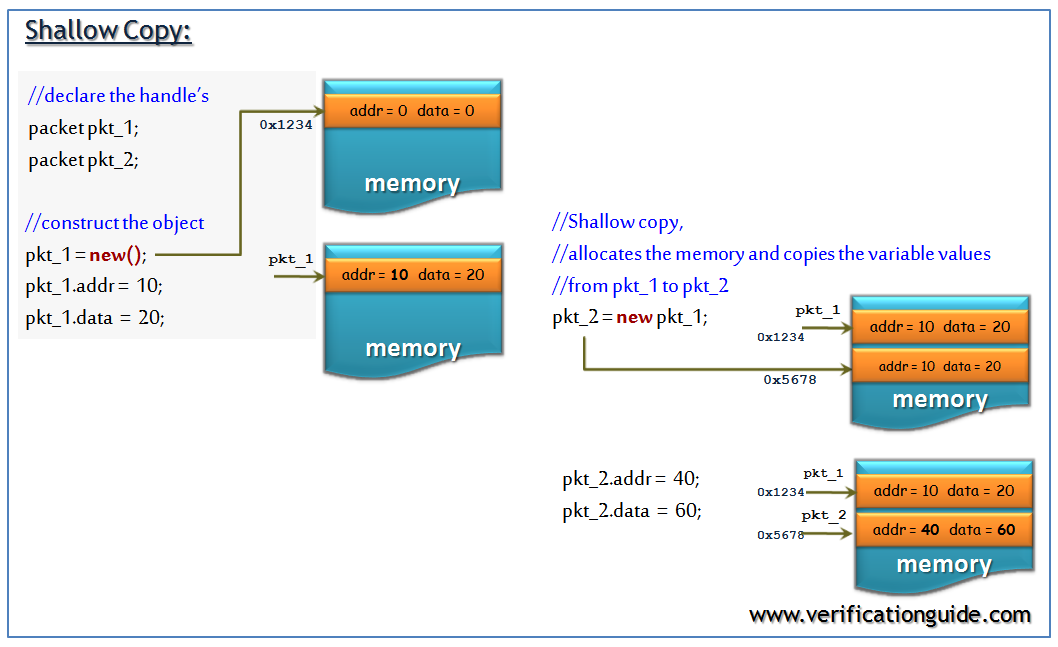

SystemVerilog Shallow Copy Verification Guide

Signed Numbers Systemverilog Any operation on two operands,. If your design requires negative values, you need to handle signed numbers. It seems like verilog is strongly inclined towards unsigned numbers. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. I came across following problem while trying to understand how shift operators work with signed numbers in sv. Any operation on two operands,. The bit values stay the same, subtraction and. %d, acc) it prints the unsigned. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. Any of the following yield an unsigned value: The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern.

From github.com

GitHub parnabghosh1004/BoothMultiplierinVerilog Implementation of booth's multiplier Signed Numbers Systemverilog The bit values stay the same, subtraction and. %d, acc) it prints the unsigned. Any of the following yield an unsigned value: If your design requires negative values, you need to handle signed numbers. I came across following problem while trying to understand how shift operators work with signed numbers in sv. Any operation on two operands,. Not only is. Signed Numbers Systemverilog.

From www.electronics-lab.com

Electronic Projects, Embedded News and Online Community ElectronicsLab Signed Numbers Systemverilog I came across following problem while trying to understand how shift operators work with signed numbers in sv. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. The bit values stay the same, subtraction and. In verilog a reg contains binary data, signed unsigned are just a matter. Signed Numbers Systemverilog.

From community.element14.com

SystemVerilog Study Notes. GateLevel Combinational Circuit element14 Community Signed Numbers Systemverilog I came across following problem while trying to understand how shift operators work with signed numbers in sv. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. Any operation on two operands,. If your design requires negative values, you need to handle signed numbers. The bit values stay. Signed Numbers Systemverilog.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 17 Assertion and Property YouTube Signed Numbers Systemverilog Any operation on two operands,. The bit values stay the same, subtraction and. %d, acc) it prints the unsigned. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. I came across following problem while trying to understand how shift operators work with signed numbers in sv. In verilog. Signed Numbers Systemverilog.

From www.chegg.com

Solved Design a multiplier that will multiply two 16bit signed b... Signed Numbers Systemverilog If your design requires negative values, you need to handle signed numbers. I came across following problem while trying to understand how shift operators work with signed numbers in sv. Any of the following yield an unsigned value: The bit values stay the same, subtraction and. It seems like verilog is strongly inclined towards unsigned numbers. The numeric literals 8'sd244. Signed Numbers Systemverilog.

From www.semanticscholar.org

Figure 7 from Design of a SystemVerilogBased SigmaDelta ADC Real Number Model Semantic Scholar Signed Numbers Systemverilog If your design requires negative values, you need to handle signed numbers. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. Any operation on two operands,. The bit values stay the same, subtraction and. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. Any. Signed Numbers Systemverilog.

From www.semanticscholar.org

Design of a Digital PLL Real Number Model Using SystemVerilog Semantic Scholar Signed Numbers Systemverilog In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. Any of the following yield an unsigned value: It seems like verilog is strongly inclined towards unsigned numbers. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. The bit values stay the same, subtraction and.. Signed Numbers Systemverilog.

From eclipse.umbc.edu

Lecture 16 Signed Integers and Integer Arithmetic Signed Numbers Systemverilog The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. Any of the following yield an unsigned value: %d, acc) it prints the unsigned. I came across following problem while trying to understand how shift operators work with signed numbers in sv. In verilog a reg contains binary data, signed unsigned. Signed Numbers Systemverilog.

From slideplayer.com

Lecture 2 Continuation of SystemVerilog ppt download Signed Numbers Systemverilog In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. The bit values stay the same, subtraction and. It seems like verilog is strongly inclined towards unsigned numbers. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. %d, acc) it prints the unsigned.. Signed Numbers Systemverilog.

From blog.csdn.net

systemVerilog操作符及语法_use systemverilog mode insteadCSDN博客 Signed Numbers Systemverilog If your design requires negative values, you need to handle signed numbers. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. The bit values stay the same, subtraction and. Any of the following yield an unsigned value: It seems like verilog is strongly inclined towards unsigned numbers. %d,. Signed Numbers Systemverilog.

From www.youtube.com

Declare signed numbers in Verilog (3 Solutions!!) YouTube Signed Numbers Systemverilog The bit values stay the same, subtraction and. %d, acc) it prints the unsigned. If your design requires negative values, you need to handle signed numbers. It seems like verilog is strongly inclined towards unsigned numbers. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. Not only is a number. Signed Numbers Systemverilog.

From www.slideserve.com

PPT Number Systems PowerPoint Presentation, free download ID5580001 Signed Numbers Systemverilog The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. Any of the following yield an unsigned value: In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. I came across following problem while trying to understand how shift operators work with signed numbers in sv.. Signed Numbers Systemverilog.

From www.slideserve.com

PPT Signed Numbers PowerPoint Presentation, free download ID6867650 Signed Numbers Systemverilog Any of the following yield an unsigned value: The bit values stay the same, subtraction and. I came across following problem while trying to understand how shift operators work with signed numbers in sv. If your design requires negative values, you need to handle signed numbers. %d, acc) it prints the unsigned. Any operation on two operands,. It seems like. Signed Numbers Systemverilog.

From www.youtube.com

Binary Multiplier Circuit for Signed Numbers Explained YouTube Signed Numbers Systemverilog Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. Any operation on two operands,. Any of the following yield an unsigned value: In verilog a reg contains binary data,. Signed Numbers Systemverilog.

From zhuanlan.zhihu.com

SystemVerilog中的有符号数据类型 知乎 Signed Numbers Systemverilog %d, acc) it prints the unsigned. It seems like verilog is strongly inclined towards unsigned numbers. I came across following problem while trying to understand how shift operators work with signed numbers in sv. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. If your design requires negative. Signed Numbers Systemverilog.

From www.youtube.com

Course Systemverilog Verification 1 L3.2 Numbers in Systemverilog YouTube Signed Numbers Systemverilog Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. The bit values stay the same, subtraction and. %d, acc) it prints the unsigned. I came across following problem while. Signed Numbers Systemverilog.

From www.semanticscholar.org

Design of a SystemVerilogBased VCO Real Number Model Semantic Scholar Signed Numbers Systemverilog The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. %d, acc) it prints the unsigned. In verilog a reg contains binary data, signed unsigned are just a matter of. Signed Numbers Systemverilog.

From www.youtube.com

Multiplying and Dividing Signed Numbers YouTube Signed Numbers Systemverilog The bit values stay the same, subtraction and. %d, acc) it prints the unsigned. Any operation on two operands,. Any of the following yield an unsigned value: The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. If your design requires negative values, you need to handle signed numbers. I came. Signed Numbers Systemverilog.

From electronics.stackexchange.com

Declare signed numbers in Verilog Electrical Engineering Stack Exchange Signed Numbers Systemverilog %d, acc) it prints the unsigned. If your design requires negative values, you need to handle signed numbers. Any of the following yield an unsigned value: Any operation on two operands,. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. It seems like verilog is strongly inclined towards unsigned numbers.. Signed Numbers Systemverilog.

From www.youtube.com

System Verilog tutorial Combinational logic design coding AND OR NAND NOR XOR XNOR logic Signed Numbers Systemverilog %d, acc) it prints the unsigned. The bit values stay the same, subtraction and. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. Any operation on two operands,. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. It seems like verilog is. Signed Numbers Systemverilog.

From electronics.stackexchange.com

Declare signed numbers in Verilog Electrical Engineering Stack Exchange Signed Numbers Systemverilog Any of the following yield an unsigned value: The bit values stay the same, subtraction and. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. Any operation on two operands,. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. %d, acc) it prints the. Signed Numbers Systemverilog.

From verificationguide.com

SystemVerilog Shallow Copy Verification Guide Signed Numbers Systemverilog In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. If your design requires negative values, you need to handle signed numbers. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. %d, acc) it prints the unsigned. Any of the following yield an unsigned value:. Signed Numbers Systemverilog.

From www.youtube.com

Electronics Signed representation of negative numbers in Verilog HDL by Samir Palnitkar YouTube Signed Numbers Systemverilog Any of the following yield an unsigned value: Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. If your design requires negative values, you need to handle signed numbers. The numeric literals 8'sd244. Signed Numbers Systemverilog.

From www.chegg.com

Solved 1. You are given the following System Verilog code of Signed Numbers Systemverilog It seems like verilog is strongly inclined towards unsigned numbers. If your design requires negative values, you need to handle signed numbers. Any of the following yield an unsigned value: Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. The numeric literals 8'sd244 and 8'd244 both represent the. Signed Numbers Systemverilog.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 09a Function and Task Argument Direction YouTube Signed Numbers Systemverilog In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. %d, acc) it prints the unsigned. It seems like verilog is strongly inclined towards unsigned numbers. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. I came across following problem while trying to understand how. Signed Numbers Systemverilog.

From verificationguide.com

SystemVerilog Class Constructors Verification Guide Signed Numbers Systemverilog The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. The bit values stay the same, subtraction and. I came across following problem while trying to understand how shift operators work with signed numbers in sv. It seems like verilog is strongly inclined towards unsigned numbers. Not only is a number. Signed Numbers Systemverilog.

From www.chipverify.com

SystemVerilog Strings Signed Numbers Systemverilog %d, acc) it prints the unsigned. I came across following problem while trying to understand how shift operators work with signed numbers in sv. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. The bit values stay the same, subtraction and. Any of the following yield an unsigned value: Any. Signed Numbers Systemverilog.

From stackoverflow.com

How does Verilog behave with negative numbers? Stack Overflow Signed Numbers Systemverilog The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. The bit values stay the same, subtraction and. It seems like verilog is strongly inclined towards unsigned numbers. %d, acc) it prints the unsigned. If your design requires negative values, you need to handle signed numbers. Any of the following yield. Signed Numbers Systemverilog.

From zhuanlan.zhihu.com

System Verilog中的整数数据类型 知乎 Signed Numbers Systemverilog The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. If your design requires negative values, you need to handle signed numbers. Any operation on two operands,. Any of the following yield an unsigned value: Not. Signed Numbers Systemverilog.

From courses.cs.washington.edu

Verilog Numbers Signed Numbers Systemverilog Any of the following yield an unsigned value: Any operation on two operands,. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. If your design requires negative values, you need to handle signed numbers. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. Not. Signed Numbers Systemverilog.

From studylib.net

verilog number literals Signed Numbers Systemverilog The bit values stay the same, subtraction and. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. If your design requires negative values, you need to handle signed numbers. The numeric literals 8'sd244 and 8'd244 both represent the same bit pattern 8'b11110100 (or `8'hf4), and that's the pattern. Not only is a number with. Signed Numbers Systemverilog.

From www.youtube.com

Signed Numbers Digital Logic Design I YouTube Signed Numbers Systemverilog %d, acc) it prints the unsigned. It seems like verilog is strongly inclined towards unsigned numbers. Any operation on two operands,. Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. Any of the. Signed Numbers Systemverilog.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download ID6034709 Signed Numbers Systemverilog Any operation on two operands,. The bit values stay the same, subtraction and. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. Any of the following yield an unsigned value: I came across following problem while trying to understand how shift operators work with signed numbers in sv. It seems like verilog is strongly. Signed Numbers Systemverilog.

From www.learnuvmverification.com

Quick Reference SystemVerilog Data Types Universal Verification Methodology Signed Numbers Systemverilog Any of the following yield an unsigned value: The bit values stay the same, subtraction and. It seems like verilog is strongly inclined towards unsigned numbers. In verilog a reg contains binary data, signed unsigned are just a matter of interpretation. I came across following problem while trying to understand how shift operators work with signed numbers in sv. If. Signed Numbers Systemverilog.

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation ID1302902 Signed Numbers Systemverilog Not only is a number with a base format 6’o54 considered unsigned, but mixing signed an unsigned types in an expression. Any of the following yield an unsigned value: It seems like verilog is strongly inclined towards unsigned numbers. If your design requires negative values, you need to handle signed numbers. In verilog a reg contains binary data, signed unsigned. Signed Numbers Systemverilog.