Clock Skew And Clock Jitter In Vlsi . Any signal takes some time to. In a clock path skew and jitter are the unwanted phenomena that should b. These clock sources should maintain regular clock cycles with clean edges. Clock skew and jitter are the essential topics to understand in vlsi timing closure. If possible, route data and clock in opposite. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop.

from siliconvlsi.com

Any signal takes some time to. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. Clock skew and jitter are the essential topics to understand in vlsi timing closure. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. If possible, route data and clock in opposite. In a clock path skew and jitter are the unwanted phenomena that should b. These clock sources should maintain regular clock cycles with clean edges. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals.

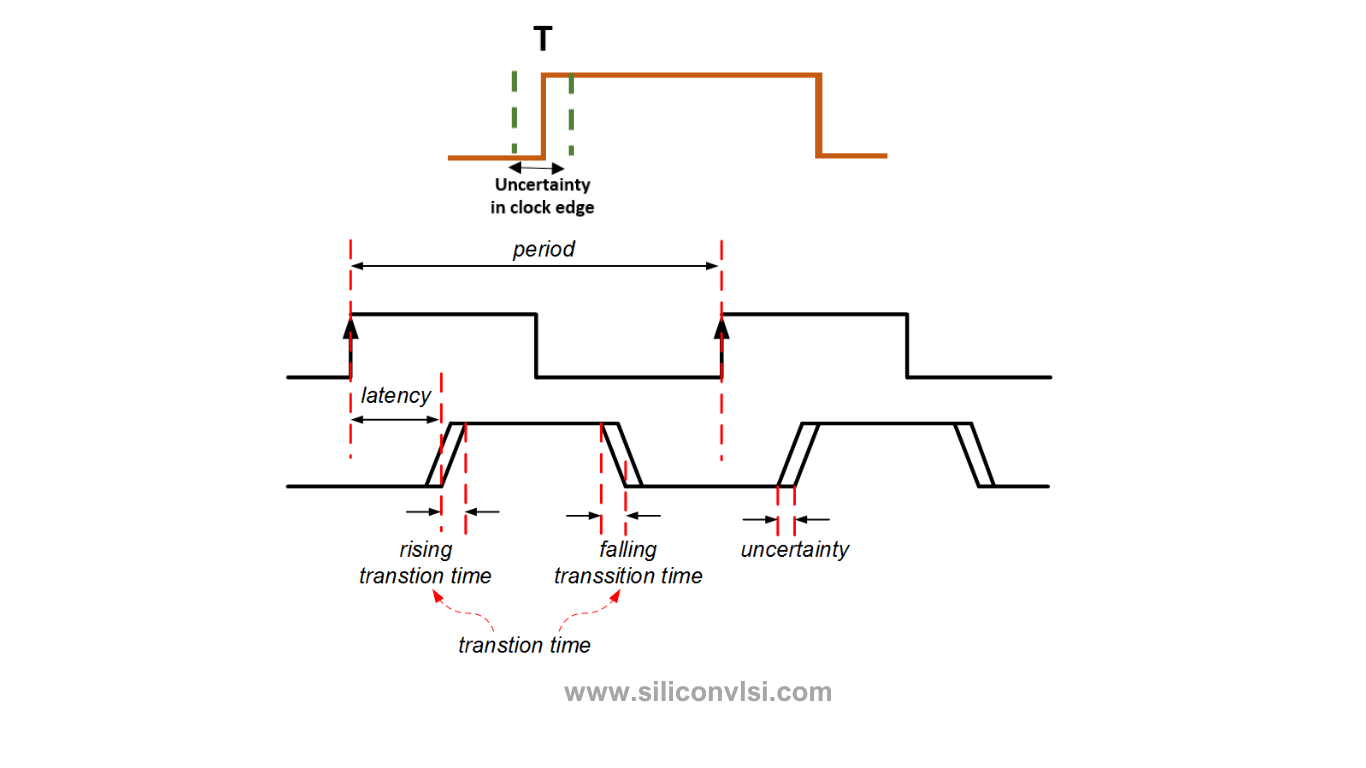

Difference Between Clock Skew and Uncertainty Siliconvlsi

Clock Skew And Clock Jitter In Vlsi These clock sources should maintain regular clock cycles with clean edges. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. In a clock path skew and jitter are the unwanted phenomena that should b. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. Any signal takes some time to. These clock sources should maintain regular clock cycles with clean edges. Clock skew and jitter are the essential topics to understand in vlsi timing closure. If possible, route data and clock in opposite. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop.

From design4silicon.blogspot.com

VLSI Design Overview and Questionnaires Basics of Setup and Hold Part 2 Clock Skew And Clock Jitter In Vlsi Clock skew and jitter are the essential topics to understand in vlsi timing closure. If possible, route data and clock in opposite. These clock sources should maintain regular clock cycles with clean edges. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. Clock. Clock Skew And Clock Jitter In Vlsi.

From www.slideserve.com

PPT Signal and Timing Parameters I Common Clock Class 2 PowerPoint Clock Skew And Clock Jitter In Vlsi These clock sources should maintain regular clock cycles with clean edges. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Skew is defined as the difference between the arrival time. Clock Skew And Clock Jitter In Vlsi.

From www.eeworldonline.com

Application relevance of clock jitter Electrical Engineering News and Clock Skew And Clock Jitter In Vlsi In a clock path skew and jitter are the unwanted phenomena that should b. If possible, route data and clock in opposite. Clock skew and jitter are the essential topics to understand in vlsi timing closure. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. Clock skew, in simple terms, is. Clock Skew And Clock Jitter In Vlsi.

From pt.slideshare.net

Clock jitter Clock Skew And Clock Jitter In Vlsi In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. If possible, route data and clock in opposite. In a clock path skew and jitter are the unwanted phenomena that should b. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data. Clock Skew And Clock Jitter In Vlsi.

From www.researchgate.net

Jitter tolerance for varying clocktodata skew (a) at 200 ps (b Clock Skew And Clock Jitter In Vlsi If possible, route data and clock in opposite. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. Clock skew, in simple terms, is the difference. Clock Skew And Clock Jitter In Vlsi.

From www.zhihu.com

如何理解 clock drift 和 clock skew 这两个概念呢? 知乎 Clock Skew And Clock Jitter In Vlsi Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. These clock sources should maintain regular clock cycles with clean edges. Clock skew, in. Clock Skew And Clock Jitter In Vlsi.

From www.mdpi.com

JLPEA Free FullText Review and Comparison of Clock Jitter Noise Clock Skew And Clock Jitter In Vlsi Any signal takes some time to. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. If possible, route data and clock in opposite. Clock skew and jitter are the essential topics to understand in vlsi timing closure. In a clock path skew and jitter are the unwanted phenomena that should b.. Clock Skew And Clock Jitter In Vlsi.

From www.youtube.com

Lecture6 VLSI System Testing Clock Skew Types YouTube Clock Skew And Clock Jitter In Vlsi Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Any signal takes some time to. Clock skew and jitter are the essential topics to understand in vlsi timing closure. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. Skew. Clock Skew And Clock Jitter In Vlsi.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Clock Skewtolerant circuits Clock Skew And Clock Jitter In Vlsi Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. Clock skew and jitter are the essential topics to understand in vlsi timing. Clock Skew And Clock Jitter In Vlsi.

From www.physicaldesign4u.com

OCV (On Chip Variation) and CRPR (Clock Reconvergence Pessimism Removal Clock Skew And Clock Jitter In Vlsi In a clock path skew and jitter are the unwanted phenomena that should b. If possible, route data and clock in opposite. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. These clock sources should maintain regular clock cycles with clean edges. In a circuit, there is a. Clock Skew And Clock Jitter In Vlsi.

From 8.136.218.141

Static Timing Analysis Physical Design VLSI BackEnd Adventure Clock Skew And Clock Jitter In Vlsi In a clock path skew and jitter are the unwanted phenomena that should b. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. These clock sources should maintain regular clock. Clock Skew And Clock Jitter In Vlsi.

From www.youtube.com

Clock Skew in VLSI Positive Skew Negative Skew Global Skew Clock Skew And Clock Jitter In Vlsi Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. In a clock path skew and jitter are the unwanted phenomena that should b. Any signal. Clock Skew And Clock Jitter In Vlsi.

From dokumen.tips

(PDF) Lecture 9 Clocking, Clock Skew, Clock Jitter, Clock Distribution Clock Skew And Clock Jitter In Vlsi Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. If possible, route data and clock in opposite. Clock skew, in simple terms, is the difference. Clock Skew And Clock Jitter In Vlsi.

From www.slideserve.com

PPT Chapter 10 PowerPoint Presentation, free download ID6062070 Clock Skew And Clock Jitter In Vlsi These clock sources should maintain regular clock cycles with clean edges. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. If possible, route data and clock in opposite. Any signal takes some time to. In a circuit, there is a clock generating source. Clock Skew And Clock Jitter In Vlsi.

From www.youtube.com

VLSI STA What is clock jitter? YouTube Clock Skew And Clock Jitter In Vlsi In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. Skew is defined as the difference between the arrival. Clock Skew And Clock Jitter In Vlsi.

From siliconvlsi.com

What do you mean by clock Jitter? Siliconvlsi Clock Skew And Clock Jitter In Vlsi These clock sources should maintain regular clock cycles with clean edges. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. In a clock path skew and jitter are the unwanted phenomena that should b. Clock skew and jitter are the essential topics to understand in vlsi timing closure.. Clock Skew And Clock Jitter In Vlsi.

From www.slideshare.net

Clock Skew 1 Clock Skew And Clock Jitter In Vlsi If possible, route data and clock in opposite. Any signal takes some time to. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew and jitter are the essential topics to understand in vlsi timing closure. In a clock path skew and jitter are the unwanted phenomena. Clock Skew And Clock Jitter In Vlsi.

From mahajankankit.medium.com

STA Explanation of Clock Skew Concepts in VLSI by ANKIT MAHAJAN Medium Clock Skew And Clock Jitter In Vlsi In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. These clock sources should maintain regular clock cycles with clean edges. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc.. Clock Skew And Clock Jitter In Vlsi.

From vlsimaster.com

Clock Jitter VLSI Master Clock Skew And Clock Jitter In Vlsi Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. If possible, route data and clock in opposite. These clock sources should maintain regular clock cycles with clean edges. Clock skew and jitter are the essential topics to understand in vlsi timing closure. In. Clock Skew And Clock Jitter In Vlsi.

From www.youtube.com

Clock Skew and Jitter YouTube Clock Skew And Clock Jitter In Vlsi These clock sources should maintain regular clock cycles with clean edges. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. Skew is defined as the difference between the arrival time of the clock signal at the clock pin. Clock Skew And Clock Jitter In Vlsi.

From www.semanticscholar.org

Figure 61 from A lowskew, low jitter receiver circuit for onchip Clock Skew And Clock Jitter In Vlsi Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. In a clock path skew and jitter are the unwanted phenomena that should b. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal. Clock Skew And Clock Jitter In Vlsi.

From slideplayer.com

Mary Jane Irwin ( ) CSE477 VLSI Digital Circuits Fall 2002 Lecture 19 Clock Skew And Clock Jitter In Vlsi In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. These clock sources should maintain regular clock cycles with clean edges. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and. Clock Skew And Clock Jitter In Vlsi.

From www.youtube.com

Chapter07 Clock Latency Clock Skew Clock Jitter Clock Clock Skew And Clock Jitter In Vlsi Clock skew and jitter are the essential topics to understand in vlsi timing closure. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch. Clock Skew And Clock Jitter In Vlsi.

From siliconvlsi.com

What is useful skew, local skew and global skew? Siliconvlsi Clock Skew And Clock Jitter In Vlsi These clock sources should maintain regular clock cycles with clean edges. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. In a clock path skew and jitter are the unwanted phenomena that should b. In a circuit, there is a clock generating source either its pll or a. Clock Skew And Clock Jitter In Vlsi.

From siliconvlsi.com

Difference Between Clock Skew and Uncertainty Siliconvlsi Clock Skew And Clock Jitter In Vlsi Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop. If possible, route data and clock in opposite. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew and jitter are. Clock Skew And Clock Jitter In Vlsi.

From vlsitalks.com

CTS (CLOCK TREE SYNTHESIS) VLSI TALKS Clock Skew And Clock Jitter In Vlsi Clock skew and jitter are the essential topics to understand in vlsi timing closure. Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop. Clock Skew And Clock Jitter In Vlsi.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Skew And Clock Jitter In Vlsi In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. These clock sources should maintain regular clock cycles with clean edges. Any signal takes some time to. If possible, route data and clock in opposite. Skew is defined as. Clock Skew And Clock Jitter In Vlsi.

From www.slideshare.net

Clock Distribution Clock Skew And Clock Jitter In Vlsi In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. Any signal takes some time to. In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. Clock skew and. Clock Skew And Clock Jitter In Vlsi.

From www.scribd.com

STA Explanation of Clock Skew Concepts in VLSI by ANKIT MAHAJAN Clock Skew And Clock Jitter In Vlsi In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. These clock sources should maintain regular clock cycles with clean edges. Any signal takes some time to. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and. Clock Skew And Clock Jitter In Vlsi.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Skew And Clock Jitter In Vlsi If possible, route data and clock in opposite. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop.. Clock Skew And Clock Jitter In Vlsi.

From vlsiuniverse.blogspot.in

Clock jitter Clock Skew And Clock Jitter In Vlsi In a clock path skew and jitter are the unwanted phenomena that should b. If possible, route data and clock in opposite. Clock skew and jitter are the essential topics to understand in vlsi timing closure. In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. Any signal takes some. Clock Skew And Clock Jitter In Vlsi.

From slideplayer.com

Mary Jane Irwin ( ) CSE477 VLSI Digital Circuits Fall 2002 Lecture 19 Clock Skew And Clock Jitter In Vlsi In a clock path skew and jitter are the unwanted phenomena that should b. In the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. If possible, route data and clock in opposite. In a circuit, there is a clock. Clock Skew And Clock Jitter In Vlsi.

From www.vlsijunction.com

VLSI Physical Design Clock Skew Clock Skew And Clock Jitter In Vlsi Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. Clock skew and jitter are the essential topics to understand in vlsi timing closure. These clock sources should maintain regular clock cycles with clean edges. Any signal takes some time to. In a clock path skew and jitter are the unwanted phenomena. Clock Skew And Clock Jitter In Vlsi.

From www.youtube.com

VLSI Static Timing Analysis Training Lecture on Clock Skew, CRPR Clock Skew And Clock Jitter In Vlsi In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. In a clock path skew and jitter are the unwanted phenomena that should b. Skew is defined as the difference between the arrival time of the clock signal at the clock pin of the capture flop and the launch flop.. Clock Skew And Clock Jitter In Vlsi.

From siliconvlsi.com

What are the sources of Skew and Jitter in Clock signals? Siliconvlsi Clock Skew And Clock Jitter In Vlsi In a circuit, there is a clock generating source either its pll or a clock oscillator, or any other source. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew and jitter are the essential topics to understand in vlsi timing closure. Any signal takes some time. Clock Skew And Clock Jitter In Vlsi.