Clock Cycle Time In A Pipelined Processor . The following data is given, about the. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). Not quite a factor of n due to pipeline overheads. Cycle time is the longest delay. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. Time required to complete a. Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle:

from www.chegg.com

The following data is given, about the. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Cycle time is the longest delay. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: Time required to complete a. Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Not quite a factor of n due to pipeline overheads.

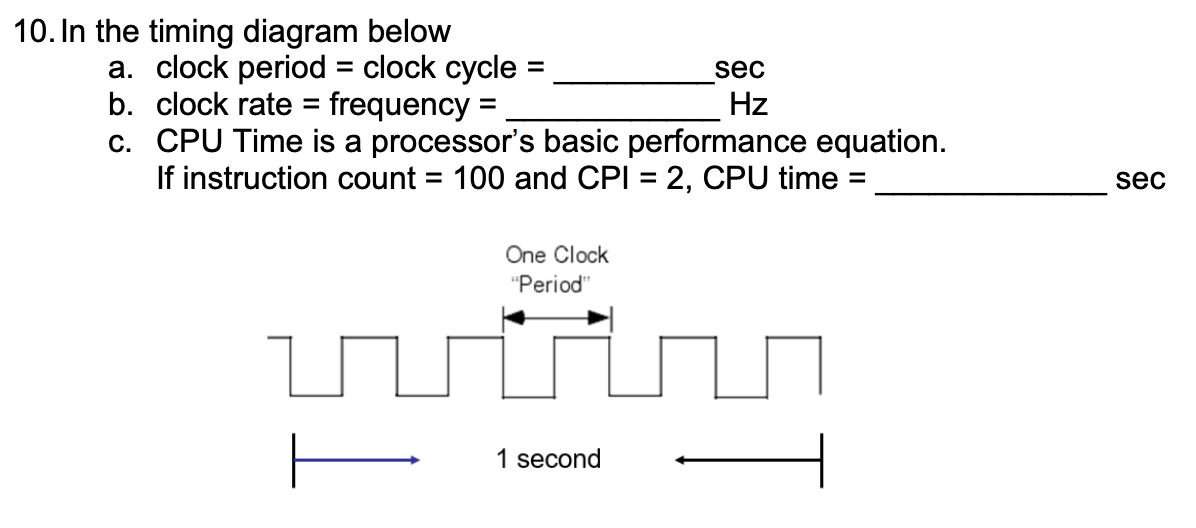

Solved 10. In the timing diagram below a. clock period =

Clock Cycle Time In A Pipelined Processor The following data is given, about the. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. The following data is given, about the. Time required to complete a. Cycle time is the longest delay. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. Not quite a factor of n due to pipeline overheads. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than.

From www.coursehigh.com

(Solved) 2 Exercise Examine Pipelining Affects Clock Cycle Time Clock Cycle Time In A Pipelined Processor In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). Time required to complete a. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of. Clock Cycle Time In A Pipelined Processor.

From people.cs.pitt.edu

Implementing the PIpelined CPU Clock Cycle Time In A Pipelined Processor Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: Since instructions take different time to finish, memory and functional unit are not efficiently utilized. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb. Clock Cycle Time In A Pipelined Processor.

From www.slideserve.com

PPT Pipelined Processor Design PowerPoint Presentation, free download Clock Cycle Time In A Pipelined Processor My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. Not quite a factor of n due to pipeline overheads. Time required to complete a. In a pipelined processor, all the pipeline stages take a single clock. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved a) (4pts) What is the clock cycle time in a Clock Cycle Time In A Pipelined Processor In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates.. Clock Cycle Time In A Pipelined Processor.

From www.cgdirector.com

What is a CPU's IPC? Instructions per Cycle explained Clock Cycle Time In A Pipelined Processor In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Cycle time is the longest delay. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat. Clock Cycle Time In A Pipelined Processor.

From www.pinterest.com

What is the clock cycle time in a pipelined and nonpipelined processor Clock Cycle Time In A Pipelined Processor Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Time required to complete a. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. In. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved In this exercise, we examine how pipelining affects Clock Cycle Time In A Pipelined Processor In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Cycle time everything in a cpu. Clock Cycle Time In A Pipelined Processor.

From slideplayer.com

Pipelined datapath and control ppt download Clock Cycle Time In A Pipelined Processor Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Not quite a factor of n due to pipeline overheads. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: In this organization, an instruction only goes through stages it actually needs (e.g., st only. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

What is the clock cycle time in a pipelined and Clock Cycle Time In A Pipelined Processor In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). Not quite a factor of n due to pipeline. Clock Cycle Time In A Pipelined Processor.

From www.slideserve.com

PPT Pipelined Datapath and Control PowerPoint Presentation, free Clock Cycle Time In A Pipelined Processor Not quite a factor of n due to pipeline overheads. Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. Cycle time is the longest delay. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Time required to complete a. Since instructions take different time to. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved 10. In the timing diagram below a. clock period = Clock Cycle Time In A Pipelined Processor In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. The following data is given, about the. Cycle time. Clock Cycle Time In A Pipelined Processor.

From www.numerade.com

SOLVED 4.8 In this exercise, we examine how pipelining affects the Clock Cycle Time In A Pipelined Processor Time required to complete a. Cycle time is the longest delay. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. The following data is given, about the. Cycle time. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved a) [3 Points] What is the clock cycle time for a Clock Cycle Time In A Pipelined Processor In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. Not quite a factor of n due to pipeline overheads. My assignment deals with calculations of. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved (20 points) (a)What is the clock cycle time in a Clock Cycle Time In A Pipelined Processor My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Time required to complete a. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Not quite a factor of n due to pipeline overheads. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the. Clock Cycle Time In A Pipelined Processor.

From www.numerade.com

SOLVED Q2 (30 points) In this question, we will examine how pipelining Clock Cycle Time In A Pipelined Processor In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. Not quite a factor of n due to pipeline overheads. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb. Clock Cycle Time In A Pipelined Processor.

From www.numerade.com

SOLVED Assume that individual stages of the datapath have the Clock Cycle Time In A Pipelined Processor Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. In a pipelined processor, all the. Clock Cycle Time In A Pipelined Processor.

From www.numerade.com

SOLVED In this exercise, we examine how pipelining affects the clock Clock Cycle Time In A Pipelined Processor Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Time required to complete a. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). The following data is given, about the. Multi cycle processor advantages • better mips. Clock Cycle Time In A Pipelined Processor.

From slideplayer.com

CENTRAL PROCESSING UNIT ppt download Clock Cycle Time In A Pipelined Processor Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. Cycle time is the longest delay. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to. Clock Cycle Time In A Pipelined Processor.

From www.numerade.com

SOLVED Assume you examine how pipelining affects the clock cycle time Clock Cycle Time In A Pipelined Processor Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: Cycle time is the longest delay. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Time required to complete a.. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved Given an unpipelined processor with a 10ns cycle time Clock Cycle Time In A Pipelined Processor Since instructions take different time to finish, memory and functional unit are not efficiently utilized. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved Consider a datapth with individual stages having the Clock Cycle Time In A Pipelined Processor Cycle time is the longest delay. Time required to complete a. Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. The following data is given, about the. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: In a pipelined. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved Question 1 The basic singlecycle MIPS Clock Cycle Time In A Pipelined Processor The following data is given, about the. Time required to complete a. In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. In this organization, an instruction only goes through stages. Clock Cycle Time In A Pipelined Processor.

From www.numerade.com

SOLVED Suppose we have two implementations of the same instruction set Clock Cycle Time In A Pipelined Processor Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Cycle time everything in a cpu moves in lockstep, synchronized by the. Clock Cycle Time In A Pipelined Processor.

From slideplayer.com

Lecture 22 Pipelined Processor ppt download Clock Cycle Time In A Pipelined Processor My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Not quite a factor of n due to pipeline overheads. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: In this organization, an instruction only goes through stages it actually needs (e.g., st only takes. Clock Cycle Time In A Pipelined Processor.

From slideplayer.com

Lecture 22 Pipelined Processor ppt download Clock Cycle Time In A Pipelined Processor Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: Time required to complete a. Cycle time is the longest delay. Not quite a factor of n due to pipeline overheads. The following data is given, about the. In a pipelined processor, all the pipeline stages take a single clock. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved In this exercise, we examine how pipelining affects Clock Cycle Time In A Pipelined Processor Not quite a factor of n due to pipeline overheads. In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. The following data is given, about the. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles. Clock Cycle Time In A Pipelined Processor.

From www.numerade.com

SOLVEDIn this exercise, we examine how pipelining affects the clock Clock Cycle Time In A Pipelined Processor In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. The following data is given, about the. Cycle time is the longest delay. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Not quite a factor of n due to. Clock Cycle Time In A Pipelined Processor.

From www.slideserve.com

PPT Pipelined Processor Design PowerPoint Presentation, free download Clock Cycle Time In A Pipelined Processor The following data is given, about the. Time required to complete a. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. My assignment deals. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved What is the clock cycle time in nanoseconds ( ns) of Clock Cycle Time In A Pipelined Processor Cycle time is the longest delay. Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

What is the clock cycle time in a pipelined and Clock Cycle Time In A Pipelined Processor Time required to complete a. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). Since instructions take different time to finish, memory and functional unit are not efficiently utilized. My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates.. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

Solved (a) What is the clock cycle time in a pipelined and Clock Cycle Time In A Pipelined Processor My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. The following data is given, about the. Time required to complete a. In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). Since instructions take different time to finish, memory. Clock Cycle Time In A Pipelined Processor.

From www.semanticscholar.org

Figure 1 from SIMD pipelined processor implemented on a FPGA Semantic Clock Cycle Time In A Pipelined Processor In this organization, an instruction only goes through stages it actually needs (e.g., st only takes 4 cycles because it does not need the wb stage). My assignment deals with calculations of pipelined cpu and single cycle cpu clock rates. Time required to complete a. The following data is given, about the. In a pipelined processor, all the pipeline stages. Clock Cycle Time In A Pipelined Processor.

From www.chegg.com

2. We examine how pipelining affects the clock cycle Clock Cycle Time In A Pipelined Processor In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough to accommodate the slowest stage. Not quite a factor of n due to pipeline overheads. Multi cycle processor advantages • better mips and smaller clock period (higher clock frequency) • hence, better performance than. My assignment deals with calculations of. Clock Cycle Time In A Pipelined Processor.

From stackoverflow.com

mips Clock cycle in pipelining and singleclock cycle implementation Clock Cycle Time In A Pipelined Processor Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Time required to complete a. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: In a pipelined processor, all the pipeline stages take a single clock cycle, so clock cycle must be long enough. Clock Cycle Time In A Pipelined Processor.

From www.numerade.com

SOLVED Assume that individual stages of the datapath have the Clock Cycle Time In A Pipelined Processor Time required to complete a. Cycle time everything in a cpu moves in lockstep, synchronized by the clock (heartbeat of the cpu.) a machine cycle: Since instructions take different time to finish, memory and functional unit are not efficiently utilized. Not quite a factor of n due to pipeline overheads. The following data is given, about the. Cycle time is. Clock Cycle Time In A Pipelined Processor.