Transmission Gate Verilog . Useful for multiplexers (select between multiple inputs) and xors. (output, input, enable, ~enable) example (transmission. A simulator can do this for a tran gate by splitting. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Transmission gate has one output, one input. In vhdl the transmission gate is represented with the keyword cmos. Cmos, rcmos (resistive version) terminal list: Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. You have described a fundamental problem in implementing transmission gates. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels.

from www.slideserve.com

A simulator can do this for a tran gate by splitting. (output, input, enable, ~enable) example (transmission. Transmission gate has one output, one input. Cmos, rcmos (resistive version) terminal list: You have described a fundamental problem in implementing transmission gates. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. In vhdl the transmission gate is represented with the keyword cmos. Useful for multiplexers (select between multiple inputs) and xors. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels.

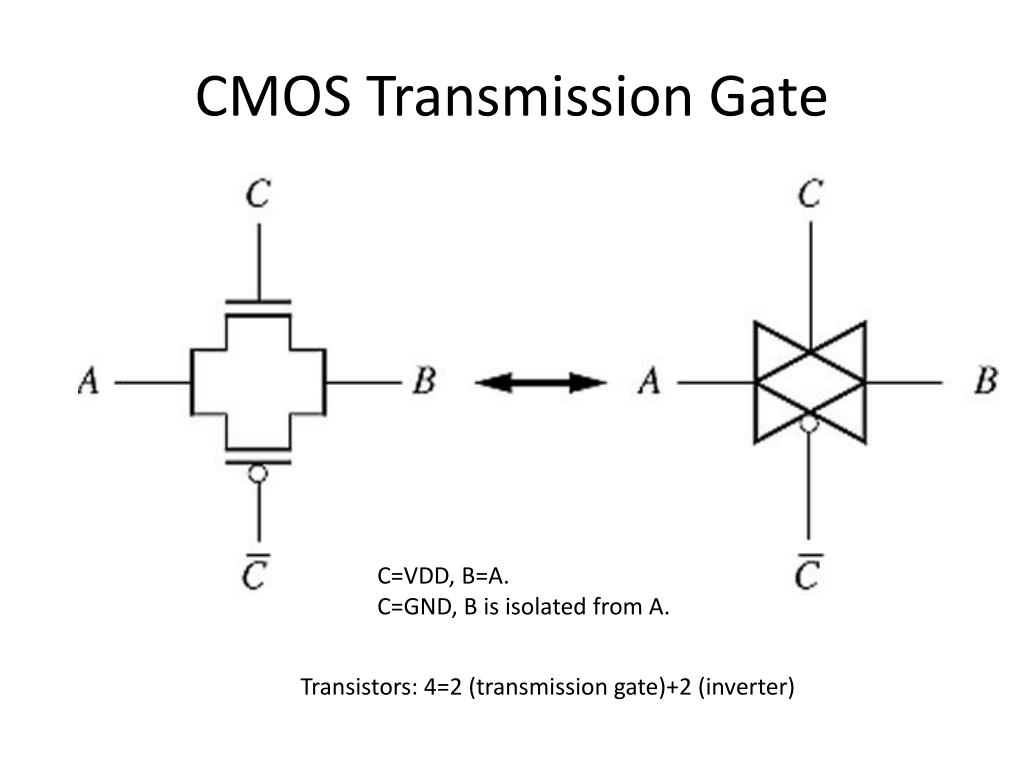

PPT CMOS Transmission Gate PowerPoint Presentation, free download

Transmission Gate Verilog Transmission gate has one output, one input. Useful for multiplexers (select between multiple inputs) and xors. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. In vhdl the transmission gate is represented with the keyword cmos. You have described a fundamental problem in implementing transmission gates. A simulator can do this for a tran gate by splitting. Cmos, rcmos (resistive version) terminal list: Transmission gate has one output, one input. (output, input, enable, ~enable) example (transmission. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels.

From www.semanticscholar.org

Figure 7 from Transmission gatebased approximate adders for inexact Transmission Gate Verilog In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Useful for multiplexers (select between multiple inputs) and xors. In vhdl the transmission gate is represented with the keyword cmos. (output, input, enable, ~enable) example (transmission. You have described a fundamental problem in implementing transmission gates. A simulator can do this. Transmission Gate Verilog.

From www.youtube.com

LTspice tutorial 3 Simulation of Transmission gate circuit using BSIM4 Transmission Gate Verilog In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. (output, input, enable, ~enable) example (transmission. Transmission gate has one output, one input. In vhdl the transmission gate is represented with the keyword cmos. You have described a fundamental problem in implementing transmission gates. The transmission gate is a bilateral switch. Transmission Gate Verilog.

From www.semanticscholar.org

Figure 2 from A High Speed Transmission Gate Logic Base 1/N Frequency Transmission Gate Verilog Transmission gate has one output, one input. A simulator can do this for a tran gate by splitting. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. Cmos, rcmos (resistive version) terminal list: Useful for multiplexers (select between multiple inputs) and xors. In this homework, you will learn to create. Transmission Gate Verilog.

From www.youtube.com

CMOS Transmission Gate Logic (PART 1) Day On My Plate VLSI Design Transmission Gate Verilog A simulator can do this for a tran gate by splitting. Useful for multiplexers (select between multiple inputs) and xors. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Cmos, rcmos (resistive version) terminal list: (output, input, enable, ~enable) example (transmission. In vhdl the transmission gate is represented with the. Transmission Gate Verilog.

From studylib.net

CMOS Transmission Gates Transmission Gate Verilog A simulator can do this for a tran gate by splitting. Cmos, rcmos (resistive version) terminal list: Useful for multiplexers (select between multiple inputs) and xors. Transmission gate has one output, one input. (output, input, enable, ~enable) example (transmission. In vhdl the transmission gate is represented with the keyword cmos. The transmission gate is a bilateral switch consisting of nmos. Transmission Gate Verilog.

From www.slideserve.com

PPT CMOS Transmission Gate PowerPoint Presentation, free download Transmission Gate Verilog In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. You have described a fundamental problem in implementing transmission gates. Cmos, rcmos (resistive version) terminal list: Transmission gate has one output, one. Transmission Gate Verilog.

From www.linkedin.com

Transmission Gate Advantages Over CMOS Transmission Gate Verilog You have described a fundamental problem in implementing transmission gates. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. In vhdl the transmission gate is represented with the keyword cmos. A simulator can do this for a tran gate by splitting. (output, input, enable, ~enable) example (transmission. Transmission gate has. Transmission Gate Verilog.

From www.researchgate.net

TFET transmission gate based (a) 3‐stage cascaded delay chain,(b Transmission Gate Verilog Useful for multiplexers (select between multiple inputs) and xors. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Transmission gate has one output, one input.. Transmission Gate Verilog.

From www.slideserve.com

PPT Verilog Hardware Description Language PowerPoint Presentation Transmission Gate Verilog The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. You have described a fundamental problem in implementing transmission gates. Transmission gate has one output, one input. Cmos, rcmos (resistive version) terminal list: In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary. Transmission Gate Verilog.

From www.semanticscholar.org

Figure 1 from A Simple Transistors Width Adjustment Method on CMOS Transmission Gate Verilog In vhdl the transmission gate is represented with the keyword cmos. A simulator can do this for a tran gate by splitting. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. In this homework, you will learn to create structural (gate and transistor level). Transmission Gate Verilog.

From www.youtube.com

Lecture3 Gate Level Modelling Verilog Programming YouTube Transmission Gate Verilog Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. You have described a fundamental problem in implementing transmission gates. (output, input, enable, ~enable) example (transmission. In vhdl the transmission gate is represented with the keyword cmos. The transmission gate is a bilateral switch consisting. Transmission Gate Verilog.

From dokumen.tips

(PDF) Optimization for Transmission Gate Master Slave Scan Flip Flop Transmission Gate Verilog A simulator can do this for a tran gate by splitting. Transmission gate has one output, one input. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. In vhdl the transmission gate is represented with the keyword cmos. Useful for multiplexers (select between multiple inputs) and xors. Cmos, rcmos (resistive. Transmission Gate Verilog.

From www.youtube.com

TRANSMISSION GATE Verilog code verilog vlsi transmission YouTube Transmission Gate Verilog In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. You have described a fundamental problem in implementing transmission gates. A simulator can do this for a tran gate by splitting. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates. Transmission Gate Verilog.

From www.researchgate.net

A Basic Transmission Gate Download Scientific Diagram Transmission Gate Verilog The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. Transmission gate has one output, one input. A simulator can do this for a tran gate by splitting. In vhdl the transmission gate is represented with the keyword cmos. Cmos, rcmos (resistive version) terminal list: Useful for multiplexers (select between multiple. Transmission Gate Verilog.

From www.slideserve.com

PPT CMOS Transmission Gate PowerPoint Presentation, free download Transmission Gate Verilog In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Transmission gate has one output, one input. Cmos, rcmos (resistive version) terminal list: A simulator can do this for a tran gate by splitting. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual. Transmission Gate Verilog.

From www.chegg.com

Solved 1. Consider the following CMOS transmission gate. We Transmission Gate Verilog A simulator can do this for a tran gate by splitting. Useful for multiplexers (select between multiple inputs) and xors. (output, input, enable, ~enable) example (transmission. Cmos, rcmos (resistive version) terminal list: Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. In vhdl the. Transmission Gate Verilog.

From www.youtube.com

Transmission Gate logic Implement Logic Gates using Transmission Transmission Gate Verilog Useful for multiplexers (select between multiple inputs) and xors. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. (output, input, enable, ~enable) example (transmission. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. In. Transmission Gate Verilog.

From www.researchgate.net

Schematic of transmission gatebased D flipflop. Download Scientific Transmission Gate Verilog In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Transmission gate has one output, one input. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. Cmos, rcmos (resistive version) terminal list: In vhdl the. Transmission Gate Verilog.

From ar.inspiredpencil.com

Cmos Transistor Symbol Transmission Gate Verilog You have described a fundamental problem in implementing transmission gates. Cmos, rcmos (resistive version) terminal list: Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. Transmission gate has one output, one input. In vhdl the transmission gate is represented with the keyword cmos. In. Transmission Gate Verilog.

From studylib.net

cmos transmission gate circuits Transmission Gate Verilog In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Transmission gate has one output, one input. In vhdl the transmission gate is represented with the keyword cmos. You have described a fundamental problem in implementing transmission gates. Cmos, rcmos (resistive version) terminal list: A simulator can do this for a. Transmission Gate Verilog.

From www.google.com

Patent US6404237 Boosted multiplexer transmission gate Google Patents Transmission Gate Verilog Useful for multiplexers (select between multiple inputs) and xors. In vhdl the transmission gate is represented with the keyword cmos. You have described a fundamental problem in implementing transmission gates. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. Transmission gate has one output,. Transmission Gate Verilog.

From www.chegg.com

Solved a) Discuss the advantages transmission gates have Transmission Gate Verilog (output, input, enable, ~enable) example (transmission. You have described a fundamental problem in implementing transmission gates. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. Transmission gate has one output, one. Transmission Gate Verilog.

From iamradhakulkarni.blogspot.com

TRANSMISSION GATE CMOS Transmission Gate Verilog You have described a fundamental problem in implementing transmission gates. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. (output, input, enable, ~enable) example (transmission. Transmission gate has one output, one input. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic. Transmission Gate Verilog.

From manualfixmaureen.z13.web.core.windows.net

Design 2 Bit Comparator Using Gates Transmission Gate Verilog Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. In vhdl the transmission gate is represented with the keyword cmos. A simulator can do this for a tran gate by splitting. You have described a fundamental problem in implementing transmission gates. The transmission gate. Transmission Gate Verilog.

From www.youtube.com

D Latch Implementation using Transmission Gate CMOS Transmission Gate Transmission Gate Verilog Transmission gate has one output, one input. You have described a fundamental problem in implementing transmission gates. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. Verilog gate level modeling techniques. Transmission Gate Verilog.

From www.allaboutcircuits.com

The CMOS Transmission Gate Transmission Gate Verilog Transmission gate has one output, one input. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. (output, input, enable, ~enable) example (transmission. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. In vhdl the transmission gate is represented with the. Transmission Gate Verilog.

From www.youtube.com

Pass Transistor Transmission Gate Switch logic PDC Lec116 Transmission Gate Verilog A simulator can do this for a tran gate by splitting. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. (output, input, enable, ~enable) example (transmission. In vhdl the transmission gate is represented with the keyword cmos. Cmos, rcmos (resistive version) terminal list: Transmission gate has one output, one input.. Transmission Gate Verilog.

From slideplayer.com

Copyright © 2004 The McGrawHill Companies, Inc. All rights reserved Transmission Gate Verilog Cmos, rcmos (resistive version) terminal list: You have described a fundamental problem in implementing transmission gates. Useful for multiplexers (select between multiple inputs) and xors. A simulator can do this for a tran gate by splitting. In vhdl the transmission gate is represented with the keyword cmos. Transmission gate has one output, one input. The transmission gate is a bilateral. Transmission Gate Verilog.

From electronics.stackexchange.com

circuit design Plotting MOS resistances in transmission gates in Transmission Gate Verilog Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. A simulator can do this for a tran gate by splitting. In vhdl the transmission gate. Transmission Gate Verilog.

From www.circuitdiagram.co

Cmos Transmission Gate Circuit Circuit Diagram Transmission Gate Verilog Useful for multiplexers (select between multiple inputs) and xors. (output, input, enable, ~enable) example (transmission. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. In vhdl the transmission gate is represented with the keyword cmos. Cmos, rcmos (resistive version) terminal list: You have described a fundamental problem in implementing transmission. Transmission Gate Verilog.

From www.kindpng.com

Transmission Gate Symbol, HD Png Download kindpng Transmission Gate Verilog A simulator can do this for a tran gate by splitting. Cmos, rcmos (resistive version) terminal list: Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and xor. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic. Transmission Gate Verilog.

From slideplayer.com

مدار منطقی Logic Circuits ppt download Transmission Gate Verilog A simulator can do this for a tran gate by splitting. Transmission gate has one output, one input. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. (output, input, enable, ~enable) example (transmission. Cmos, rcmos (resistive version) terminal list: The transmission gate is a bilateral switch consisting of nmos and. Transmission Gate Verilog.

From www.semanticscholar.org

Figure 2 from An analytical delay model for CMOS InverterTransmission Transmission Gate Verilog Useful for multiplexers (select between multiple inputs) and xors. Cmos, rcmos (resistive version) terminal list: (output, input, enable, ~enable) example (transmission. Transmission gate has one output, one input. A simulator can do this for a tran gate by splitting. In vhdl the transmission gate is represented with the keyword cmos. The transmission gate is a bilateral switch consisting of nmos. Transmission Gate Verilog.

From www.circuitdiagram.co

Cmos Transmission Gate Circuit Circuit Diagram Transmission Gate Verilog Useful for multiplexers (select between multiple inputs) and xors. In this homework, you will learn to create structural (gate and transistor level) and functional descriptions of elementary and. The transmission gate is a bilateral switch consisting of nmos and pmos transistors controlled by externally applied logic levels. A simulator can do this for a tran gate by splitting. Cmos, rcmos. Transmission Gate Verilog.

From www.youtube.com

Transmission Gate Combinational Circuit Design Know How YouTube Transmission Gate Verilog Useful for multiplexers (select between multiple inputs) and xors. In vhdl the transmission gate is represented with the keyword cmos. Cmos, rcmos (resistive version) terminal list: You have described a fundamental problem in implementing transmission gates. Verilog gate level modeling techniques are useful to introduce and model delays that are inherent to actual physical logic gates like and, or, and. Transmission Gate Verilog.