Gates In Verilog . In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. These primitives are instantiated like modules except that they are predefined in verilog and do. These are just modeling styles and do not affect the final hardware design that we are going to make. In this post, we will code the or gate using three modeling styles available in verilog: The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. Gate level, dataflow, and behavioral modeling. In every model, we get the same results, but abstraction levels and coding approaches are different. Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. Verilog has built in primitives like gates, transmission gates, and switches. These are rarely used in design (rtl coding), but are used. Verilog supports coding circuits using basic logic gates as predefined primitives. A digital circuit is implemented using logic gates and interconnections between these gates.

from www.studocu.com

Verilog supports coding circuits using basic logic gates as predefined primitives. A digital circuit is implemented using logic gates and interconnections between these gates. In this post, we will code the or gate using three modeling styles available in verilog: Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. These are just modeling styles and do not affect the final hardware design that we are going to make. Gate level, dataflow, and behavioral modeling. These are rarely used in design (rtl coding), but are used. Verilog has built in primitives like gates, transmission gates, and switches. In every model, we get the same results, but abstraction levels and coding approaches are different. The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks.

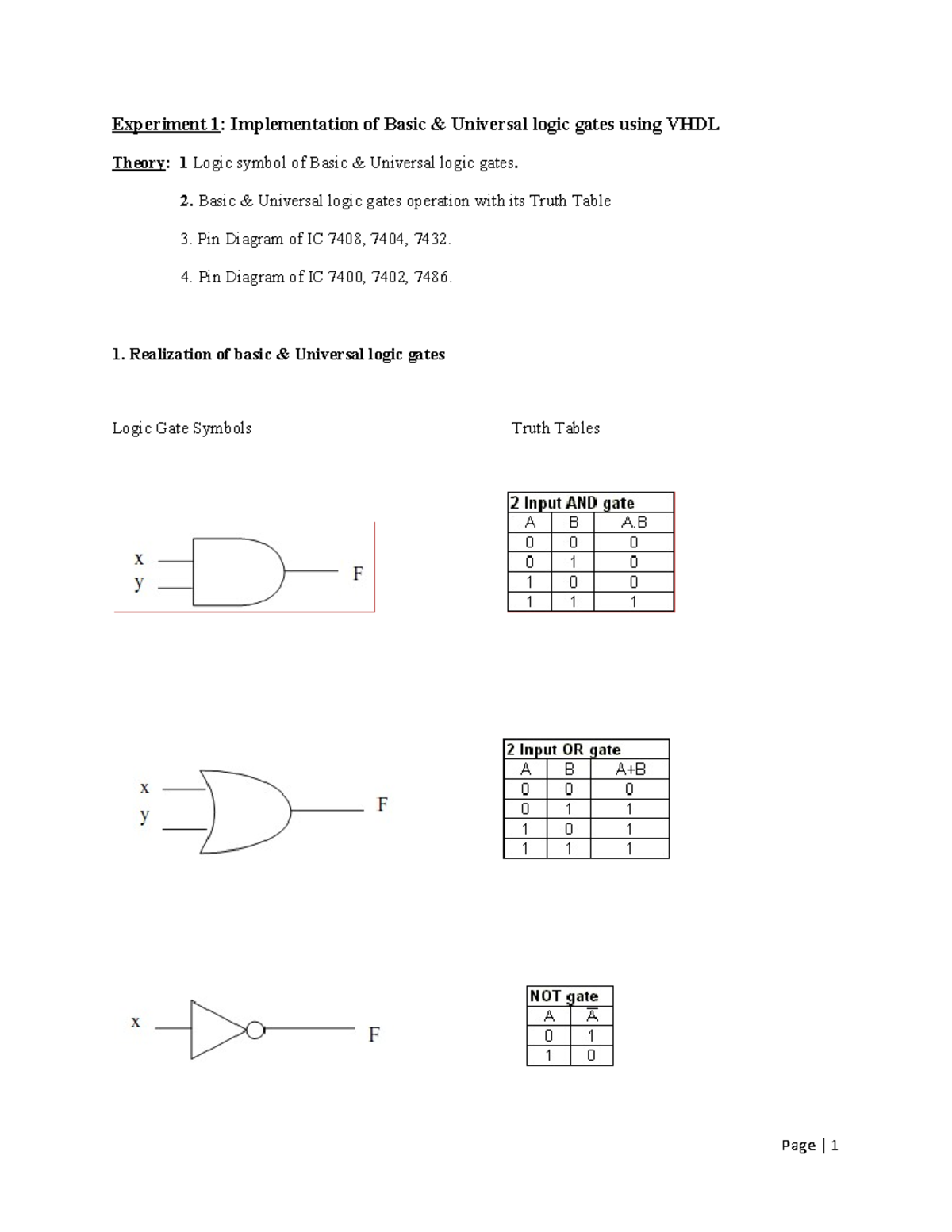

Implementation of basic and logic gates using VHDL and verilog

Gates In Verilog The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. Verilog has built in primitives like gates, transmission gates, and switches. In every model, we get the same results, but abstraction levels and coding approaches are different. A digital circuit is implemented using logic gates and interconnections between these gates. The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. These primitives are instantiated like modules except that they are predefined in verilog and do. Verilog supports coding circuits using basic logic gates as predefined primitives. Gate level, dataflow, and behavioral modeling. These are just modeling styles and do not affect the final hardware design that we are going to make. These are rarely used in design (rtl coding), but are used. In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. In this post, we will code the or gate using three modeling styles available in verilog:

From www.studocu.com

Implementation of basic and logic gates using VHDL and verilog Gates In Verilog Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. A digital circuit is. Gates In Verilog.

From www.youtube.com

GATE LEVEL MODELLING 2 Design and verify half subtractor using Gates In Verilog Verilog supports coding circuits using basic logic gates as predefined primitives. These are rarely used in design (rtl coding), but are used. In every model, we get the same results, but abstraction levels and coding approaches are different. In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay. Gates In Verilog.

From www.chegg.com

Solved The Code must be written in verilog here is the gate Gates In Verilog In every model, we get the same results, but abstraction levels and coding approaches are different. These are rarely used in design (rtl coding), but are used. These primitives are instantiated like modules except that they are predefined in verilog and do. Gate level, dataflow, and behavioral modeling. In this post, we will code the or gate using three modeling. Gates In Verilog.

From circuitdigest.com

Implementation of Basic Logic Gates using VHDL in ModelSim Gates In Verilog Verilog supports coding circuits using basic logic gates as predefined primitives. These are rarely used in design (rtl coding), but are used. These are just modeling styles and do not affect the final hardware design that we are going to make. Modeling done at this level is usually called gate level modeling as it involves gates and has a one. Gates In Verilog.

From medium.com

Logic Gates By 2X1 MUX Implementation in Verilog by RAO MUHAMMAD UMER Gates In Verilog In every model, we get the same results, but abstraction levels and coding approaches are different. A digital circuit is implemented using logic gates and interconnections between these gates. In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. These primitives are instantiated. Gates In Verilog.

From www.numerade.com

SOLVED Please use 'and' or 'not' gate to design XNOR gate by Verilog Gates In Verilog These are rarely used in design (rtl coding), but are used. In this post, we will code the or gate using three modeling styles available in verilog: Verilog supports coding circuits using basic logic gates as predefined primitives. Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation. Gates In Verilog.

From www.oreilly.com

Appendix A Logic Gates and Boolean Algebra Used in the Book FSM Gates In Verilog A digital circuit is implemented using logic gates and interconnections between these gates. These are rarely used in design (rtl coding), but are used. These primitives are instantiated like modules except that they are predefined in verilog and do. Verilog supports coding circuits using basic logic gates as predefined primitives. Modeling done at this level is usually called gate level. Gates In Verilog.

From eliteengineerofficial.blogspot.com

LOGIC GATES USING VERILOG Gates In Verilog The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. In this post, we will. Gates In Verilog.

From www.youtube.com

27. Verilog HDL Gate level modeling And/Or gates, Buf/Not gates Gates In Verilog In every model, we get the same results, but abstraction levels and coding approaches are different. In this post, we will code the or gate using three modeling styles available in verilog: Verilog has built in primitives like gates, transmission gates, and switches. Gate level, dataflow, and behavioral modeling. These are rarely used in design (rtl coding), but are used.. Gates In Verilog.

From www.slideserve.com

PPT Digital System Design PowerPoint Presentation, free download ID Gates In Verilog Verilog has built in primitives like gates, transmission gates, and switches. Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. In every model, we get the same results, but abstraction levels and coding approaches are different. The primitives (the most basic. Gates In Verilog.

From www.numerade.com

SOLVED 2. Implement a 2bit multiplier circuit using halfadders and Gates In Verilog A digital circuit is implemented using logic gates and interconnections between these gates. These primitives are instantiated like modules except that they are predefined in verilog and do. In this post, we will code the or gate using three modeling styles available in verilog: Verilog supports coding circuits using basic logic gates as predefined primitives. These are just modeling styles. Gates In Verilog.

From www.youtube.com

System Verilog tutorial Combinational logic design coding AND OR Gates In Verilog Gate level, dataflow, and behavioral modeling. The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. A digital circuit is implemented using logic gates and interconnections between these gates. Modeling done at this level is usually called gate level modeling as it. Gates In Verilog.

From www.youtube.com

Writing Gates on Verilog YouTube Gates In Verilog Verilog supports coding circuits using basic logic gates as predefined primitives. These primitives are instantiated like modules except that they are predefined in verilog and do. These are just modeling styles and do not affect the final hardware design that we are going to make. In every model, we get the same results, but abstraction levels and coding approaches are. Gates In Verilog.

From www.vrogue.co

Cmos Logic Gates Using Verilog Hdl vrogue.co Gates In Verilog In this post, we will code the or gate using three modeling styles available in verilog: Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. Verilog has built in primitives like gates, transmission gates, and switches. In every model, we get. Gates In Verilog.

From www.youtube.com

GATE LEVEL MODELLING 3 Design and verify Full adder using Verilog HDL Gates In Verilog Gate level, dataflow, and behavioral modeling. These are rarely used in design (rtl coding), but are used. Verilog supports coding circuits using basic logic gates as predefined primitives. The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. In the real world,. Gates In Verilog.

From mavink.com

Verilog Not Gate Gates In Verilog Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. A digital circuit is implemented using logic gates and interconnections between these gates. In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and. Gates In Verilog.

From www.youtube.com

Verilog Programslogic gates YouTube Gates In Verilog Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. A digital circuit is implemented using logic gates and interconnections between these gates. These are rarely used in design (rtl coding), but are used. In every model, we get the same results,. Gates In Verilog.

From community.element14.com

SystemVerilog Study Notes. GateLevel Combinational Circuit element14 Gates In Verilog In every model, we get the same results, but abstraction levels and coding approaches are different. These are rarely used in design (rtl coding), but are used. Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. The primitives (the most basic. Gates In Verilog.

From mavink.com

Gate Level Modelling In Verilog Gates In Verilog These are rarely used in design (rtl coding), but are used. Verilog supports coding circuits using basic logic gates as predefined primitives. Verilog has built in primitives like gates, transmission gates, and switches. Gate level, dataflow, and behavioral modeling. These primitives are instantiated like modules except that they are predefined in verilog and do. In every model, we get the. Gates In Verilog.

From www.chegg.com

Solved Question 3 (Verilog using structural gates) A Gates In Verilog In every model, we get the same results, but abstraction levels and coding approaches are different. These are rarely used in design (rtl coding), but are used. In this post, we will code the or gate using three modeling styles available in verilog: Verilog has built in primitives like gates, transmission gates, and switches. These are just modeling styles and. Gates In Verilog.

From mavink.com

Nand Gate Verilog Code Gates In Verilog These primitives are instantiated like modules except that they are predefined in verilog and do. In every model, we get the same results, but abstraction levels and coding approaches are different. Gate level, dataflow, and behavioral modeling. Verilog has built in primitives like gates, transmission gates, and switches. In the real world, digital gates have delays involved for inputs propagating. Gates In Verilog.

From www.chipverify.com

Gate Level Modeling Gates In Verilog These primitives are instantiated like modules except that they are predefined in verilog and do. In this post, we will code the or gate using three modeling styles available in verilog: In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. Verilog has. Gates In Verilog.

From e-com143.blogspot.com

Verilog HDL code to realize all logic gates Gates In Verilog In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. A digital circuit is implemented using logic gates and interconnections between these gates. Gate level, dataflow, and behavioral modeling. Verilog supports coding circuits using basic logic gates as predefined primitives. In this post,. Gates In Verilog.

From www.slideserve.com

PPT Verilog For Computer Design PowerPoint Presentation, free Gates In Verilog A digital circuit is implemented using logic gates and interconnections between these gates. Gate level, dataflow, and behavioral modeling. In this post, we will code the or gate using three modeling styles available in verilog: In every model, we get the same results, but abstraction levels and coding approaches are different. Verilog has built in primitives like gates, transmission gates,. Gates In Verilog.

From www.numerade.com

SOLVED JUST AND B. I will upvote for sure. 5. Design and simulate the Gates In Verilog The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. These primitives are instantiated like modules except that they are predefined in verilog and do. In this post, we will code the or gate using three modeling styles available in verilog: Verilog. Gates In Verilog.

From www.youtube.com

Module 3 buf /not gates in Verilog lecture 14 YouTube Gates In Verilog A digital circuit is implemented using logic gates and interconnections between these gates. Verilog has built in primitives like gates, transmission gates, and switches. In this post, we will code the or gate using three modeling styles available in verilog: Modeling done at this level is usually called gate level modeling as it involves gates and has a one to. Gates In Verilog.

From www.slideserve.com

PPT Lab 1 and 2 Digital System Design Using Verilog PowerPoint Gates In Verilog These are just modeling styles and do not affect the final hardware design that we are going to make. In every model, we get the same results, but abstraction levels and coding approaches are different. Gate level, dataflow, and behavioral modeling. A digital circuit is implemented using logic gates and interconnections between these gates. Verilog has built in primitives like. Gates In Verilog.

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation Gates In Verilog A digital circuit is implemented using logic gates and interconnections between these gates. Gate level, dataflow, and behavioral modeling. Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and the. In this post, we will code the or gate using three modeling styles. Gates In Verilog.

From siliconvlsi.com

Verilog Modules Siliconvlsi Gates In Verilog In every model, we get the same results, but abstraction levels and coding approaches are different. These are rarely used in design (rtl coding), but are used. Gate level, dataflow, and behavioral modeling. Modeling done at this level is usually called gate level modeling as it involves gates and has a one to one relation between a hardware schematic and. Gates In Verilog.

From www.chegg.com

Solved Write the Verilog code for the gate diagram. A small Gates In Verilog The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks. These primitives are instantiated like modules except that they are predefined in verilog and do. In every model, we get the same results, but abstraction levels and coding approaches are different. These. Gates In Verilog.

From www.numerade.com

SOLVED The SR latch can be built using NAND gates or NOR gates. This Gates In Verilog A digital circuit is implemented using logic gates and interconnections between these gates. These are just modeling styles and do not affect the final hardware design that we are going to make. The primitives (the most basic commands of a language) defined in verilog have been set keeping the user requirements in mind making it easy to design bigger blocks.. Gates In Verilog.

From present5.com

Digital Design An Embedded Systems Approach Using Verilog Gates In Verilog In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. These are rarely used in design (rtl coding), but are used. In every model, we get the same results, but abstraction levels and coding approaches are different. Gate level, dataflow, and behavioral modeling.. Gates In Verilog.

From mungfali.com

Behavioral Modeling Verilog Gates In Verilog In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. In every model, we get the same results, but abstraction levels and coding approaches are different. A digital circuit is implemented using logic gates and interconnections between these gates. Gate level, dataflow, and. Gates In Verilog.

From www.vrogue.co

Cmos Logic Gates Using Verilog Hdl vrogue.co Gates In Verilog Gate level, dataflow, and behavioral modeling. In the real world, digital gates have delays involved for inputs propagating to the output with gate operation, and the same delay can be modeled in verilog. These are rarely used in design (rtl coding), but are used. In this post, we will code the or gate using three modeling styles available in verilog:. Gates In Verilog.

From byjus.com

Make a chart of circuit diagram of all logic gate Gates In Verilog Gate level, dataflow, and behavioral modeling. Verilog has built in primitives like gates, transmission gates, and switches. These are rarely used in design (rtl coding), but are used. These are just modeling styles and do not affect the final hardware design that we are going to make. In every model, we get the same results, but abstraction levels and coding. Gates In Verilog.