Power Pad In Vlsi . Pads are normally distributed around the edge of the ic. The board uses 1 oz copper (1.4 mils thick) and. So, power pads act as a bridge to pass the power from the outside to the chip. Power pads are placed along with io pads in the pads section of the full chip. Basically a big (100um x 100um) piece of metal. Many stacking layers for physical robustness. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. The pad should be large enough to have input or output circuitry. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. These pads pass the power from outside of the chip to the power rings. By reducing the voltage difference between local power.

from individual.utoronto.ca

Many stacking layers for physical robustness. Basically a big (100um x 100um) piece of metal. So, power pads act as a bridge to pass the power from the outside to the chip. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Pads are normally distributed around the edge of the ic. These pads pass the power from outside of the chip to the power rings. By reducing the voltage difference between local power. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. The board uses 1 oz copper (1.4 mils thick) and. The pad should be large enough to have input or output circuitry.

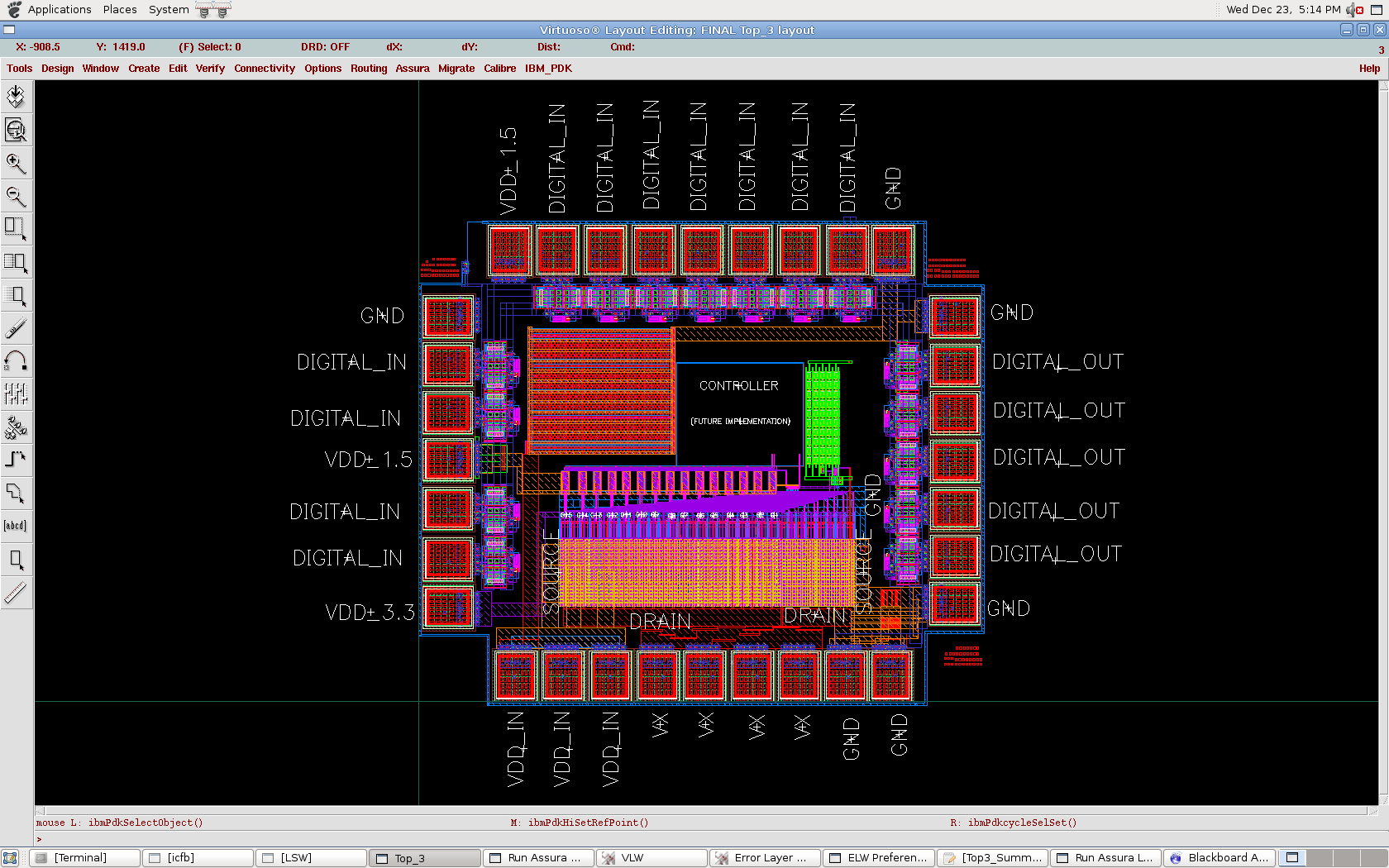

ECE1388 VLSI Design Methodology Final Project

Power Pad In Vlsi Many stacking layers for physical robustness. Many stacking layers for physical robustness. The board uses 1 oz copper (1.4 mils thick) and. By reducing the voltage difference between local power. Power pads are placed along with io pads in the pads section of the full chip. Pads are normally distributed around the edge of the ic. So, power pads act as a bridge to pass the power from the outside to the chip. These pads pass the power from outside of the chip to the power rings. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Basically a big (100um x 100um) piece of metal. The pad should be large enough to have input or output circuitry. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip.

From siliconvlsi.com

A survey on VLSI Floorplanning Siliconvlsi Power Pad In Vlsi The pad should be large enough to have input or output circuitry. These pads pass the power from outside of the chip to the power rings. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Pads are normally distributed around the edge of the ic. Many stacking layers for physical robustness.. Power Pad In Vlsi.

From www.vlsisystemdesign.com

Redefine pad placement using opensource EDA VLSI System Design Power Pad In Vlsi The pad should be large enough to have input or output circuitry. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Pads are normally distributed around the edge of the ic. So, power pads. Power Pad In Vlsi.

From www.slideserve.com

PPT VLSI Digital System Design PowerPoint Presentation, free download Power Pad In Vlsi Many stacking layers for physical robustness. The board uses 1 oz copper (1.4 mils thick) and. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Basically a big (100um x 100um) piece of metal. Power pads are placed along with io pads in the pads section of the full chip. So, power. Power Pad In Vlsi.

From present5.com

KLMH VLSI Physical Design From Graph Partitioning Power Pad In Vlsi Power pads are placed along with io pads in the pads section of the full chip. Basically a big (100um x 100um) piece of metal. By reducing the voltage difference between local power. So, power pads act as a bridge to pass the power from the outside to the chip. Many stacking layers for physical robustness. The pad should be. Power Pad In Vlsi.

From www.youtube.com

VLSI Design Lab Project SAR ADC YouTube Power Pad In Vlsi The board uses 1 oz copper (1.4 mils thick) and. These pads pass the power from outside of the chip to the power rings. So, power pads act as a bridge to pass the power from the outside to the chip. Power pads are placed along with io pads in the pads section of the full chip. By reducing the. Power Pad In Vlsi.

From mungfali.com

VLSI Circuits Power Pad In Vlsi Basically a big (100um x 100um) piece of metal. So, power pads act as a bridge to pass the power from the outside to the chip. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. By reducing the voltage difference between local power. The pad should be large enough to have. Power Pad In Vlsi.

From www.vlsisystemdesign.com

Think about preplaced cells and power ring generation in opensource Power Pad In Vlsi Power pads are placed along with io pads in the pads section of the full chip. Pads are normally distributed around the edge of the ic. By reducing the voltage difference between local power. The pad should be large enough to have input or output circuitry. The board uses 1 oz copper (1.4 mils thick) and. Steady state ir drop. Power Pad In Vlsi.

From www.slideserve.com

PPT Design and Implementation of VLSI Systems (EN1600) Lecture 32 Power Pad In Vlsi Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. By reducing the voltage difference between local power. So, power pads act as a bridge to pass the power from the outside to the chip. The pad should be large enough to have input or output circuitry. Many stacking layers for physical robustness.. Power Pad In Vlsi.

From www.vrogue.co

Asic System On Chip Vlsi Design Power Planning vrogue.co Power Pad In Vlsi The board uses 1 oz copper (1.4 mils thick) and. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. By reducing the voltage difference between local power. Power pads are placed along with io pads in the pads section of the full chip. Pads are normally distributed around the edge of. Power Pad In Vlsi.

From teamvlsi.com

Well Tap Cells in Physical Design Team VLSI Power Pad In Vlsi The pad should be large enough to have input or output circuitry. Power pads are placed along with io pads in the pads section of the full chip. These pads pass the power from outside of the chip to the power rings. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Basically. Power Pad In Vlsi.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Lecture 20 Package, Power, and Power Pad In Vlsi Many stacking layers for physical robustness. These pads pass the power from outside of the chip to the power rings. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. By reducing the voltage difference between local power. The board uses 1 oz copper (1.4 mils thick) and. Basically a big (100um x. Power Pad In Vlsi.

From present5.com

VLSI Design Chapter 5 CMOS Circuit and Logic Power Pad In Vlsi The board uses 1 oz copper (1.4 mils thick) and. Basically a big (100um x 100um) piece of metal. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Power pads are placed along with. Power Pad In Vlsi.

From vlsibyjim.blogspot.com

VLSI Basics Power Planning Power Pad In Vlsi Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. These pads pass the power from outside of the chip to the power rings. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. So, power pads act as a bridge to pass the power. Power Pad In Vlsi.

From vlsitalks.com

POWER PLAN VLSI TALKS Power Pad In Vlsi Many stacking layers for physical robustness. These pads pass the power from outside of the chip to the power rings. The pad should be large enough to have input or output circuitry. By reducing the voltage difference between local power. Power pads are placed along with io pads in the pads section of the full chip. Pads are normally distributed. Power Pad In Vlsi.

From www.slideserve.com

PPT VLSI Design Chapter 5 CMOS Circuit and Logic Design PowerPoint Power Pad In Vlsi The board uses 1 oz copper (1.4 mils thick) and. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Power pads are placed along with io pads in the pads section of the full chip. Basically a big (100um x 100um) piece of metal. Many stacking layers for physical robustness. So,. Power Pad In Vlsi.

From siliconvlsi.com

How to reduce shortcircuit power in VLSI? Siliconvlsi Power Pad In Vlsi The pad should be large enough to have input or output circuitry. Power pads are placed along with io pads in the pads section of the full chip. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Basically a big (100um x 100um) piece of metal. The board uses 1 oz. Power Pad In Vlsi.

From www.vlsisystemdesign.com

Preroute Power Nets and Power Grid Generation contest VLSI System Design Power Pad In Vlsi These pads pass the power from outside of the chip to the power rings. So, power pads act as a bridge to pass the power from the outside to the chip. By reducing the voltage difference between local power. Power pads are placed along with io pads in the pads section of the full chip. Power planning in vlsi physical. Power Pad In Vlsi.

From ece.umd.edu

VLSI Layout of a full chip with ring oscillators and pads Power Pad In Vlsi Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. So, power pads act as a bridge to pass the power from the outside to the chip. Pads are normally distributed around the edge of the ic. The pad should be large enough to have input or output circuitry. Steady state ir drop. Power Pad In Vlsi.

From slideplayer.com

ELEC 7770 Advanced VLSI Design Spring 2016 Power and Ground ppt download Power Pad In Vlsi So, power pads act as a bridge to pass the power from the outside to the chip. These pads pass the power from outside of the chip to the power rings. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. The pad should be large enough to have input or output. Power Pad In Vlsi.

From www.vlsisystemdesign.com

pad placement location VLSI System Design Power Pad In Vlsi Many stacking layers for physical robustness. By reducing the voltage difference between local power. Basically a big (100um x 100um) piece of metal. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. So, power pads act as a bridge to pass the power from the outside to the chip. These pads. Power Pad In Vlsi.

From www.slideserve.com

PPT AreaI/O FlipChip Routing for ChipPackage CoDesign PowerPoint Power Pad In Vlsi These pads pass the power from outside of the chip to the power rings. The board uses 1 oz copper (1.4 mils thick) and. Pads are normally distributed around the edge of the ic. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. The pad should be large enough to have input. Power Pad In Vlsi.

From www.youtube.com

VLSI Physical Design Powerplan YouTube Power Pad In Vlsi So, power pads act as a bridge to pass the power from the outside to the chip. Basically a big (100um x 100um) piece of metal. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Power pads are placed along with io pads in the pads section of the full chip. Steady. Power Pad In Vlsi.

From www.semanticscholar.org

Power Grid Analysis In VLSI Designs Semantic Scholar Power Pad In Vlsi Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. So, power pads act as a bridge to pass the power from the outside to the chip. Power pads are placed along with io pads in the pads section of the full chip. The board uses 1 oz copper (1.4 mils thick) and.. Power Pad In Vlsi.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Package, Power, and I/O Power Pad In Vlsi The pad should be large enough to have input or output circuitry. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Power pads are placed along with io pads in the pads section of. Power Pad In Vlsi.

From vlsibegin.blogspot.com

Powerplanning Power Pad In Vlsi Pads are normally distributed around the edge of the ic. The board uses 1 oz copper (1.4 mils thick) and. These pads pass the power from outside of the chip to the power rings. Power pads are placed along with io pads in the pads section of the full chip. So, power pads act as a bridge to pass the. Power Pad In Vlsi.

From itech-science.blogspot.com

Role Of Vlsi Industry In India For Digital Revolution By Chandan Kumar Power Pad In Vlsi Power pads are placed along with io pads in the pads section of the full chip. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Many stacking layers for physical robustness. The board uses 1 oz copper (1.4 mils thick) and. So, power pads act as a bridge to pass the power. Power Pad In Vlsi.

From www.researchgate.net

VLSI chip floorplan showing multiple modulator drivers and receiver Power Pad In Vlsi Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Pads are normally distributed around the edge of the ic. The pad should be large enough to have input or output circuitry. These pads pass the power from outside of the chip to the power rings. By reducing the voltage difference between. Power Pad In Vlsi.

From siliconvlsi.com

What is power planning in VLSI? Siliconvlsi Power Pad In Vlsi So, power pads act as a bridge to pass the power from the outside to the chip. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Many stacking layers for physical robustness. Pads are normally distributed around the edge of the ic. Power pads are placed along with io pads in the. Power Pad In Vlsi.

From individual.utoronto.ca

ECE1388 VLSI Design Methodology Final Project Power Pad In Vlsi Power pads are placed along with io pads in the pads section of the full chip. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Pads are normally distributed around the edge of the ic. Basically a big (100um x 100um) piece of metal. These pads pass the power from outside of. Power Pad In Vlsi.

From hernan.de

Grant H. CRC32 VLSI Design using Cadence's Virtuoso Power Pad In Vlsi The board uses 1 oz copper (1.4 mils thick) and. Power planning in vlsi physical design is the hidden hero behind every reliable and efficient vlsi chip. Many stacking layers for physical robustness. Basically a big (100um x 100um) piece of metal. So, power pads act as a bridge to pass the power from the outside to the chip. Power. Power Pad In Vlsi.

From studylib.net

Multipads, single layer power net routing in VLSI circuits Power Pad In Vlsi Power pads are placed along with io pads in the pads section of the full chip. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. So, power pads act as a bridge to pass the power from the outside to the chip. By reducing the voltage difference between local power. Power. Power Pad In Vlsi.

From www.zerotoasiccourse.com

Padring Zero to ASIC Course Power Pad In Vlsi Basically a big (100um x 100um) piece of metal. By reducing the voltage difference between local power. So, power pads act as a bridge to pass the power from the outside to the chip. Pads are normally distributed around the edge of the ic. Many stacking layers for physical robustness. Power pads are placed along with io pads in the. Power Pad In Vlsi.

From www.slideserve.com

PPT Progettazione di circuiti e sistemi VLSI PowerPoint Presentation Power Pad In Vlsi So, power pads act as a bridge to pass the power from the outside to the chip. These pads pass the power from outside of the chip to the power rings. Basically a big (100um x 100um) piece of metal. Pads are normally distributed around the edge of the ic. Steady state ir drop is caused by the resistance of. Power Pad In Vlsi.

From ivlsi.com

Power in VLSI Physical Design Power Pad In Vlsi The board uses 1 oz copper (1.4 mils thick) and. Power pads are placed along with io pads in the pads section of the full chip. Pads are normally distributed around the edge of the ic. Steady state ir drop is caused by the resistance of the metal wires comprising the power distribution network. Many stacking layers for physical robustness.. Power Pad In Vlsi.

From www.vlsisystemdesign.com

Redefine pad placement using opensource EDA VLSI System Design Power Pad In Vlsi The pad should be large enough to have input or output circuitry. Power pads are placed along with io pads in the pads section of the full chip. So, power pads act as a bridge to pass the power from the outside to the chip. The board uses 1 oz copper (1.4 mils thick) and. Many stacking layers for physical. Power Pad In Vlsi.