Transmission Gate Logical Effort . The method of logical effort is an easy way to estimate delay in a cmos circuit. The logical effort of a gate is the slope of the delay vs. We can select the fastest candidate by comparing delay. Path effective fanout (path electrical effort) is f = cl/c [1] g1. Path delay (equation derivation) the path logical effort, g = g. Fanout for the gate, divided by the slope for an inverter. It is easy to estimate this. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Every gate is sized according to a 2:1 min.

from eevibes.com

Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Fanout for the gate, divided by the slope for an inverter. We can select the fastest candidate by comparing delay. The method of logical effort is an easy way to estimate delay in a cmos circuit. Path effective fanout (path electrical effort) is f = cl/c [1] g1. It is easy to estimate this. Path delay (equation derivation) the path logical effort, g = g. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. The logical effort of a gate is the slope of the delay vs. Every gate is sized according to a 2:1 min.

What is Logical effort? How it effects the speed of digital circuitry

Transmission Gate Logical Effort It is easy to estimate this. We can select the fastest candidate by comparing delay. Fanout for the gate, divided by the slope for an inverter. The method of logical effort is an easy way to estimate delay in a cmos circuit. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Path delay (equation derivation) the path logical effort, g = g. Path effective fanout (path electrical effort) is f = cl/c [1] g1. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. It is easy to estimate this. The logical effort of a gate is the slope of the delay vs. Every gate is sized according to a 2:1 min.

From www.circuitdiagram.co

Cmos Transmission Gate Circuit Circuit Diagram Transmission Gate Logical Effort The method of logical effort is an easy way to estimate delay in a cmos circuit. The logical effort of a gate is the slope of the delay vs. Path effective fanout (path electrical effort) is f = cl/c [1] g1. Path delay (equation derivation) the path logical effort, g = g. Every gate is sized according to a 2:1. Transmission Gate Logical Effort.

From www.numerade.com

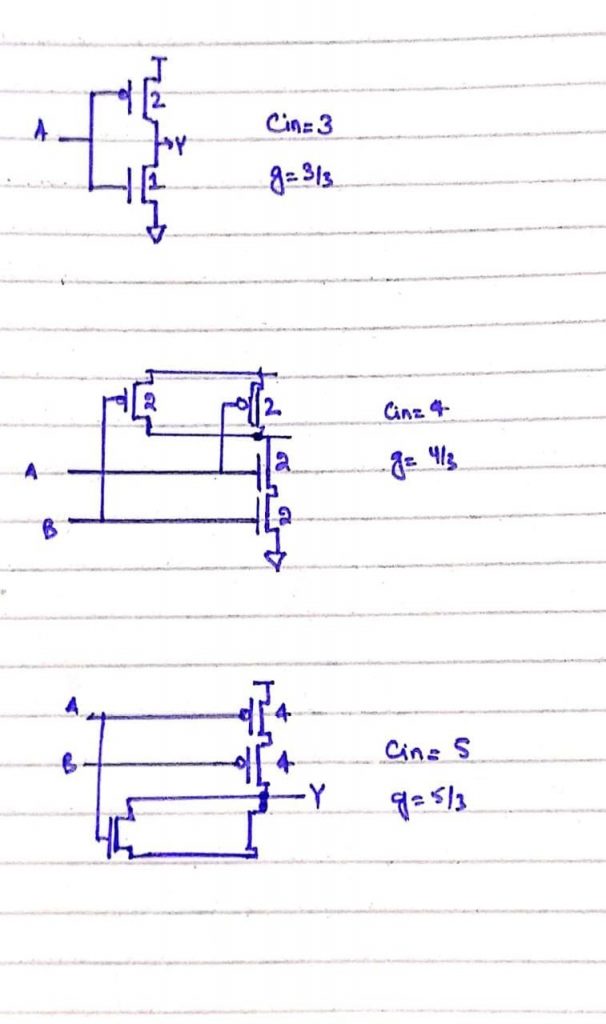

SOLVED Find the (a) Input capacitance (b) logical effort (c) parasitic Transmission Gate Logical Effort Path delay (equation derivation) the path logical effort, g = g. Every gate is sized according to a 2:1 min. Fanout for the gate, divided by the slope for an inverter. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Path effective fanout (path electrical. Transmission Gate Logical Effort.

From slideplayer.com

Copyright © 2004 The McGrawHill Companies, Inc. All rights reserved Transmission Gate Logical Effort Path effective fanout (path electrical effort) is f = cl/c [1] g1. Path delay (equation derivation) the path logical effort, g = g. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. The logical effort of a gate is the slope of the delay vs.. Transmission Gate Logical Effort.

From www.slideserve.com

PPT EE466 VLSI Design Lecture 6 Logical Effort PowerPoint Transmission Gate Logical Effort Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. It is easy to estimate this. The logical effort of a gate is the slope of the delay vs. Every gate is sized according to a 2:1 min. Fanout for the gate, divided by the slope. Transmission Gate Logical Effort.

From www.semanticscholar.org

Figure 1 from A High Speed Transmission Gate Logic Base 1/N Frequency Transmission Gate Logical Effort The method of logical effort is an easy way to estimate delay in a cmos circuit. We can select the fastest candidate by comparing delay. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Path effective fanout (path electrical effort) is f = cl/c [1]. Transmission Gate Logical Effort.

From www.slideserve.com

PPT EE466 VLSI Design Lecture 6 Logical Effort PowerPoint Transmission Gate Logical Effort Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. The logical effort of a gate is the slope of the delay vs. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. Fanout. Transmission Gate Logical Effort.

From eevibes.com

What is Logical effort? How it effects the speed of digital circuitry Transmission Gate Logical Effort Fanout for the gate, divided by the slope for an inverter. It is easy to estimate this. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. The logical effort of a gate is the slope of the delay vs. Every gate is sized according to a 2:1. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Pass Transistor Logic PowerPoint Presentation ID6783564 Transmission Gate Logical Effort It is easy to estimate this. Every gate is sized according to a 2:1 min. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output. Transmission Gate Logical Effort.

From www.youtube.com

Switch logic Pass Transistor & Transmission Gate VLSI Lec53 Transmission Gate Logical Effort It is easy to estimate this. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. We can select the fastest candidate by comparing delay. Path effective fanout (path electrical effort) is f = cl/c [1] g1. Logical effort is the ratio of the input capacitance. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Lecture 5 Logical Effort Transmission Gate Logical Effort Path effective fanout (path electrical effort) is f = cl/c [1] g1. Fanout for the gate, divided by the slope for an inverter. It is easy to estimate this. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. We can select the fastest candidate by. Transmission Gate Logical Effort.

From www.slideserve.com

PPT CMOS Transmission Gate PowerPoint Presentation, free download Transmission Gate Logical Effort Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. The method of logical effort is an easy way to estimate delay in a cmos circuit. Fanout for the gate, divided by the slope for an inverter. The logical effort of a gate is the slope. Transmission Gate Logical Effort.

From www.semanticscholar.org

Figure 1 from Performance evaluation of full adders in ASIC using Transmission Gate Logical Effort Every gate is sized according to a 2:1 min. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. The logical effort of a gate is the slope of the delay vs. It is easy to estimate this. Path effective fanout (path electrical effort) is f = cl/c. Transmission Gate Logical Effort.

From www.studypool.com

SOLUTION 12 pass transistor and transmission gate logic circuits Transmission Gate Logical Effort Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. The logical effort of a gate is the slope of the delay vs. Path effective fanout (path electrical effort) is f = cl/c [1] g1. Path delay (equation derivation) the path logical effort, g = g.. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Chapter 02 Logic Design with MOSFETs PowerPoint Presentation Transmission Gate Logical Effort Every gate is sized according to a 2:1 min. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. Path effective fanout (path electrical. Transmission Gate Logical Effort.

From www.scribd.com

L16 GatesLogical Effort Parasitic Delay PDF Transmission Gate Logical Effort The method of logical effort is an easy way to estimate delay in a cmos circuit. We can select the fastest candidate by comparing delay. It is easy to estimate this. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Logical effort is the ratio. Transmission Gate Logical Effort.

From www.slideserve.com

PPT PassTransistor Logic PowerPoint Presentation, free download ID Transmission Gate Logical Effort We can select the fastest candidate by comparing delay. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. Path effective fanout (path electrical. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Designing Combinational Logic Circuits PowerPoint Presentation Transmission Gate Logical Effort We can select the fastest candidate by comparing delay. It is easy to estimate this. Path effective fanout (path electrical effort) is f = cl/c [1] g1. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Fanout for the gate, divided by the slope for. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Logic Gate Delay Modeling 1 PowerPoint Presentation, free Transmission Gate Logical Effort The logical effort of a gate is the slope of the delay vs. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. The method of logical effort is an easy way to estimate delay in a cmos circuit. Every gate is sized according to a. Transmission Gate Logical Effort.

From cegpgxiv.blob.core.windows.net

Transmission Gate Transistor Sizing at Abby Welch blog Transmission Gate Logical Effort The method of logical effort is an easy way to estimate delay in a cmos circuit. Every gate is sized according to a 2:1 min. Path delay (equation derivation) the path logical effort, g = g. We can select the fastest candidate by comparing delay. It is easy to estimate this. Logical effort is the ratio of the input capacitance. Transmission Gate Logical Effort.

From exyfedfbc.blob.core.windows.net

Transmission Gate Logic Truth Table at Betty Reuter blog Transmission Gate Logical Effort Fanout for the gate, divided by the slope for an inverter. Every gate is sized according to a 2:1 min. The method of logical effort is an easy way to estimate delay in a cmos circuit. Path effective fanout (path electrical effort) is f = cl/c [1] g1. We can select the fastest candidate by comparing delay. Logical effort is. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Lecture 6 Logical Effort PowerPoint Presentation, free download Transmission Gate Logical Effort Fanout for the gate, divided by the slope for an inverter. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. It is easy to estimate this. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter. Transmission Gate Logical Effort.

From www.youtube.com

CMOS Transmission Gate Logic (PART 1) Day On My Plate VLSI Design Transmission Gate Logical Effort Fanout for the gate, divided by the slope for an inverter. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. Path effective fanout (path electrical effort) is f = cl/c [1] g1. The method of logical effort is an easy way to estimate delay in a cmos. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Lecture 10 Circuit Families PowerPoint Presentation, free Transmission Gate Logical Effort Path effective fanout (path electrical effort) is f = cl/c [1] g1. The method of logical effort is an easy way to estimate delay in a cmos circuit. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. Fanout for the gate, divided by the slope for an. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Logical Effort A Method to Optimize Circuit Topology PowerPoint Transmission Gate Logical Effort Path effective fanout (path electrical effort) is f = cl/c [1] g1. Path delay (equation derivation) the path logical effort, g = g. The method of logical effort is an easy way to estimate delay in a cmos circuit. We can select the fastest candidate by comparing delay. Fanout for the gate, divided by the slope for an inverter. The. Transmission Gate Logical Effort.

From www.chegg.com

Solved Problem 3 Transmission Gate, Logical Effort Transmission Gate Logical Effort We can select the fastest candidate by comparing delay. The method of logical effort is an easy way to estimate delay in a cmos circuit. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Path effective fanout (path electrical effort) is f = cl/c [1]. Transmission Gate Logical Effort.

From www.chegg.com

1. (30 pts.) [Logical Effort of CMOS + Transmission Transmission Gate Logical Effort Path delay (equation derivation) the path logical effort, g = g. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. It is easy to estimate this. We can select the fastest candidate by comparing delay. Path effective fanout (path electrical effort) is f = cl/c. Transmission Gate Logical Effort.

From www.circuitdiagram.co

Circuit Diagram For Xnor Gate Circuit Diagram Transmission Gate Logical Effort Path delay (equation derivation) the path logical effort, g = g. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Every gate is sized according to a 2:1 min. Logical effort is the ratio of the input capacitance of a gate to the input capacitance. Transmission Gate Logical Effort.

From www.allaboutcircuits.com

The CMOS Transmission Gate Transmission Gate Logical Effort The method of logical effort is an easy way to estimate delay in a cmos circuit. We can select the fastest candidate by comparing delay. Path delay (equation derivation) the path logical effort, g = g. The logical effort of a gate is the slope of the delay vs. Logical effort is the ratio of the input capacitance of a. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Chapter 7 Complementary MOS (CMOS) Logic Design PowerPoint Transmission Gate Logical Effort The method of logical effort is an easy way to estimate delay in a cmos circuit. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. We can select the fastest candidate by comparing delay. Path delay (equation derivation) the path logical effort, g = g.. Transmission Gate Logical Effort.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Lecture 5 Logical Effort Transmission Gate Logical Effort Path delay (equation derivation) the path logical effort, g = g. The method of logical effort is an easy way to estimate delay in a cmos circuit. It is easy to estimate this. Fanout for the gate, divided by the slope for an inverter. Logical effort is the ratio of the input capacitance of a gate to the input capacitance. Transmission Gate Logical Effort.

From www.studypool.com

SOLUTION 12 pass transistor and transmission gate logic circuits Transmission Gate Logical Effort Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. The method of logical effort is an easy way to estimate delay in a cmos circuit. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering. Transmission Gate Logical Effort.

From www.chegg.com

Solved Logic Effort In this problem, you will design a Transmission Gate Logical Effort Every gate is sized according to a 2:1 min. It is easy to estimate this. Path effective fanout (path electrical effort) is f = cl/c [1] g1. The method of logical effort is an easy way to estimate delay in a cmos circuit. We can select the fastest candidate by comparing delay. Logical effort is the ratio of the input. Transmission Gate Logical Effort.

From www.youtube.com

Transmission Gate logic Implement Logic Gates using Transmission Transmission Gate Logical Effort It is easy to estimate this. The method of logical effort is an easy way to estimate delay in a cmos circuit. Path effective fanout (path electrical effort) is f = cl/c [1] g1. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same. We can select the. Transmission Gate Logical Effort.

From www.chegg.com

Solved Write logic output function for the following Transmission Gate Logical Effort The logical effort of a gate is the slope of the delay vs. It is easy to estimate this. Fanout for the gate, divided by the slope for an inverter. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. Logical effort is the ratio of. Transmission Gate Logical Effort.

From www.chegg.com

4.16 Find the parasitic delay and logical effort of Transmission Gate Logical Effort Every gate is sized according to a 2:1 min. Path delay (equation derivation) the path logical effort, g = g. Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. We can select the fastest candidate by comparing delay. The method of logical effort is an. Transmission Gate Logical Effort.