Transistors Density In Vlsi . Technology scaling has a threefold objective: the most accurate and meaningful metric for density is the number of transistors on the chip area. the basic properties of transistors are clearly important for logic design. Function of how fast a logic gate can change input voltage of another downstream gate. Built by jack kilby at texas instruments 2003. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. speed or clock rate of a circuit. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm.

from www.mdpi.com

Built by jack kilby at texas instruments 2003. Function of how fast a logic gate can change input voltage of another downstream gate. the most accurate and meaningful metric for density is the number of transistors on the chip area. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. speed or clock rate of a circuit. the basic properties of transistors are clearly important for logic design. Technology scaling has a threefold objective:

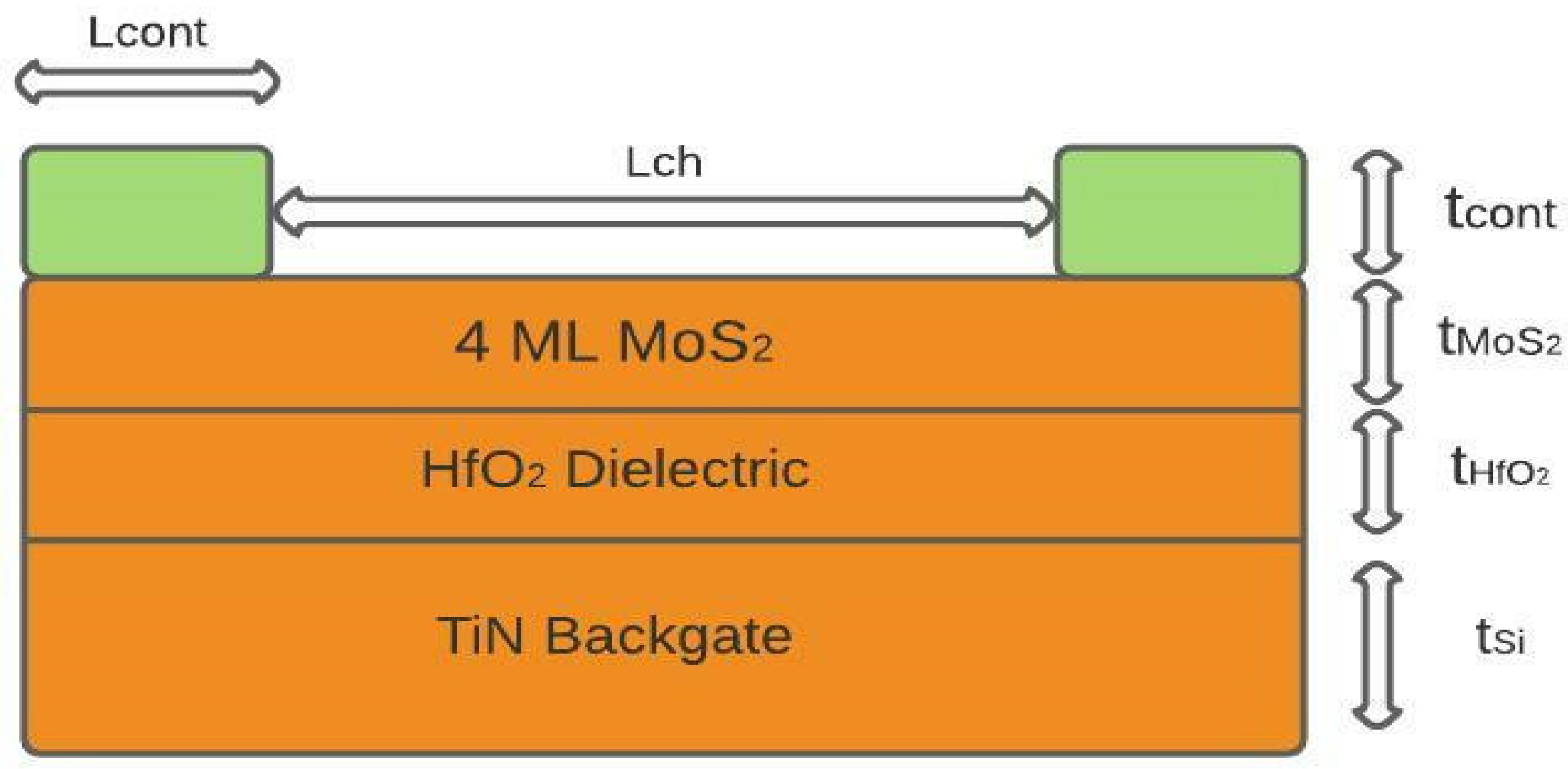

Micromachines Free FullText Effects of Channel Length Scaling on

Transistors Density In Vlsi the most accurate and meaningful metric for density is the number of transistors on the chip area. the basic properties of transistors are clearly important for logic design. speed or clock rate of a circuit. the most accurate and meaningful metric for density is the number of transistors on the chip area. Built by jack kilby at texas instruments 2003. Technology scaling has a threefold objective: Function of how fast a logic gate can change input voltage of another downstream gate. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model.

From www.researchgate.net

Transistors and component density advances in semiconductors (above Transistors Density In Vlsi Built by jack kilby at texas instruments 2003. the basic properties of transistors are clearly important for logic design. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. the most accurate and meaningful metric for density is the number of transistors on the chip area. speed. Transistors Density In Vlsi.

From semiwiki.com

Effect of Design on Transistor Density Read more on SemiWiki Transistors Density In Vlsi Function of how fast a logic gate can change input voltage of another downstream gate. the basic properties of transistors are clearly important for logic design. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. . Transistors Density In Vlsi.

From www.researchgate.net

(a) The evolution of transistor density scaling. Reprinted with Transistors Density In Vlsi speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Function of how fast a logic gate can change input voltage of another downstream gate. the basic properties of. Transistors Density In Vlsi.

From present5.com

KLMH VLSI Physical Design From Graph Partitioning Transistors Density In Vlsi the basic properties of transistors are clearly important for logic design. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. Technology scaling has a threefold objective: in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit. Transistors Density In Vlsi.

From slides.com

Moore's Law Transistors Density In Vlsi Technology scaling has a threefold objective: the basic properties of transistors are clearly important for logic design. Built by jack kilby at texas instruments 2003. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. Function of how fast a logic gate can change input voltage of another downstream. Transistors Density In Vlsi.

From www.researchgate.net

2 Historical development of Density trends. (a) Transistor density Transistors Density In Vlsi in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. the most accurate and meaningful metric for density is the number of transistors on the chip area. Function of how fast a logic gate can change input. Transistors Density In Vlsi.

From www.researchgate.net

Evolution of the Field Effect Transistor (FET) Architecture. The single Transistors Density In Vlsi Technology scaling has a threefold objective: in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Function of how fast a logic gate can change input voltage of another downstream gate. the most accurate and meaningful metric. Transistors Density In Vlsi.

From slideplayer.com

Introduction to VLSI CMPE/ELEE 4375 Introduction ppt download Transistors Density In Vlsi the most accurate and meaningful metric for density is the number of transistors on the chip area. Built by jack kilby at texas instruments 2003. the basic properties of transistors are clearly important for logic design. speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of. Transistors Density In Vlsi.

From www.researchgate.net

Ranges of the Transistor's Chart Density Download Scientific Diagram Transistors Density In Vlsi the basic properties of transistors are clearly important for logic design. speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. the most accurate and meaningful metric for. Transistors Density In Vlsi.

From www.slideserve.com

PPT Basics of VLSI PowerPoint Presentation, free download ID7335645 Transistors Density In Vlsi the most accurate and meaningful metric for density is the number of transistors on the chip area. Function of how fast a logic gate can change input voltage of another downstream gate. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance. Transistors Density In Vlsi.

From www.tomshardware.com

Imec Reveals Sub1nm Transistor Roadmap, 3DStacked CMOS 2.0 Plans Transistors Density In Vlsi Technology scaling has a threefold objective: Built by jack kilby at texas instruments 2003. speed or clock rate of a circuit. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. the most accurate and meaningful metric for density is the number of transistors on the chip area.. Transistors Density In Vlsi.

From slideplayer.com

CSE477 VLSI Digital Circuits Fall Lecture 07 Pass Transistor Logic Transistors Density In Vlsi speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. the most accurate and meaningful metric for density is the number of transistors on the chip area. the. Transistors Density In Vlsi.

From www.vlsiuniverse.com

VLSI UNIVERSE Transistor sizing W/L CMOS VLSI Transistors Density In Vlsi transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. speed or clock rate of a circuit. the most accurate and meaningful metric for density is the number of transistors on the chip area. Function of how fast a logic gate can change input voltage of another downstream. Transistors Density In Vlsi.

From www.semanticscholar.org

Figure 1 from multiplevalued CAM for a collision Transistors Density In Vlsi Built by jack kilby at texas instruments 2003. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Function of how fast a logic gate can change input voltage of another downstream gate. speed or clock rate. Transistors Density In Vlsi.

From www.slideserve.com

PPT Analog VLSI Neural Circuits PowerPoint Presentation, free Transistors Density In Vlsi in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. speed or clock rate of a circuit. Built by jack kilby at texas instruments 2003. Technology scaling has a threefold objective: transistors with the size of. Transistors Density In Vlsi.

From semiengineering.com

Transistor Options Beyond 3nm Transistors Density In Vlsi transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. the basic properties of transistors are clearly important for logic design. Function of how fast a logic gate can change input voltage of another downstream gate. speed or clock rate of a circuit. Technology scaling has a threefold. Transistors Density In Vlsi.

From www.pinterest.com

Pin by Nancy on Vlsi Electronics circuit, Diodes, Capacitors Transistors Density In Vlsi speed or clock rate of a circuit. Technology scaling has a threefold objective: Built by jack kilby at texas instruments 2003. Function of how fast a logic gate can change input voltage of another downstream gate. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to. Transistors Density In Vlsi.

From freeradicalscience.com

New Organic Transistors Facilitate Higher Density Circuit Integration Transistors Density In Vlsi the most accurate and meaningful metric for density is the number of transistors on the chip area. Built by jack kilby at texas instruments 2003. Technology scaling has a threefold objective: Function of how fast a logic gate can change input voltage of another downstream gate. the basic properties of transistors are clearly important for logic design. . Transistors Density In Vlsi.

From www.science.org

Toward attojoule switching energy in logic transistors Science Transistors Density In Vlsi the most accurate and meaningful metric for density is the number of transistors on the chip area. Built by jack kilby at texas instruments 2003. Technology scaling has a threefold objective: speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a. Transistors Density In Vlsi.

From www.scribd.com

StickDiagrams (2) VLSI PDF Bipolar Junction Transistor Cmos Transistors Density In Vlsi Built by jack kilby at texas instruments 2003. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model.. Transistors Density In Vlsi.

From www.vlsiuniverse.com

Transistor sizing W/L CMOS VLSI VLSI UNIVERSE Transistors Density In Vlsi Built by jack kilby at texas instruments 2003. Technology scaling has a threefold objective: the basic properties of transistors are clearly important for logic design. speed or clock rate of a circuit. the most accurate and meaningful metric for density is the number of transistors on the chip area. transistors with the size of 50 μm. Transistors Density In Vlsi.

From www.slideshare.net

Fundamentals of CMOS VLSI Design and Mos Transistors Transistors Density In Vlsi speed or clock rate of a circuit. Built by jack kilby at texas instruments 2003. Technology scaling has a threefold objective: the most accurate and meaningful metric for density is the number of transistors on the chip area. Function of how fast a logic gate can change input voltage of another downstream gate. in this article, we. Transistors Density In Vlsi.

From www.youtube.com

VLSI Device Physics of Scaled Nanowire Field Effect Transistors with Transistors Density In Vlsi Built by jack kilby at texas instruments 2003. the most accurate and meaningful metric for density is the number of transistors on the chip area. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. Technology scaling has a threefold objective: the basic properties of transistors are clearly. Transistors Density In Vlsi.

From www.slideserve.com

PPT Basics of VLSI PowerPoint Presentation, free download ID7335645 Transistors Density In Vlsi Built by jack kilby at texas instruments 2003. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide. Transistors Density In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Gate arrays Transistors Density In Vlsi the basic properties of transistors are clearly important for logic design. Built by jack kilby at texas instruments 2003. the most accurate and meaningful metric for density is the number of transistors on the chip area. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit. Transistors Density In Vlsi.

From www.researchgate.net

(a) Transistor characteristics, (b) base current density, and (c Transistors Density In Vlsi the basic properties of transistors are clearly important for logic design. Technology scaling has a threefold objective: Built by jack kilby at texas instruments 2003. speed or clock rate of a circuit. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. the most accurate and meaningful. Transistors Density In Vlsi.

From www.mdpi.com

Micromachines Free FullText Effects of Channel Length Scaling on Transistors Density In Vlsi speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. the most accurate and meaningful metric for density is the number of transistors on the chip area. the. Transistors Density In Vlsi.

From www.researchgate.net

Density functional theory calculations and high‐density 2D transistor Transistors Density In Vlsi speed or clock rate of a circuit. Function of how fast a logic gate can change input voltage of another downstream gate. the most accurate and meaningful metric for density is the number of transistors on the chip area. the basic properties of transistors are clearly important for logic design. Built by jack kilby at texas instruments. Transistors Density In Vlsi.

From www.youtube.com

MOS transistor Structure Modes of operation VLSI Lec03 YouTube Transistors Density In Vlsi the basic properties of transistors are clearly important for logic design. Technology scaling has a threefold objective: Built by jack kilby at texas instruments 2003. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. transistors. Transistors Density In Vlsi.

From www.youtube.com

Limits on Logic levels and current density VLSI Lec52 YouTube Transistors Density In Vlsi Function of how fast a logic gate can change input voltage of another downstream gate. the most accurate and meaningful metric for density is the number of transistors on the chip area. Built by jack kilby at texas instruments 2003. speed or clock rate of a circuit. the basic properties of transistors are clearly important for logic. Transistors Density In Vlsi.

From www.researchgate.net

(a) The evolution of transistor density scaling. Reprinted with Transistors Density In Vlsi speed or clock rate of a circuit. Built by jack kilby at texas instruments 2003. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. the basic properties of transistors are clearly important for logic design.. Transistors Density In Vlsi.

From www.researchgate.net

The main parts of this review on 2D transistors for VLSI, including Transistors Density In Vlsi speed or clock rate of a circuit. transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. Function of how fast a logic gate can change input voltage of another downstream gate. Built by jack kilby at texas instruments 2003. in this article, we will learn how to. Transistors Density In Vlsi.

From www.researchgate.net

(PDF) Retrospective on VLSI value scaling and lithography Transistors Density In Vlsi Technology scaling has a threefold objective: speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Function of how fast a logic gate can change input voltage of another downstream. Transistors Density In Vlsi.

From www.slideserve.com

PPT VLSI Design Lecture 3a Nonideal Transistors PowerPoint Transistors Density In Vlsi transistors with the size of 50 μm in the 1960s have been scaled down to less than 15 nm. Technology scaling has a threefold objective: speed or clock rate of a circuit. the most accurate and meaningful metric for density is the number of transistors on the chip area. in this article, we will learn how. Transistors Density In Vlsi.

From www.semanticscholar.org

Figure 14 from Novel VerticalStackedArrayTransistor (VSAT) for ultra Transistors Density In Vlsi the basic properties of transistors are clearly important for logic design. speed or clock rate of a circuit. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. the most accurate and meaningful metric for. Transistors Density In Vlsi.