What Is A Clock Enable . A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. In my undergrad years, i was taught that since the clock. The r and ce inputs. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. R takes precedence over ce. I read in some forums that in asics, clock gating saves a lot more power than clock enable. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. You're right about a clock enable's function: But, an enable is a signal which makes the flipflop.

from webdocs.cs.ualberta.ca

The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. R takes precedence over ce. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. In my undergrad years, i was taught that since the clock. I read in some forums that in asics, clock gating saves a lot more power than clock enable. You're right about a clock enable's function: The r and ce inputs. It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. But, an enable is a signal which makes the flipflop.

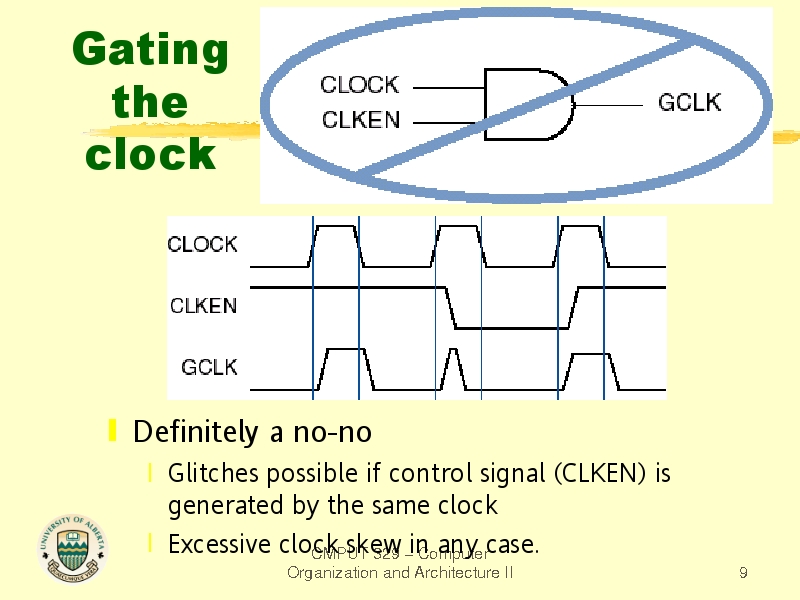

Gating the clock

What Is A Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. The r and ce inputs. It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. You're right about a clock enable's function: In my undergrad years, i was taught that since the clock. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). R takes precedence over ce. But, an enable is a signal which makes the flipflop. I read in some forums that in asics, clock gating saves a lot more power than clock enable. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals.

From www.comtechsolutions.com

Payroll > Time Clock > Enable Time Clock Hours Calculation What Is A Clock Enable But, an enable is a signal which makes the flipflop. I read in some forums that in asics, clock gating saves a lot more power than clock enable. R takes precedence over ce. The r and ce inputs. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as. What Is A Clock Enable.

From www.anuko.com

How to Enable Taskbar Clock What Is A Clock Enable You're right about a clock enable's function: A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). I read in some forums that in asics, clock gating saves a lot more power than clock enable. Hi, i have a state machine (with. What Is A Clock Enable.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire What Is A Clock Enable R takes precedence over ce. But, an enable is a signal which makes the flipflop. It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. The skew between the main clock and the divided clock will vary depending on the. What Is A Clock Enable.

From webdocs.cs.ualberta.ca

Gating the clock What Is A Clock Enable In my undergrad years, i was taught that since the clock. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). You're right about a clock enable's function: The skew between the main clock and the divided clock will vary depending on. What Is A Clock Enable.

From www.youtube.com

How To Enable / Disable 24 Hour Clock Format On Apple Watch 8 / Ultra What Is A Clock Enable I read in some forums that in asics, clock gating saves a lot more power than clock enable. The r and ce inputs. R takes precedence over ce. In my undergrad years, i was taught that since the clock. It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve. What Is A Clock Enable.

From www.nimblehand.com

How to Enable Clock on Your Android Lock Screen What Is A Clock Enable I read in some forums that in asics, clock gating saves a lot more power than clock enable. The r and ce inputs. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. But, an enable is a signal which makes. What Is A Clock Enable.

From help.exatouch.com

Manage the Time Clock Exatouch Knowledge Base What Is A Clock Enable A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). I read in some forums that in asics, clock gating saves a lot more power than clock enable. But, an enable is a signal which makes the flipflop. In my undergrad years,. What Is A Clock Enable.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch What Is A Clock Enable But, an enable is a signal which makes the flipflop. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any. What Is A Clock Enable.

From www.idownloadblog.com

iOS 7 the ultimate Clock app guide What Is A Clock Enable In my undergrad years, i was taught that since the clock. The r and ce inputs. It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. Hi, i have a state machine (with about 12 states), and there is an. What Is A Clock Enable.

From www.youtube.com

How To Enable Dual Clock on iPhone Lockscreen (easy) YouTube What Is A Clock Enable The r and ce inputs. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. You're right about a clock enable's function: Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside. What Is A Clock Enable.

From www.youtube.com

How to Generate a Clock Signal with a 555 timer The Learning Circuit What Is A Clock Enable In my undergrad years, i was taught that since the clock. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). The skew between the main clock and the divided clock will vary depending on the route, so you should treat them. What Is A Clock Enable.

From www.reddit.com

How to Enable Seconds in Windows 11 Taskbar Clock A StepbyStep Guide What Is A Clock Enable In my undergrad years, i was taught that since the clock. You're right about a clock enable's function: I read in some forums that in asics, clock gating saves a lot more power than clock enable. The r and ce inputs. But, an enable is a signal which makes the flipflop. The skew between the main clock and the divided. What Is A Clock Enable.

From dokumen.tips

(PDF) Clock Enable Timing Closure Methodology … Enable Timing Closure What Is A Clock Enable The r and ce inputs. R takes precedence over ce. I read in some forums that in asics, clock gating saves a lot more power than clock enable. In my undergrad years, i was taught that since the clock. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or. What Is A Clock Enable.

From www.youtube.com

How To enable Screen Off clock or Ambient Display OPPO Care YouTube What Is A Clock Enable The r and ce inputs. I read in some forums that in asics, clock gating saves a lot more power than clock enable. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. A clock (better represented as clk) is a signal which. What Is A Clock Enable.

From www.msftnext.com

How to enable seconds for taskbar clock in Windows 11 What Is A Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). R takes precedence. What Is A Clock Enable.

From www.youtube.com

Apple Watch Enable/Disable 24 Hour Clock (Series 6,5,4,3,SE) YouTube What Is A Clock Enable It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. R takes precedence. What Is A Clock Enable.

From www.slideserve.com

PPT Register Files and Memories PowerPoint Presentation, free What Is A Clock Enable I read in some forums that in asics, clock gating saves a lot more power than clock enable. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. Hi, i have a state machine (with about 12 states), and there is an enable. What Is A Clock Enable.

From www.slideserve.com

PPT Clock domains & divider Clock & reset distribution PowerPoint What Is A Clock Enable You're right about a clock enable's function: The r and ce inputs. In my undergrad years, i was taught that since the clock. I read in some forums that in asics, clock gating saves a lot more power than clock enable. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is. What Is A Clock Enable.

From timemachinescorp.com

The Benefits of WiFi Enabled Time Clocks What Is A Clock Enable You're right about a clock enable's function: But, an enable is a signal which makes the flipflop. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. A clock (better represented as clk) is a signal which is used to make the flipflop. What Is A Clock Enable.

From vlsimaster.com

Clock Gating VLSI Master What Is A Clock Enable The r and ce inputs. It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. R takes precedence over ce. In my undergrad years, i was taught that since the clock. A clock (better represented as clk) is a signal. What Is A Clock Enable.

From www.youtube.com

Enable Seconds In Windows 11 Taskbar Clock YouTube What Is A Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. R takes precedence over ce. But, an enable is a signal which makes the flipflop. I read in some forums that in asics, clock gating saves a lot more power than. What Is A Clock Enable.

From www.yumpu.com

Clock Enable Clock Gating What Is A Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). I read in. What Is A Clock Enable.

From www.youtube.com

How to Enable the Alarm Clock Feature within Windows 10 YouTube What Is A Clock Enable The r and ce inputs. It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside. What Is A Clock Enable.

From www.youtube.com

Clock buffer key parameters and specifications YouTube What Is A Clock Enable R takes precedence over ce. The r and ce inputs. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). In my undergrad years, i was taught that since the clock. It is recommended by both xilinx and altera to use clock. What Is A Clock Enable.

From www.researchgate.net

(PDF) Exploiting useful skew in gated low voltage clock trees What Is A Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. But, an enable is a signal which makes the flipflop. R takes precedence over ce. The r and ce inputs. You're right about a clock enable's function: It is recommended by. What Is A Clock Enable.

From klamtnsmb.blob.core.windows.net

What Is Clock Enable at Hanna Nunley blog What Is A Clock Enable It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. You're right about a clock enable's function: A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge. What Is A Clock Enable.

From www.youtube.com

How to Enable Clock with Seconds in System Tray in Windows 11 25247 What Is A Clock Enable I read in some forums that in asics, clock gating saves a lot more power than clock enable. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). R takes precedence over ce. Hi, i have a state machine (with about 12. What Is A Clock Enable.

From www.electronicsforu.com

Clock Gating for the of Things Design Guide What Is A Clock Enable You're right about a clock enable's function: Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks. What Is A Clock Enable.

From itstechbased.com

How to Enable Clock with Seconds in Windows 11 Main Release Tech Based What Is A Clock Enable It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. The r and ce inputs. But, an enable is a signal which makes the flipflop. R takes precedence over ce. You're right about a clock enable's function: A clock (better. What Is A Clock Enable.

From www.slideserve.com

PPT EKT 124 / 3 DIGITAL ELEKTRONIC 1 PowerPoint Presentation, free What Is A Clock Enable You're right about a clock enable's function: R takes precedence over ce. But, an enable is a signal which makes the flipflop. I read in some forums that in asics, clock gating saves a lot more power than clock enable. The r and ce inputs. In my undergrad years, i was taught that since the clock. A clock (better represented. What Is A Clock Enable.

From www.youtube.com

Enable Dual Clocks on any iPhone Lockscreen [ iOS 16 ] Dual Clock Now What Is A Clock Enable The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. In my undergrad years, i was taught that since the clock. But, an enable is a signal which makes the flipflop. I read in some forums that in asics, clock gating saves a. What Is A Clock Enable.

From hohpasavvy.weebly.com

Hot alarm clock enable sleep mode windows hohpasavvy What Is A Clock Enable The r and ce inputs. You're right about a clock enable's function: Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources. What Is A Clock Enable.

From www.slideserve.com

PPT Clock domains & divider Clock & reset distribution PowerPoint What Is A Clock Enable The r and ce inputs. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge (in exceptional case both edge). R takes precedence over ce. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any. What Is A Clock Enable.

From www.youtube.com

How to Enable Dual Clock on any iPhone 13 [iOS 16] YouTube What Is A Clock Enable The skew between the main clock and the divided clock will vary depending on the route, so you should treat them as unrelated clocks and handle signals. You're right about a clock enable's function: The r and ce inputs. In my undergrad years, i was taught that since the clock. Hi, i have a state machine (with about 12 states),. What Is A Clock Enable.

From slideplayer.com

I2C Protocol and RTC Interfacing ppt download What Is A Clock Enable You're right about a clock enable's function: It is recommended by both xilinx and altera to use clock enable, which can help save fpga clock resources and improve fpga timing characteristics and timing analysis of the design. A clock (better represented as clk) is a signal which is used to make the flipflop work at its positive or negative edge. What Is A Clock Enable.