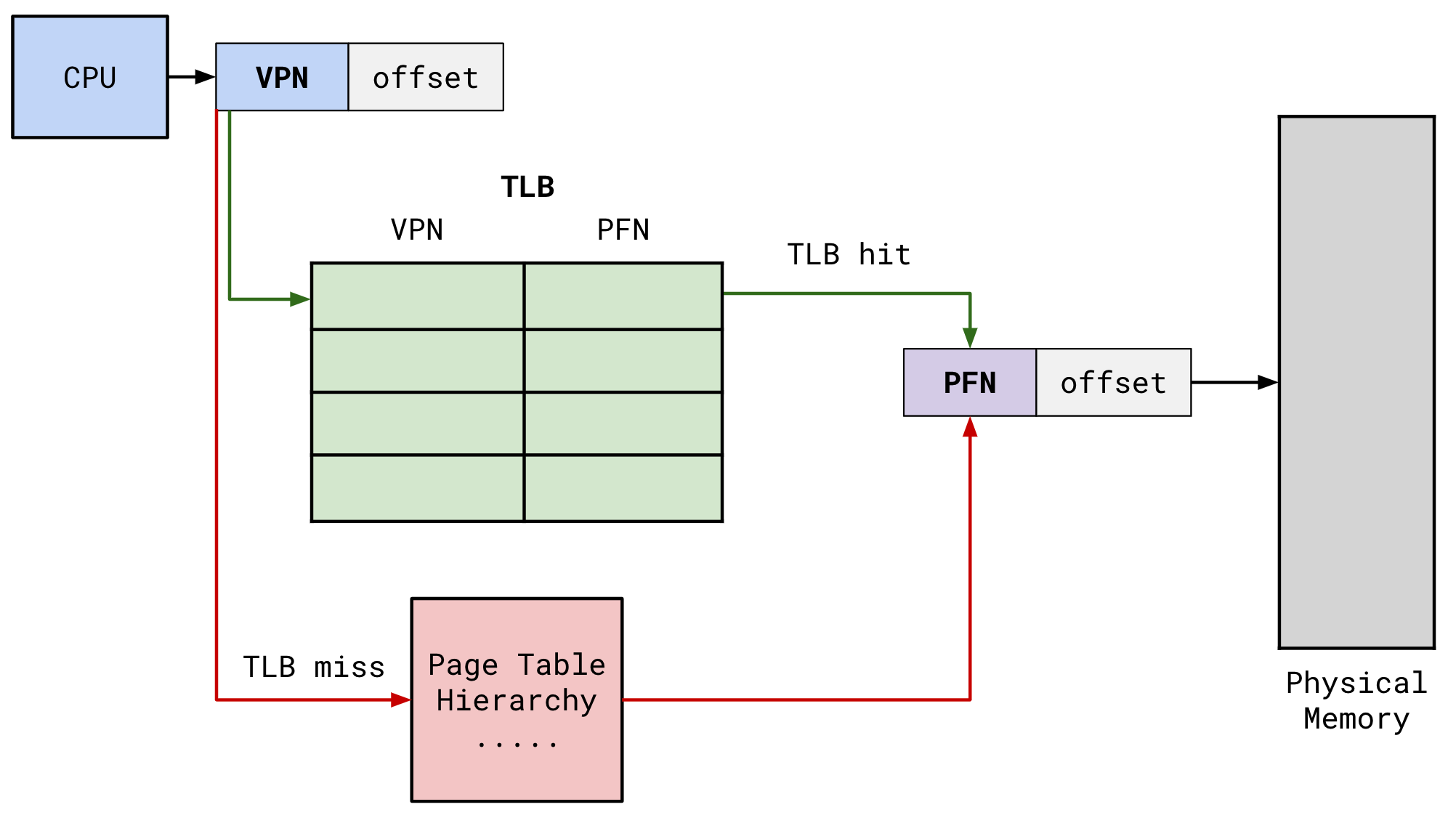

Paging Hardware With Tlb In Os . paging hardware with tlb. Memory protection implemented by associating protection bit with each frame. Divide physical memory into frames: the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. But, page tables consume memory for lifetime of vas. Easy to address, no translation required. Size is power of 2, between 512 bytes and 8,192 bytes. full course of operating system: It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance.

from cs4118.github.io

Easy to address, no translation required. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. Memory protection implemented by associating protection bit with each frame. the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. Divide physical memory into frames: But, page tables consume memory for lifetime of vas. full course of operating system: Size is power of 2, between 512 bytes and 8,192 bytes. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again.

Translation Lookaside Buffer (TLB) COMS W4118 Operating Systems I

Paging Hardware With Tlb In Os Size is power of 2, between 512 bytes and 8,192 bytes. Divide physical memory into frames: paging hardware with tlb. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. Easy to address, no translation required. full course of operating system: the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Memory protection implemented by associating protection bit with each frame. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. Size is power of 2, between 512 bytes and 8,192 bytes. But, page tables consume memory for lifetime of vas.

From www.slideserve.com

PPT Segmentation PowerPoint Presentation, free download ID455392 Paging Hardware With Tlb In Os Divide physical memory into frames: full course of operating system: Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. Easy to address, no translation required. But, page tables consume memory for lifetime of vas. paging hardware with tlb. the translation lookaside buffer (tlb) is a vital component in. Paging Hardware With Tlb In Os.

From www.youtube.com

Memory management Part 4 Hardware Support for Paging TLB YouTube Paging Hardware With Tlb In Os It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. full course of operating system: Size is power of 2, between 512 bytes and 8,192 bytes. But, page tables consume memory for lifetime of vas. Divide physical memory into frames:. Paging Hardware With Tlb In Os.

From www.scaler.com

Paging in OS Scaler Topics Paging Hardware With Tlb In Os full course of operating system: paging hardware with tlb. the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. Memory protection implemented by associating protection bit with each frame. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to. Paging Hardware With Tlb In Os.

From www.geeksforgeeks.org

Difference between Paging and Swapping in OS Paging Hardware With Tlb In Os a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Memory protection implemented by associating protection bit with each frame. But, page tables consume memory for lifetime of vas. Easy to address, no translation required. paging hardware with tlb.. Paging Hardware With Tlb In Os.

From byjus.com

Paging in OS GATE Notes Paging Hardware With Tlb In Os Memory protection implemented by associating protection bit with each frame. But, page tables consume memory for lifetime of vas. paging hardware with tlb. full course of operating system: Easy to address, no translation required. Divide physical memory into frames: a translation look aside buffer can be defined as a memory cache which can be used to reduce. Paging Hardware With Tlb In Os.

From devfancy.github.io

19. TLB(Translation Lookaside Buffers) Paging Hardware With Tlb In Os Size is power of 2, between 512 bytes and 8,192 bytes. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. Memory protection implemented by associating protection bit with each frame. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time. Paging Hardware With Tlb In Os.

From slideplayer.com

CS 3733 Operating Systems Topics Memory Management (SGG, Chapter 08 Paging Hardware With Tlb In Os But, page tables consume memory for lifetime of vas. Easy to address, no translation required. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. full course of operating system: Memory protection implemented by associating protection bit with each frame.. Paging Hardware With Tlb In Os.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Paging Hardware With Tlb In Os a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. It is a memory cache which is closer to the cpu and. Paging Hardware With Tlb In Os.

From operating-os-system.blogspot.com

OS การจัดการหน่วยความจำ (memory management) Paging Hardware With Tlb In Os paging hardware with tlb. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. full course of operating system: But, page tables consume memory for lifetime of vas. Memory protection implemented by associating protection bit with each frame. the translation lookaside buffer (tlb) is a vital component in modern. Paging Hardware With Tlb In Os.

From unchained112.github.io

Operating System Notes Paging Hardware With Tlb In Os It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. Memory protection implemented by associating protection bit with. Paging Hardware With Tlb In Os.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Paging Hardware With Tlb In Os Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. Size is power of 2, between 512 bytes and 8,192 bytes. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Memory. Paging Hardware With Tlb In Os.

From www.cs.uic.edu

Operating Systems Main Memory Paging Hardware With Tlb In Os Easy to address, no translation required. Divide physical memory into frames: paging hardware with tlb. But, page tables consume memory for lifetime of vas. the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. It is a memory cache which is closer to the cpu and. Paging Hardware With Tlb In Os.

From www.gatevidyalay.com

Translation Lookaside Buffer TLB Paging Gate Vidyalay Paging Hardware With Tlb In Os full course of operating system: a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Divide physical memory into frames: the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory. Paging Hardware With Tlb In Os.

From unstop.com

Understanding Paging In Operating System // Unstop (formerly Paging Hardware With Tlb In Os Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. Divide physical memory into frames: But, page tables consume memory for lifetime of vas. full course of operating. Paging Hardware With Tlb In Os.

From slideplayer.com

CSE 451 Operating Systems Autumn 2003 Lecture 10 Paging & TLBs ppt Paging Hardware With Tlb In Os the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. Size is power of 2, between 512 bytes and 8,192 bytes. paging hardware with tlb. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time. Paging Hardware With Tlb In Os.

From www.slideserve.com

PPT Paging Example PowerPoint Presentation, free download ID4740759 Paging Hardware With Tlb In Os It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. But,. Paging Hardware With Tlb In Os.

From celery1124.github.io

Large Page and Large TLB Entries Mian's Blog Architecture and system Paging Hardware With Tlb In Os Easy to address, no translation required. paging hardware with tlb. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. But, page tables consume memory for lifetime of vas. a translation look aside buffer can be defined as a. Paging Hardware With Tlb In Os.

From jhi93.github.io

Memory Management2 HAEIN Paging Hardware With Tlb In Os Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. Divide physical memory into frames: Easy to address, no translation required. Size is power of 2, between 512 bytes and 8,192 bytes. But, page tables consume memory for lifetime of vas. Memory protection implemented by associating protection bit with each frame. . Paging Hardware With Tlb In Os.

From www.scaler.com

Translation Lookaside Buffer (TLB) in OS Scaler Topics Paging Hardware With Tlb In Os Divide physical memory into frames: Size is power of 2, between 512 bytes and 8,192 bytes. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. paging hardware with tlb. It is a memory cache which is closer to. Paging Hardware With Tlb In Os.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Paging Hardware With Tlb In Os paging hardware with tlb. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. full course of operating system: the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory. Paging Hardware With Tlb In Os.

From slideplayer.com

Chapter 9 Memory Management ppt download Paging Hardware With Tlb In Os Memory protection implemented by associating protection bit with each frame. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that. Paging Hardware With Tlb In Os.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Paging Hardware With Tlb In Os paging hardware with tlb. Size is power of 2, between 512 bytes and 8,192 bytes. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Divide physical memory into frames: Memory protection implemented by associating protection bit with each. Paging Hardware With Tlb In Os.

From data-flair.training

Paging in Operating System DataFlair Paging Hardware With Tlb In Os paging hardware with tlb. full course of operating system: But, page tables consume memory for lifetime of vas. Memory protection implemented by associating protection bit with each frame. Size is power of 2, between 512 bytes and 8,192 bytes. It is a memory cache which is closer to the cpu and the time taken by cpu to access. Paging Hardware With Tlb In Os.

From www.slideshare.net

Os Swapping, Paging, Segmentation and Virtual Memory Paging Hardware With Tlb In Os Size is power of 2, between 512 bytes and 8,192 bytes. Divide physical memory into frames: a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. paging hardware with tlb. But, page tables consume memory for lifetime of vas.. Paging Hardware With Tlb In Os.

From www.slideserve.com

PPT Memory management PowerPoint Presentation, free download ID6165500 Paging Hardware With Tlb In Os the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. paging hardware with tlb. Easy to address, no translation required. Divide physical memory into frames: Memory protection implemented by associating protection bit with each frame. Faster translations (tlbs) using paging as the core mechanism to support. Paging Hardware With Tlb In Os.

From www.scaler.com

Paging in OS Scaler Topics Paging Hardware With Tlb In Os Size is power of 2, between 512 bytes and 8,192 bytes. paging hardware with tlb. Memory protection implemented by associating protection bit with each frame. full course of operating system: a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again. Paging Hardware With Tlb In Os.

From www.youtube.com

CST 206 MOD 4 PART 13 Paging Hardware with TLB YouTube Paging Hardware With Tlb In Os But, page tables consume memory for lifetime of vas. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is. Paging Hardware With Tlb In Os.

From www.slideserve.com

PPT ECE3055 Computer Architecture and Operating Systems Lecture 9 Paging Hardware With Tlb In Os Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. Easy to address, no translation required. Divide physical memory into frames: Size is power of 2, between 512 bytes and 8,192 bytes. Memory protection implemented by associating protection bit with each frame. the translation lookaside buffer (tlb) is a vital component. Paging Hardware With Tlb In Os.

From www.youtube.com

L43 Paging with Translation LookAside Buffer(TLB) Architecture Paging Hardware With Tlb In Os the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. Size is power of 2, between 512 bytes and 8,192 bytes. paging hardware with tlb. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. But, page tables. Paging Hardware With Tlb In Os.

From www.slideshare.net

Implementation of page table Paging Hardware With Tlb In Os paging hardware with tlb. Memory protection implemented by associating protection bit with each frame. Divide physical memory into frames: a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Size is power of 2, between 512 bytes and 8,192. Paging Hardware With Tlb In Os.

From dxopkszqx.blob.core.windows.net

Paging Hardware Support In Os at Ramona Crane blog Paging Hardware With Tlb In Os It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. But, page tables consume memory for lifetime of vas. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. Size is power of. Paging Hardware With Tlb In Os.

From slidetodoc.com

Page Table Implementation Implementation of Page Table Page Paging Hardware With Tlb In Os But, page tables consume memory for lifetime of vas. full course of operating system: It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. Size is power of 2, between 512 bytes and 8,192 bytes. Faster translations (tlbs) using paging. Paging Hardware With Tlb In Os.

From cs4118.github.io

Translation Lookaside Buffer (TLB) COMS W4118 Operating Systems I Paging Hardware With Tlb In Os the translation lookaside buffer (tlb) is a vital component in modern operating systems, serving as a cache memory that accelerates the translation. Faster translations (tlbs) using paging as the core mechanism to support virtual memory can lead to high performance. full course of operating system: Easy to address, no translation required. Memory protection implemented by associating protection bit. Paging Hardware With Tlb In Os.

From dxopkszqx.blob.core.windows.net

Paging Hardware Support In Os at Ramona Crane blog Paging Hardware With Tlb In Os Memory protection implemented by associating protection bit with each frame. Size is power of 2, between 512 bytes and 8,192 bytes. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. full course of operating system: Divide physical memory into. Paging Hardware With Tlb In Os.

From www.scaler.com

Translation Lookaside Buffer (TLB) in OS Scaler Topics Paging Hardware With Tlb In Os Size is power of 2, between 512 bytes and 8,192 bytes. Memory protection implemented by associating protection bit with each frame. full course of operating system: It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. Divide physical memory into. Paging Hardware With Tlb In Os.