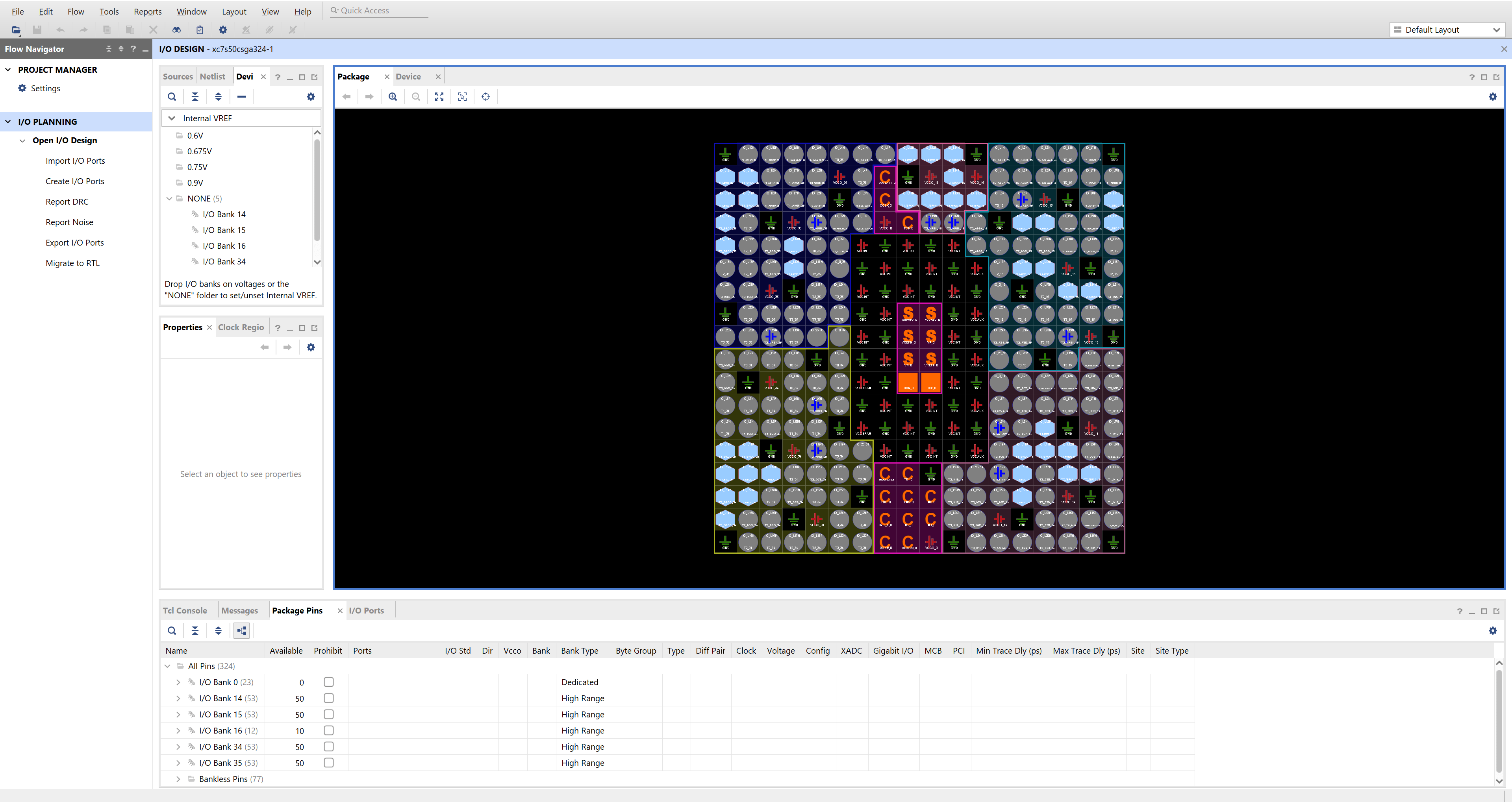

Xilinx Io Module . I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. I use io defined like this in the xdc file: Io module low level example. Contains an example on how to use the. You can refer to the below stated example applications for more details on how to use iomodule driver. Interrupts may be generated by the io module after this function is called. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. It is necessary for the caller to connect the interrupt.

from xilinx.github.io

You can refer to the below stated example applications for more details on how to use iomodule driver. Io module low level example. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. It is necessary for the caller to connect the interrupt. 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. Interrupts may be generated by the io module after this function is called. I use io defined like this in the xdc file: The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs).

Xilinx Design Constraints FPGA Design with Vivado

Xilinx Io Module Interrupts may be generated by the io module after this function is called. Contains an example on how to use the. I use io defined like this in the xdc file: I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. Interrupts may be generated by the io module after this function is called. You can refer to the below stated example applications for more details on how to use iomodule driver. It is necessary for the caller to connect the interrupt. 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. Io module low level example. Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports.

From www.hitechglobal.com

AMD (Xilinx) / Intel FPGA Boards & Systems, FMC Modules, Design Services, IP Cores and Manufacturing Xilinx Io Module I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. Interrupts may be generated by the io module after this function is called. Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. The io bus provides a generic mechanism to extend the io module functionality. Xilinx Io Module.

From www.micro-nova.com

Mercury 2 Xilinx Artix7 FPGA development board — MicroNova Xilinx Io Module I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). The io bus provides a generic mechanism to extend the io module functionality by. Xilinx Io Module.

From linuxgizmos.com

Xilinx unveils rugged additions to Versal ACAP Xilinx Io Module Interrupts may be generated by the io module after this function is called. It is necessary for the caller to connect the interrupt. I use io defined like this in the xdc file: Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. The io bus provides a generic mechanism to extend the io module functionality by providing a memory. Xilinx Io Module.

From in.rsdelivers.com

TE0711011002C Trenz Electronic GmbH Trenz Electronic GmbH TE0711011002C High IO Xilinx Xilinx Io Module Contains an example on how to use the. Io module low level example. Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped. Xilinx Io Module.

From www.mouser.in

Zynq7000 SoCs AMD / Xilinx Mouser Xilinx Io Module You can refer to the below stated example applications for more details on how to use iomodule driver. Io module low level example. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). It is necessary for the caller to connect the interrupt. Interrupts may be generated by. Xilinx Io Module.

From hackaday.io

Gallery Open Source HW Xilinx ZYNQ7000 System on Module Hackaday.io Xilinx Io Module Interrupts may be generated by the io module after this function is called. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). Contains an example on how. Xilinx Io Module.

From www.researchgate.net

Xilinx FPGA overview. The IOB connects the I/Opads to the ICN. These... Download Scientific Xilinx Io Module You can refer to the below stated example applications for more details on how to use iomodule driver. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). Contains an example on how to use the. The io bus provides a generic mechanism to extend the io module. Xilinx Io Module.

From hackaday.io

Gallery Open Source HW Xilinx ZYNQ7000 System on Module Hackaday.io Xilinx Io Module The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). I use io defined like this in the xdc file: It is necessary for the caller to connect the interrupt. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the. Xilinx Io Module.

From jp.rs-online.com

TE0711011002C Trenz Electronic GmbH プログラマブルロジック開発ツール CPLD, FPGA CPLD、FPGA 開発モジュール High IO Xilinx Io Module It is necessary for the caller to connect the interrupt. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). Interrupts may be generated by the io module after this function is called. You can refer to the below stated example applications for more details on how to. Xilinx Io Module.

From stackoverflow.com

logic XILINX ISE set I/O Marker as Clock Stack Overflow Xilinx Io Module I use io defined like this in the xdc file: The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. Contains an example on how to use the.. Xilinx Io Module.

From shop.trenz-electronic.de

High IO Industrial Artix 100 Module with speedgrade 2C and USB Trenz Electronic GmbH Online Xilinx Io Module I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. I use io defined like this in the xdc file: The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). It is necessary for. Xilinx Io Module.

From www.entegra.co.uk

Xilinx® Zynq® UltraScale+ MPSoC Module Entegra Xilinx Io Module You can refer to the below stated example applications for more details on how to use iomodule driver. Contains an example on how to use the. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. It is necessary for the caller to connect the interrupt. 22 rows decoupling the. Xilinx Io Module.

From hackaday.io

Gallery Open Source HW Xilinx ZYNQ7000 System on Module Hackaday.io Xilinx Io Module I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. You can refer to the below stated example applications for more details on how to use. Xilinx Io Module.

From shop.trenz-electronic.de

High IO Industrialgrade Xilinx Artix7 35T Module with speedgrade 2C and USB Trenz Electronic Xilinx Io Module I use io defined like this in the xdc file: Contains an example on how to use the. Io module low level example. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. Interrupts may be generated by the io module after this function is called. Set_property iostandard lvcmos33 [get_ports. Xilinx Io Module.

From hackaday.io

Gallery Open Source HW Xilinx ZYNQ7000 System on Module Hackaday.io Xilinx Io Module I use io defined like this in the xdc file: The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard. Xilinx Io Module.

From hackaday.io

Gallery Open Source HW Xilinx ZYNQ7000 System on Module Hackaday.io Xilinx Io Module You can refer to the below stated example applications for more details on how to use iomodule driver. 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. Interrupts may be generated by the io module after this function is called. Io module low level example. I use io defined like. Xilinx Io Module.

From www.researchgate.net

Xilinx FPGA overview. The IOB connects the I/Opads to the ICN. These... Download Scientific Xilinx Io Module 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. I use io defined like this in the xdc file: The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). I/o and clock planning is the process of defining. Xilinx Io Module.

From linuxgizmos.com

Xilinx launches UltraScale+ based SOM and 199 dev kit with AI extensions Xilinx Io Module It is necessary for the caller to connect the interrupt. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. Io module low level example. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). You can refer. Xilinx Io Module.

From www.raypcb.com

How To Make Your Product Stand Out With Xilinx Virtex5 FPGA Boards RAYPCB Xilinx Io Module I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. You can refer to the below stated example applications for more details on how to use iomodule driver. Interrupts may be generated by the io module after this function is called. Contains an example on how. Xilinx Io Module.

From shop.trenz-electronic.de

High IO Industrialgrade Xilinx Artix7 100T Module with speedgrade 2C and USB Trenz Xilinx Io Module The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the. Xilinx Io Module.

From www.cnx-software.com

Xilinx ZynqZ7015 FPGA + ARM based SystemonModules Include High Speed Transceivers Xilinx Io Module 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. Io module low level example. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. You can refer to the below stated example applications for more details. Xilinx Io Module.

From hackaday.io

Gallery Open Source HW Xilinx ZYNQ7000 System on Module Hackaday.io Xilinx Io Module Io module low level example. Interrupts may be generated by the io module after this function is called. It is necessary for the caller to connect the interrupt. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. You can refer to the below stated example applications for more details. Xilinx Io Module.

From redphoenixbrands.com

MYIR Launched NXP i.MX 8M Mini + Xilinx Artix7 based ARM+FPGA SoM RED PHOENIX BRANDS Xilinx Io Module Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. Contains an example on how to use the. Io module low level example. Interrupts may be generated by the io module after this function is called.. Xilinx Io Module.

From xilinx.github.io

Xilinx Design Constraints FPGA Design with Vivado Xilinx Io Module You can refer to the below stated example applications for more details on how to use iomodule driver. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. Io module low level example. The io bus provides a generic mechanism to extend the io module functionality. Xilinx Io Module.

From hackaday.io

Gallery Open Source HW Xilinx ZYNQ7000 System on Module Hackaday.io Xilinx Io Module I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. I use io defined like this in the xdc file: Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. The i/o module is a standalone version of the tightly coupled i/o module included in the. Xilinx Io Module.

From linuxgizmos.com

Xilinx unveils rugged additions to Versal ACAP Xilinx Io Module Io module low level example. 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. It is necessary for the caller to connect the interrupt. Interrupts may. Xilinx Io Module.

From www.aliexpress.com

Buy XILINX FPGA Spartan 7 XC7S50 Development Board Spartan7 PCB Core Board and Xilinx Io Module Io module low level example. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. The i/o module is a standalone version of the tightly coupled. Xilinx Io Module.

From content.speedgoat.com

IO335 Configurable FPGAbased I/O module with Xilinx Kintex 7 + I/O for Simulink Xilinx Io Module Io module low level example. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing carrier card reuse. Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. You can refer to the below. Xilinx Io Module.

From in.rsdelivers.com

TE0711011002C Trenz Electronic GmbH Trenz Electronic GmbH TE0711011002C High IO Xilinx Xilinx Io Module The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. It is necessary for the caller to connect the interrupt. You can refer to the below stated example applications for more details on how to use iomodule driver. I use io defined like this in the xdc file: Interrupts may. Xilinx Io Module.

From www.youtube.com

Mod06 Lec38 Xilinx Virtex Resource Mapping, IO Block YouTube Xilinx Io Module I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. The io bus provides a generic mechanism to extend the io module functionality by providing a memory mapped io area. You can refer to the below stated example applications for more details on how to use. Xilinx Io Module.

From militaryembedded.com

SiP devices unveiled based on AMDXilinx Zynq UltraScale+ MPSoC architecture Military Embedded Xilinx Io Module The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). It is necessary for the caller to connect the interrupt. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. Contains an example on. Xilinx Io Module.

From www.youtube.com

Xilinx Schematic Editor Connect IO Marker to bus of different length YouTube Xilinx Io Module The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. You can refer to the below stated example applications for more details on how. Xilinx Io Module.

From shop.trenz-electronic.de

High IO Industrial Artix 35 Module with speedgrade 2C and USB Trenz Electronic (EN)] Xilinx Io Module Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. It is necessary for the caller to connect the interrupt. 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module design while maximizing. Xilinx Io Module.

From www.xes-inc.com

XPedite2403 Xilinx Virtex7 FPGABased FiberOptic I/O XMC Module Xilinx Io Module Set_property iostandard lvcmos33 [get_ports {exp_p_io [*]}] set_property iostandard lvcmos33 [get_ports. You can refer to the below stated example applications for more details on how to use iomodule driver. The i/o module is a standalone version of the tightly coupled i/o module included in the logicore microblaze™ micro controller system (mcs). Interrupts may be generated by the io module after this. Xilinx Io Module.

From shop.trenz-electronic.de

High IO Industrialgrade Xilinx Artix7 100T Module with speedgrade 2C and USB Trenz Xilinx Io Module I/o and clock planning is the process of defining and analyzing the connectivity between the fpga/acap and the printed circuit board (pcb) and assigning. Interrupts may be generated by the io module after this function is called. I use io defined like this in the xdc file: 22 rows decoupling the i/o interfaces from the fpga simplifies i/o interface module. Xilinx Io Module.