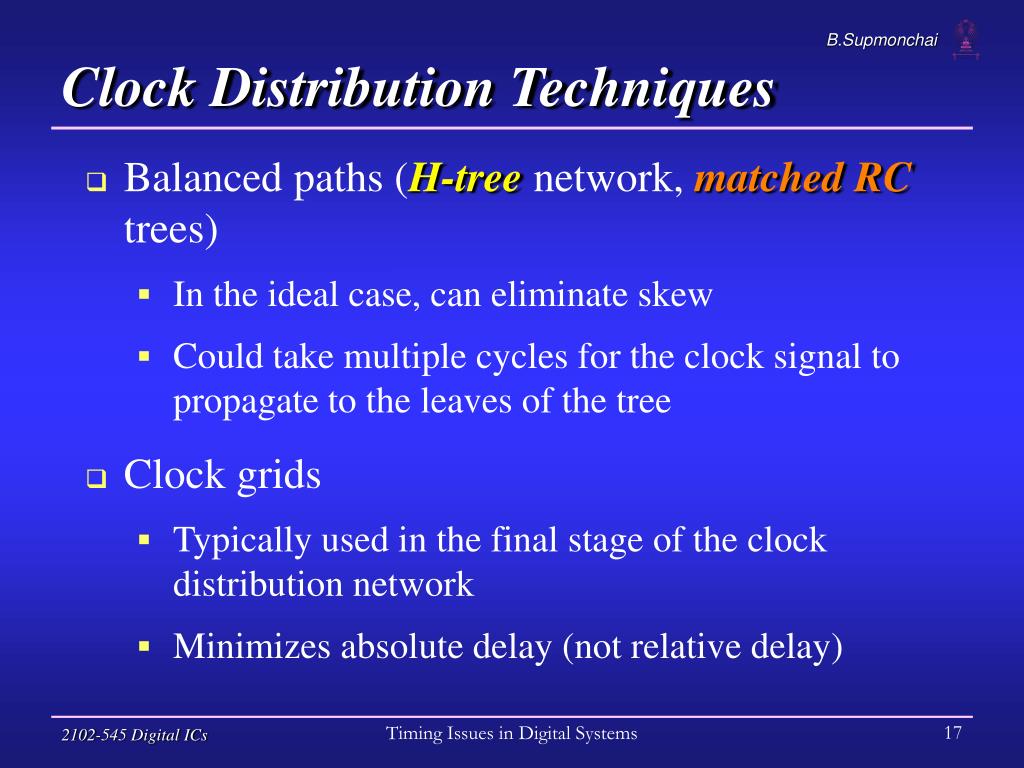

Types Of Clock Distribution Techniques . Timing loop closed individually around each data line. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Most sources of skew compensated. Buffer chain, current mode logic (cml) clocking, capacitively. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. In this paper, we studied these different methods used for the clock distribution:

from www.slideserve.com

In this paper, we studied these different methods used for the clock distribution: Most sources of skew compensated. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Buffer chain, current mode logic (cml) clocking, capacitively. Timing loop closed individually around each data line. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and.

PPT Chapter 11 Timing Issues in Digital Systems PowerPoint

Types Of Clock Distribution Techniques In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Buffer chain, current mode logic (cml) clocking, capacitively. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. In this paper, we studied these different methods used for the clock distribution: Most sources of skew compensated. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Timing loop closed individually around each data line.

From www.slideserve.com

PPT Reconfigurable Clock Distribution Circuitry PowerPoint Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Buffer chain, current mode logic (cml) clocking, capacitively. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we.. Types Of Clock Distribution Techniques.

From www.slideshare.net

Clock Distribution Types Of Clock Distribution Techniques Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Most sources of skew compensated. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Timing loop closed individually around each data line. Buffer chain, current mode logic (cml) clocking, capacitively. Various. Types Of Clock Distribution Techniques.

From www.youtube.com

Type of Clock Clock and Watch Names YouTube Types Of Clock Distribution Techniques Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. In this paper, we studied these different methods used for the clock distribution: Most sources of skew compensated. Buffer chain, current mode logic (cml) clocking, capacitively. Understanding these theories and fundamentals is essential for designing. Types Of Clock Distribution Techniques.

From www.researchgate.net

Global clock distribution network, consisting of 16 resonant clock Types Of Clock Distribution Techniques Timing loop closed individually around each data line. Buffer chain, current mode logic (cml) clocking, capacitively. Most sources of skew compensated. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Various factors and design choices affect clock distribution, including the type of materials used for. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Timing loop closed individually around each data line. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Using. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Buffer chain, current mode logic (cml) clocking, capacitively. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. In this paper, we studied these different methods used for the. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT A Survey of Clock Distribution Techniques Including Optical and Types Of Clock Distribution Techniques Most sources of skew compensated. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Buffer chain, current mode logic (cml) clocking, capacitively. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at. Types Of Clock Distribution Techniques.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Types Of Clock Distribution Techniques Most sources of skew compensated. Timing loop closed individually around each data line. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock and Power PowerPoint Presentation, free download ID417576 Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Timing loop closed individually around each data line. In this paper, we studied these different methods used for the. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Design PowerPoint Presentation, free download ID2403511 Types Of Clock Distribution Techniques Timing loop closed individually around each data line. Most sources of skew compensated. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Buffer chain, current mode logic (cml) clocking, capacitively. In this paper, we studied these different methods used for the clock distribution: In large digital systems, clock tree synthesis is employed to optimize the. Types Of Clock Distribution Techniques.

From www.scribd.com

10 Clock Distribution Topologies Types Of Clock Distribution Techniques Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Most sources of skew compensated. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. In this paper, we studied these different methods used for the clock distribution: Timing. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Reconfigurable Clock Distribution Circuitry PowerPoint Types Of Clock Distribution Techniques In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock and Power PowerPoint Presentation, free download ID417576 Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Most sources of skew compensated. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Using the techniques we discussed in previous lectures, we can set up a highly. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Options and Sleep Modes PowerPoint Presentation, free Types Of Clock Distribution Techniques Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Buffer chain, current mode logic (cml) clocking, capacitively. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and.. Types Of Clock Distribution Techniques.

From siliconvlsi.com

ClockDistribution Techniques Siliconvlsi Types Of Clock Distribution Techniques Most sources of skew compensated. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. In this paper, we studied these different methods used for the clock distribution: Timing loop closed individually around each data line. Various factors and design choices affect clock distribution, including. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Reconfigurable Clock Distribution Circuitry PowerPoint Types Of Clock Distribution Techniques In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Timing loop closed individually around each data line. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Using the techniques we discussed in previous lectures, we can set up a highly. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Types Of Clock Distribution Techniques Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. In this paper, we studied these different methods used for the clock distribution: Most sources of skew compensated. Timing loop closed. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clocking & Timing PowerPoint Presentation, free download ID4060103 Types Of Clock Distribution Techniques Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Timing loop closed individually around each data line. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and.. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Types Of Clock Distribution Techniques Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Timing loop closed individually around each data line. Most sources of skew compensated. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT A Survey of Clock Distribution Techniques Including Optical and Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Buffer chain, current mode logic (cml) clocking, capacitively. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. In this paper, we studied these different methods used for the. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT CENG3480_B1 Digital System Clock PowerPoint Presentation, free Types Of Clock Distribution Techniques In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Buffer chain, current mode logic (cml) clocking, capacitively. Timing loop closed individually around each data line. In this paper, we studied these different methods used for the clock distribution: Most sources of skew compensated. Using the. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock and Synchronization PowerPoint Presentation, free download Types Of Clock Distribution Techniques In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Timing loop closed individually around each data line. Buffer. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Types Of Clock Distribution Techniques In this paper, we studied these different methods used for the clock distribution: In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Timing loop closed individually around each data line. Using the techniques we discussed in previous lectures, we can set up a highly robust. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Types Of Clock Distribution Techniques In this paper, we studied these different methods used for the clock distribution: Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. In large digital systems, clock tree. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID Types Of Clock Distribution Techniques In this paper, we studied these different methods used for the clock distribution: Buffer chain, current mode logic (cml) clocking, capacitively. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems.. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Types Of Clock Distribution Techniques Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Timing loop closed individually around each data line. In this paper, we studied these different methods used for the clock distribution: Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we.. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Buffer chain, current mode logic (cml) clocking, capacitively.. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Chapter 11 Timing Issues in Digital Systems PowerPoint Types Of Clock Distribution Techniques Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Timing loop closed individually around each data line. Most sources of skew compensated. Buffer chain, current mode logic (cml) clocking, capacitively. Using. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Types Of Clock Distribution Techniques In this paper, we studied these different methods used for the clock distribution: Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Buffer chain, current mode logic (cml) clocking, capacitively. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we.. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Types Of Clock Distribution Techniques Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. In large digital systems, clock tree synthesis is. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Types Of Clock Distribution Techniques Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Buffer chain, current mode logic (cml) clocking, capacitively. In this paper, we studied these different methods used for the clock distribution:. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT A Survey of Clock Distribution Techniques Including Optical and Types Of Clock Distribution Techniques In large digital systems, clock tree synthesis is employed to optimize the distribution of the clock signal, ensuring uniform arrival times at different components. Understanding these theories and fundamentals is essential for designing robust and reliable digital systems. Timing loop closed individually around each data line. Various factors and design choices affect clock distribution, including the type of materials used. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Most sources of skew compensated. In this paper, we studied these different methods used for the clock distribution: Timing loop closed individually around each data line. Understanding these theories and fundamentals is essential. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Types Of Clock Distribution Techniques Various factors and design choices affect clock distribution, including the type of materials used for wires, the network’s topology and hierarchy, wire and buffer sizing, rise and. Buffer chain, current mode logic (cml) clocking, capacitively. In this paper, we studied these different methods used for the clock distribution: Timing loop closed individually around each data line. Understanding these theories and. Types Of Clock Distribution Techniques.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID518938 Types Of Clock Distribution Techniques Timing loop closed individually around each data line. Using the techniques we discussed in previous lectures, we can set up a highly robust clock source serving as root of the tree, and we. Most sources of skew compensated. In this paper, we studied these different methods used for the clock distribution: Various factors and design choices affect clock distribution, including. Types Of Clock Distribution Techniques.