Module Vs Class Systemverilog . It is intended to be a reusable component that can be connected to form a larger. Class is composed of set of members that describe how an instance of class or object is constructed and how it. For a more thorough reference, prof. Classes are used to model data, whose values can be created as part of the constrained random methodology. Hauck recommends vahid and lysecky’s verilog for digital design. But struct variables like array variables directly. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. Modules are the basic building blocks of systemverilog. We begin by looking at the way we structure a systemverilog design using the module keyword. A class variable holds just a reference and a new call is required to create a class object. The basic building block of verilog is a. This includes a discussion of.

from www.youtube.com

But struct variables like array variables directly. Class is composed of set of members that describe how an instance of class or object is constructed and how it. This includes a discussion of. Hauck recommends vahid and lysecky’s verilog for digital design. For a more thorough reference, prof. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. Classes are used to model data, whose values can be created as part of the constrained random methodology. A class variable holds just a reference and a new call is required to create a class object. We begin by looking at the way we structure a systemverilog design using the module keyword. Modules are the basic building blocks of systemverilog.

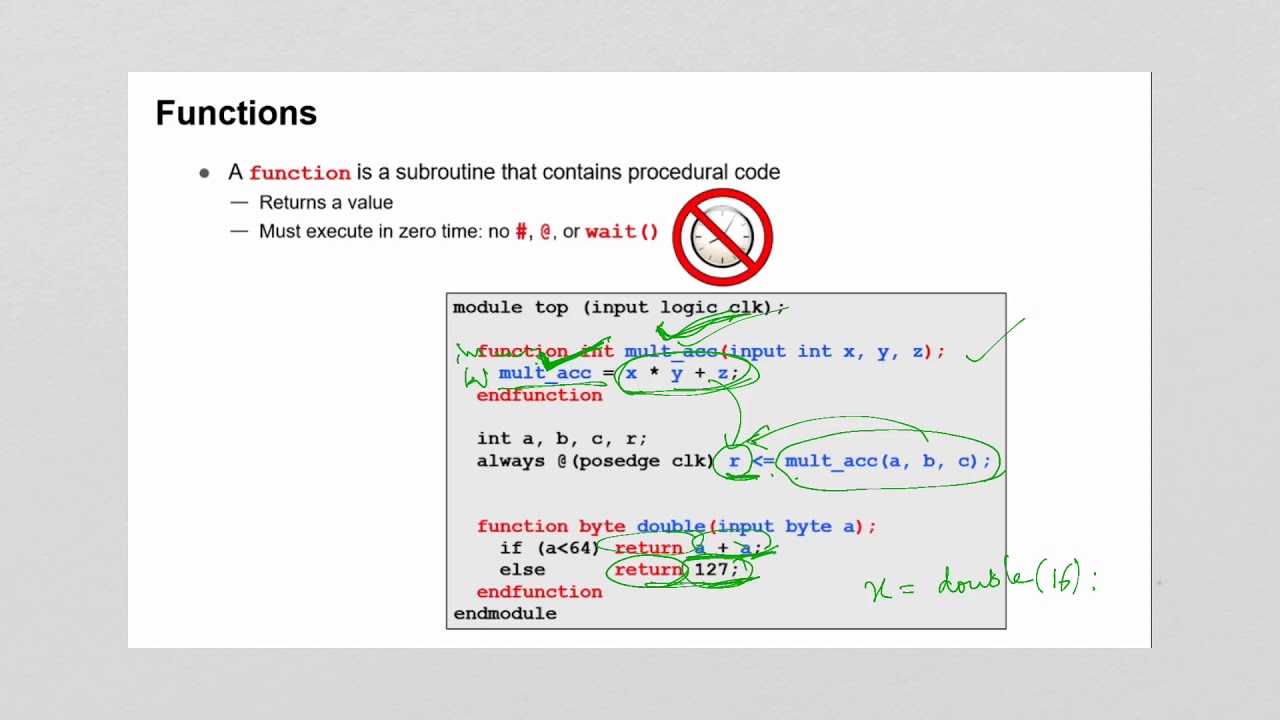

Functions and Tasks in SystemVerilog with conceptual examples YouTube

Module Vs Class Systemverilog The basic building block of verilog is a. It is intended to be a reusable component that can be connected to form a larger. But struct variables like array variables directly. We begin by looking at the way we structure a systemverilog design using the module keyword. Classes are used to model data, whose values can be created as part of the constrained random methodology. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. Hauck recommends vahid and lysecky’s verilog for digital design. This includes a discussion of. For a more thorough reference, prof. A class variable holds just a reference and a new call is required to create a class object. Class is composed of set of members that describe how an instance of class or object is constructed and how it. Modules are the basic building blocks of systemverilog. The basic building block of verilog is a.

From www.elecfans.com

SystemVerilog中的类的赋值电子发烧友网 Module Vs Class Systemverilog A class variable holds just a reference and a new call is required to create a class object. Modules are the basic building blocks of systemverilog. This includes a discussion of. The basic building block of verilog is a. Hauck recommends vahid and lysecky’s verilog for digital design. It is intended to be a reusable component that can be connected. Module Vs Class Systemverilog.

From verificationguide.com

SystemVerilog Class Assignment Verification Guide Module Vs Class Systemverilog Hauck recommends vahid and lysecky’s verilog for digital design. A class variable holds just a reference and a new call is required to create a class object. But struct variables like array variables directly. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that. Module Vs Class Systemverilog.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 12c Class Randomization YouTube Module Vs Class Systemverilog A class variable holds just a reference and a new call is required to create a class object. Hauck recommends vahid and lysecky’s verilog for digital design. Class is composed of set of members that describe how an instance of class or object is constructed and how it. You need to declare this class in a package , and import. Module Vs Class Systemverilog.

From www.congress-intercultural.eu

Verilog Vs SystemVerilog Top 10 Differences You Should Know, 56 OFF Module Vs Class Systemverilog This includes a discussion of. Classes are used to model data, whose values can be created as part of the constrained random methodology. We begin by looking at the way we structure a systemverilog design using the module keyword. For a more thorough reference, prof. A class variable holds just a reference and a new call is required to create. Module Vs Class Systemverilog.

From thecontentauthority.com

Module vs Class When To Use Each One In Writing? Module Vs Class Systemverilog Classes are used to model data, whose values can be created as part of the constrained random methodology. We begin by looking at the way we structure a systemverilog design using the module keyword. For a more thorough reference, prof. This includes a discussion of. Hauck recommends vahid and lysecky’s verilog for digital design. But struct variables like array variables. Module Vs Class Systemverilog.

From verificationguide.com

SystemVerilog Shallow Copy Verification Guide Module Vs Class Systemverilog This includes a discussion of. But struct variables like array variables directly. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. Class is composed of set of members that describe how an instance of class or object is constructed and how it.. Module Vs Class Systemverilog.

From www.youtube.com

Course Systemverilog Verification 3 L10.1 Class Based TB Module Vs Class Systemverilog You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. It is intended to be a reusable component that can be connected to form a larger. We begin by looking at the way we structure a systemverilog design using the module keyword. Hauck. Module Vs Class Systemverilog.

From zhuanlan.zhihu.com

SystemVerilog中的类的继承 知乎 Module Vs Class Systemverilog Hauck recommends vahid and lysecky’s verilog for digital design. But struct variables like array variables directly. Modules are the basic building blocks of systemverilog. For a more thorough reference, prof. It is intended to be a reusable component that can be connected to form a larger. A class variable holds just a reference and a new call is required to. Module Vs Class Systemverilog.

From www.youtube.com

SystemVerilog Classes 1 Basics YouTube Module Vs Class Systemverilog For a more thorough reference, prof. We begin by looking at the way we structure a systemverilog design using the module keyword. Classes are used to model data, whose values can be created as part of the constrained random methodology. Class is composed of set of members that describe how an instance of class or object is constructed and how. Module Vs Class Systemverilog.

From www.youtube.com

Functions and Tasks in SystemVerilog with conceptual examples YouTube Module Vs Class Systemverilog A class variable holds just a reference and a new call is required to create a class object. Classes are used to model data, whose values can be created as part of the constrained random methodology. The basic building block of verilog is a. Class is composed of set of members that describe how an instance of class or object. Module Vs Class Systemverilog.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 05 String YouTube Module Vs Class Systemverilog You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. Class is composed of set of members that describe how an instance of class or object is constructed and how it. Modules are the basic building blocks of systemverilog. For a more thorough. Module Vs Class Systemverilog.

From www.numerade.com

SOLVED Consider the following two SystemVerilog modules. 1) Do they Module Vs Class Systemverilog This includes a discussion of. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. Classes are used to model data, whose values can be created as part of the constrained random methodology. For a more thorough reference, prof. Class is composed of. Module Vs Class Systemverilog.

From www.edn.com

Inheritance and polymorphism of SystemVerilog OOP for UVM verification Module Vs Class Systemverilog It is intended to be a reusable component that can be connected to form a larger. But struct variables like array variables directly. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. We begin by looking at the way we structure a. Module Vs Class Systemverilog.

From www.maven-silicon.com

SystemVerilog Testbench/Verification Environment Architecture Maven Module Vs Class Systemverilog Classes are used to model data, whose values can be created as part of the constrained random methodology. This includes a discussion of. Hauck recommends vahid and lysecky’s verilog for digital design. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. Modules. Module Vs Class Systemverilog.

From www.youtube.com

Systemverilog Object Oriented Programming Example of Converting Module Module Vs Class Systemverilog Hauck recommends vahid and lysecky’s verilog for digital design. A class variable holds just a reference and a new call is required to create a class object. It is intended to be a reusable component that can be connected to form a larger. Modules are the basic building blocks of systemverilog. We begin by looking at the way we structure. Module Vs Class Systemverilog.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 09 Function and Task YouTube Module Vs Class Systemverilog For a more thorough reference, prof. We begin by looking at the way we structure a systemverilog design using the module keyword. Classes are used to model data, whose values can be created as part of the constrained random methodology. But struct variables like array variables directly. You need to declare this class in a package , and import the. Module Vs Class Systemverilog.

From pediaa.com

What is the Difference Between Verilog and SystemVerilog Module Vs Class Systemverilog We begin by looking at the way we structure a systemverilog design using the module keyword. For a more thorough reference, prof. It is intended to be a reusable component that can be connected to form a larger. Class is composed of set of members that describe how an instance of class or object is constructed and how it. Hauck. Module Vs Class Systemverilog.

From slideplayer.com

Chapter 4 Digital Design and Computer Architecture, 2nd Edition ppt Module Vs Class Systemverilog A class variable holds just a reference and a new call is required to create a class object. Classes are used to model data, whose values can be created as part of the constrained random methodology. But struct variables like array variables directly. We begin by looking at the way we structure a systemverilog design using the module keyword. For. Module Vs Class Systemverilog.

From www.youtube.com

Course Systemverilog Verification 2 L5.1 Basics of Systemverilog Module Vs Class Systemverilog Modules are the basic building blocks of systemverilog. For a more thorough reference, prof. It is intended to be a reusable component that can be connected to form a larger. This includes a discussion of. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of. Module Vs Class Systemverilog.

From slideplayer.com

Lecture 3 Timing & Sequential Circuits ppt download Module Vs Class Systemverilog Classes are used to model data, whose values can be created as part of the constrained random methodology. Modules are the basic building blocks of systemverilog. For a more thorough reference, prof. Class is composed of set of members that describe how an instance of class or object is constructed and how it. It is intended to be a reusable. Module Vs Class Systemverilog.

From circuitdiagrams.in

Verilog vs. SystemVerilog What are the Differences Between Them? Module Vs Class Systemverilog This includes a discussion of. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. The basic building block of verilog is a. But struct variables like array variables directly. We begin by looking at the way we structure a systemverilog design using. Module Vs Class Systemverilog.

From zhuanlan.zhihu.com

SystemVerilog 鸟瞰UVM通用验证方法学 知乎 Module Vs Class Systemverilog Classes are used to model data, whose values can be created as part of the constrained random methodology. This includes a discussion of. We begin by looking at the way we structure a systemverilog design using the module keyword. For a more thorough reference, prof. But struct variables like array variables directly. Hauck recommends vahid and lysecky’s verilog for digital. Module Vs Class Systemverilog.

From www.edaphic.studio

Beta9 SystemVerilog interface classes added — Edaphic.Studio Module Vs Class Systemverilog This includes a discussion of. Class is composed of set of members that describe how an instance of class or object is constructed and how it. The basic building block of verilog is a. We begin by looking at the way we structure a systemverilog design using the module keyword. Hauck recommends vahid and lysecky’s verilog for digital design. It. Module Vs Class Systemverilog.

From mavink.com

Systemverilog Cheat Sheet Module Vs Class Systemverilog We begin by looking at the way we structure a systemverilog design using the module keyword. The basic building block of verilog is a. Hauck recommends vahid and lysecky’s verilog for digital design. Classes are used to model data, whose values can be created as part of the constrained random methodology. For a more thorough reference, prof. A class variable. Module Vs Class Systemverilog.

From www.slideserve.com

PPT SystemVerilog basics PowerPoint Presentation, free download ID Module Vs Class Systemverilog A class variable holds just a reference and a new call is required to create a class object. Modules are the basic building blocks of systemverilog. We begin by looking at the way we structure a systemverilog design using the module keyword. You need to declare this class in a package , and import the package in every module you. Module Vs Class Systemverilog.

From stackoverflow.com

class What is the Taxonomy of Python? Stack Overflow Module Vs Class Systemverilog We begin by looking at the way we structure a systemverilog design using the module keyword. It is intended to be a reusable component that can be connected to form a larger. Classes are used to model data, whose values can be created as part of the constrained random methodology. For a more thorough reference, prof. You need to declare. Module Vs Class Systemverilog.

From www.youtube.com

SystemVerilog Object Oriented Programming Introduction to Classes Module Vs Class Systemverilog We begin by looking at the way we structure a systemverilog design using the module keyword. Classes are used to model data, whose values can be created as part of the constrained random methodology. For a more thorough reference, prof. It is intended to be a reusable component that can be connected to form a larger. Modules are the basic. Module Vs Class Systemverilog.

From www.youtube.com

Course Systemverilog Verification 1 L2.1 Design & TestBench Module Vs Class Systemverilog You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. Classes are used to model data, whose values can be created as part of the constrained random methodology. The basic building block of verilog is a. Modules are the basic building blocks of. Module Vs Class Systemverilog.

From www.youtube.com

SystemVerilog Class Task Function Methods Property YouTube Module Vs Class Systemverilog Modules are the basic building blocks of systemverilog. It is intended to be a reusable component that can be connected to form a larger. You need to declare this class in a package , and import the package in every module you plan to declare a class variable of that class. For a more thorough reference, prof. A class variable. Module Vs Class Systemverilog.

From www.youtube.com

Course Systemverilog Verification 2 L5.2 Interfaces and Modports Module Vs Class Systemverilog Class is composed of set of members that describe how an instance of class or object is constructed and how it. But struct variables like array variables directly. Classes are used to model data, whose values can be created as part of the constrained random methodology. You need to declare this class in a package , and import the package. Module Vs Class Systemverilog.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 18 Cross Modules Reference YouTube Module Vs Class Systemverilog For a more thorough reference, prof. The basic building block of verilog is a. We begin by looking at the way we structure a systemverilog design using the module keyword. Class is composed of set of members that describe how an instance of class or object is constructed and how it. You need to declare this class in a package. Module Vs Class Systemverilog.

From verificationguide.com

SystemVerilog Class Constructors Verification Guide Module Vs Class Systemverilog Class is composed of set of members that describe how an instance of class or object is constructed and how it. Modules are the basic building blocks of systemverilog. For a more thorough reference, prof. A class variable holds just a reference and a new call is required to create a class object. Classes are used to model data, whose. Module Vs Class Systemverilog.

From www.youtube.com

Verilog vs SystemVerilog 2 Difference between Verilog and Module Vs Class Systemverilog For a more thorough reference, prof. The basic building block of verilog is a. Classes are used to model data, whose values can be created as part of the constrained random methodology. But struct variables like array variables directly. You need to declare this class in a package , and import the package in every module you plan to declare. Module Vs Class Systemverilog.

From www.eeworldonline.com

How to structure SystemVerilog for reuse as Portable Stimulus Module Vs Class Systemverilog For a more thorough reference, prof. The basic building block of verilog is a. We begin by looking at the way we structure a systemverilog design using the module keyword. Hauck recommends vahid and lysecky’s verilog for digital design. But struct variables like array variables directly. It is intended to be a reusable component that can be connected to form. Module Vs Class Systemverilog.

From medium.com

System Verilog Tutorial for Beginners by Maven Silicon Medium Module Vs Class Systemverilog But struct variables like array variables directly. A class variable holds just a reference and a new call is required to create a class object. Classes are used to model data, whose values can be created as part of the constrained random methodology. We begin by looking at the way we structure a systemverilog design using the module keyword. The. Module Vs Class Systemverilog.