Clock Enable . Normally you would use an edge sensitive flop to hold latch_update_en to prevent. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Rising edge for active low latches. For an active high latch, the gating signal should toggle on the falling edge of the clock. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Features • ideal for addressable register applications • clock enable for address and data. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems.

from www.comtechsolutions.com

Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. For an active high latch, the gating signal should toggle on the falling edge of the clock. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Rising edge for active low latches. Features • ideal for addressable register applications • clock enable for address and data.

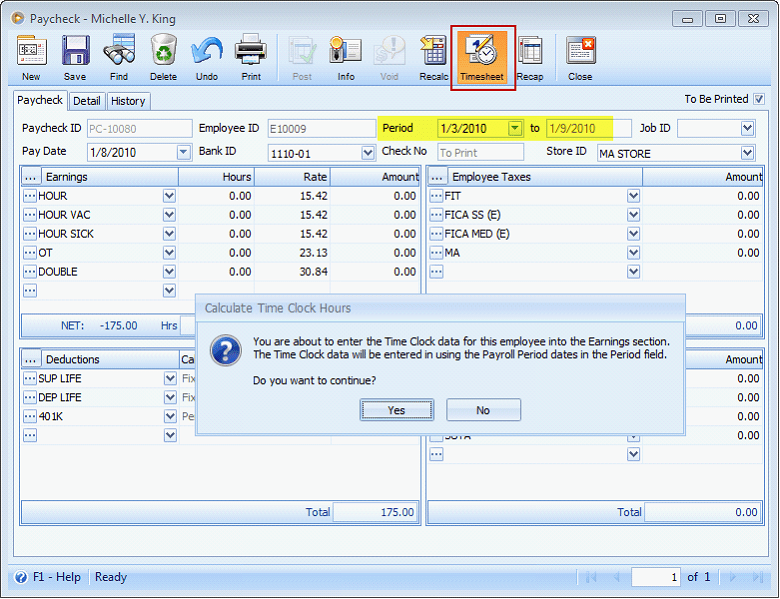

Payroll > Time Clock > Enable Time Clock Hours Calculation

Clock Enable The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Rising edge for active low latches. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. For an active high latch, the gating signal should toggle on the falling edge of the clock. Features • ideal for addressable register applications • clock enable for address and data.

From www.youtube.com

Apple Watch Enable/Disable 24 Hour Clock (Series 6,5,4,3,SE) YouTube Clock Enable The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Rising edge for active low latches. Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Features • ideal for addressable register applications • clock enable for address and data. Hi, i have a state. Clock Enable.

From www.askdavetaylor.com

Add Additional World Clocks to your Windows 11 Display from Ask Dave Taylor Clock Enable Features • ideal for addressable register applications • clock enable for address and data. For an active high latch, the gating signal should toggle on the falling edge of the clock. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. The obvious answer is to pass. Clock Enable.

From www.slideserve.com

PPT Clock domains & divider Clock & reset distribution PowerPoint Presentation ID2084973 Clock Enable Normally you would use an edge sensitive flop to hold latch_update_en to prevent. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those.. Clock Enable.

From techpp.com

How to Enable and Use StandBy Mode on iPhone [iOS 17] TechPP Clock Enable Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. Rising edge for active low latches. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Normally you. Clock Enable.

From www.researchgate.net

(PDF) Exploiting useful skew in gated low voltage clock trees Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. For an active high latch, the gating signal should toggle on the falling edge of the clock. Rising edge for active low latches. The obvious answer is to pass the clock. Clock Enable.

From www.youtube.com

Enable Dual Clocks on any iPhone Lockscreen [ iOS 16 ] Dual Clock Now for iPhone's🔥🔥 YouTube Clock Enable For an active high latch, the gating signal should toggle on the falling edge of the clock. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Learn how to. Clock Enable.

From help.exatouch.com

Manage the Time Clock Exatouch Knowledge Base Clock Enable Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Rising edge for active low latches. For an active high latch, the gating signal should toggle on the falling edge of the clock. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. Hi,. Clock Enable.

From www.msftnext.com

How to enable seconds for taskbar clock in Windows 11 Clock Enable Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Rising edge for active low latches. Features •. Clock Enable.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Enable Normally you would use an edge sensitive flop to hold latch_update_en to prevent. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. For an active high latch, the gating signal should toggle on the falling edge of the clock. Rising edge for active low latches. When the. Clock Enable.

From www.worldatlas.com

What is the Difference Between the 12 Hour and the 24 Hour Clock? WorldAtlas Clock Enable The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. For an active high latch, the gating signal should toggle on the falling edge of the clock. Rising edge for active low latches. Learn how to create a clock enable signal instead of another clock domain to avoid. Clock Enable.

From www.idownloadblog.com

iOS 7 the ultimate Clock app guide Clock Enable When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. For an active high latch, the gating signal should toggle on the falling edge of the clock. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. The obvious. Clock Enable.

From www.slideserve.com

PPT Clock domains & divider Clock & reset distribution PowerPoint Presentation ID2084973 Clock Enable Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. The obvious answer is to pass the clock and enable through an and gate, but that breaks the. Clock Enable.

From klamtnsmb.blob.core.windows.net

What Is Clock Enable at Hanna Nunley blog Clock Enable Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. For an active high latch, the gating signal should toggle on the falling edge of the clock. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Normally you. Clock Enable.

From slideplayer.com

I2C Protocol and RTC Interfacing ppt download Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Rising edge for active low latches. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Normally you would use an edge sensitive. Clock Enable.

From www.anuko.com

How to Enable Taskbar Clock Clock Enable For an active high latch, the gating signal should toggle on the falling edge of the clock. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Rising edge for active low latches. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't. Clock Enable.

From www.youtube.com

Enable Seconds In Windows 11 Taskbar Clock YouTube Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Features • ideal for addressable register applications • clock enable for address and data. Rising edge for active low latches. When the clock enable signal is asserted the ff sees the. Clock Enable.

From www.mikrocontroller.net

Clock Enable, wie macht man's richtig? Clock Enable Rising edge for active low latches. For an active high latch, the gating signal should toggle on the falling edge of the clock. Normally you would use an edge sensitive flop to hold latch_update_en to prevent. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Features •. Clock Enable.

From www.youtube.com

How to Enable Dual Clocks on Any iPhone Lock Screen🔥🔥🔥. YouTube Clock Enable Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. The obvious answer is to pass. Clock Enable.

From tabletmonkeys.com

How to Display Seconds on Your Android and iPhone Clock Clock Enable Features • ideal for addressable register applications • clock enable for address and data. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Rising edge for active. Clock Enable.

From www.youtube.com

How To enable Screen Off clock or Ambient Display OPPO Care YouTube Clock Enable Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. The obvious answer is to pass the clock and enable through an and gate, but that breaks the. Clock Enable.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Based Clock Gating Clock Enable The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. Rising edge for active low latches. Hi, i have a state machine (with about 12. Clock Enable.

From www.yumpu.com

Clock Enable Clock Gating Clock Enable Normally you would use an edge sensitive flop to hold latch_update_en to prevent. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Rising edge for active low latches. Hi,. Clock Enable.

From www.comtechsolutions.com

Payroll > Time Clock > Enable Time Clock Hours Calculation Clock Enable When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. For an active high latch, the gating signal should toggle on the falling edge of the clock. Rising edge. Clock Enable.

From slideplayer.com

SPI Protocol and DAC Interfacing ppt download Clock Enable Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. Features • ideal for addressable register applications • clock enable for address and data. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if. Clock Enable.

From www.slideserve.com

PPT FIGURES FOR CHAPTER 11 LATCHES AND FLIPFLOPS PowerPoint Presentation ID6972526 Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Rising edge for active low latches. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. For an active high latch, the gating. Clock Enable.

From www.youtube.com

How to Enable Clock with Seconds in System Tray in Windows 11 25247 YouTube Clock Enable The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. For an active high latch, the gating signal should toggle on the falling edge of the clock. When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Normally you would. Clock Enable.

From www.msftnext.com

How to enable seconds for taskbar clock in Windows 11 Clock Enable The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Features • ideal for addressable register applications • clock enable for address and data. Rising edge for active low latches. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues. Clock Enable.

From www.researchgate.net

(a) Dflipflop. (b) Reset synchronicity. (c) Resetclock contest. Download Scientific Diagram Clock Enable Rising edge for active low latches. Features • ideal for addressable register applications • clock enable for address and data. For an active high latch, the gating signal should toggle on the falling edge of the clock. Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Learn how to create a clock enable signal instead of. Clock Enable.

From vlsimaster.com

Clock Gating VLSI Master Clock Enable Rising edge for active low latches. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and. Clock Enable.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Enable Rising edge for active low latches. For an active high latch, the gating signal should toggle on the falling edge of the clock. Normally you would use an edge sensitive flop to hold latch_update_en to prevent. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement. Clock Enable.

From hohpasavvy.weebly.com

Hot alarm clock enable sleep mode windows hohpasavvy Clock Enable When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Rising edge for active low latches. Features • ideal for addressable register applications • clock enable for address and data. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing. Clock Enable.

From itstechbased.com

How to Enable Clock with Seconds in Windows 11 Main Release Tech Based Clock Enable Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Rising edge for active low latches. The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. For an active. Clock Enable.

From www.youtube.com

How to Generate a Clock Signal with a 555 timer The Learning Circuit YouTube Clock Enable When the clock enable signal is asserted the ff sees the clock normally and things proceed as expected. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. For an active high latch, the gating signal should toggle on the falling. Clock Enable.

From www.youtube.com

How To Enable Seconds In Windows 10 Taskbar Clock YouTube Clock Enable The obvious answer is to pass the clock and enable through an and gate, but that breaks the don't gate clocks rule. Features • ideal for addressable register applications • clock enable for address and data. Learn how to create a clock enable signal instead of another clock domain to avoid fpga timing issues and clock domain crossing problems. Rising. Clock Enable.

From technoresult.com

How to Sync Clock using Command Prompt in Windows 11? Technoresult Clock Enable Features • ideal for addressable register applications • clock enable for address and data. Hi, i have a state machine (with about 12 states), and there is an enable signal, that actually is used inside any else/if statement inside each one of those. Rising edge for active low latches. Learn how to create a clock enable signal instead of another. Clock Enable.