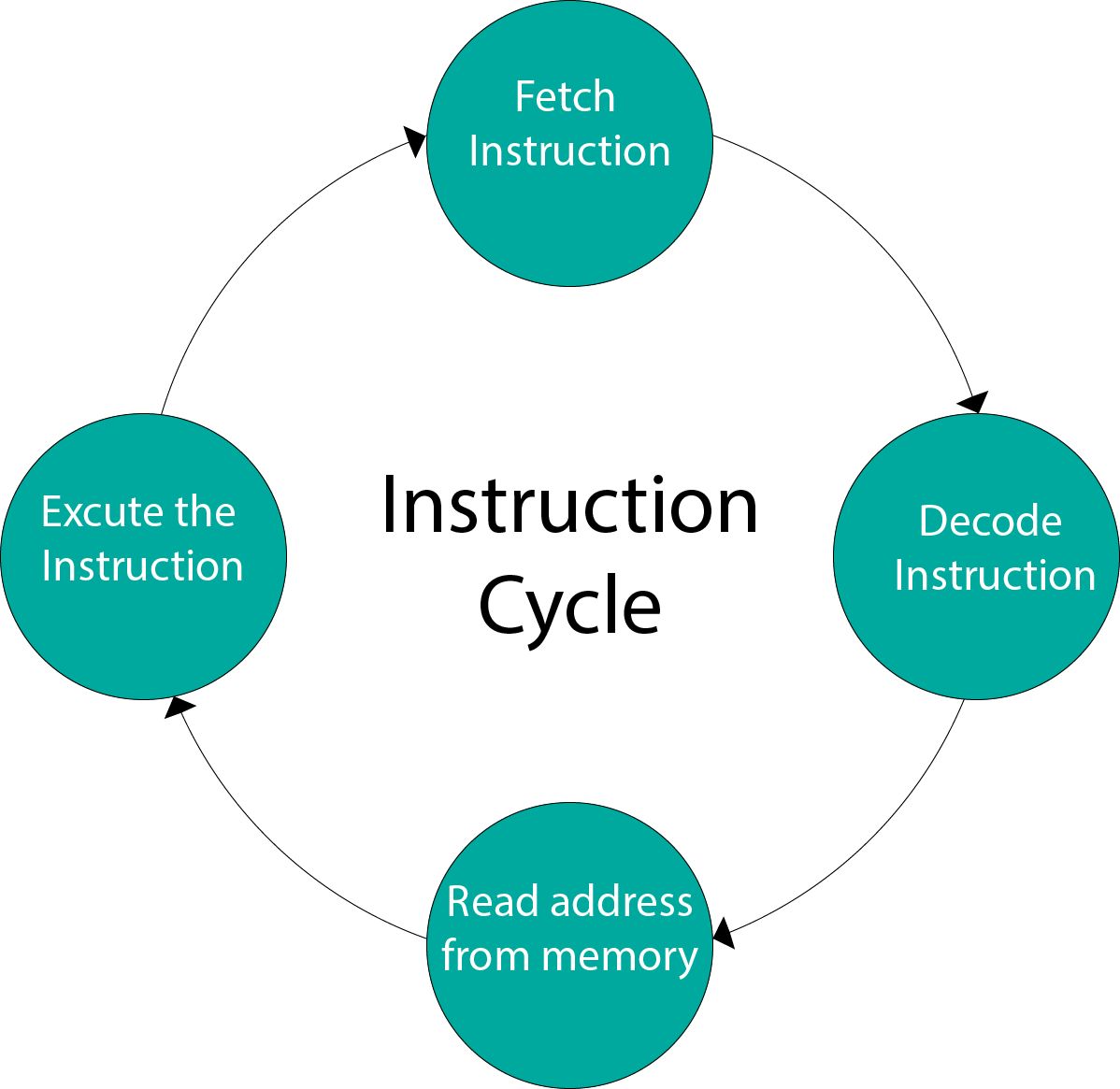

Instruction Execution Timing . An an instruction cycle consists of one to six. The time taken by the processor to complete the execution of an instruction. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. The major steps in the instruction cycle are:. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. Understand the concepts of instruction format,. In this lecture we will look at encoding schemes and approximate speed calculations. These vary by cpu architecture, but the best resource currently for. First, you need the actual timings. The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. The von newman architecture model of a computer states that the cpu is responsible for. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle.

from www.javatpoint.com

First, you need the actual timings. The time taken by the processor to complete the execution of an instruction. The major steps in the instruction cycle are:. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. Understand the concepts of instruction format,. These vary by cpu architecture, but the best resource currently for. In this lecture we will look at encoding schemes and approximate speed calculations. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. An an instruction cycle consists of one to six. The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction.

Instruction Cycle Computer Organization and Architecture Tutorial

Instruction Execution Timing The von newman architecture model of a computer states that the cpu is responsible for. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. First, you need the actual timings. The von newman architecture model of a computer states that the cpu is responsible for. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. In this lecture we will look at encoding schemes and approximate speed calculations. These vary by cpu architecture, but the best resource currently for. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. An an instruction cycle consists of one to six. The major steps in the instruction cycle are:. Understand the concepts of instruction format,. The time taken by the processor to complete the execution of an instruction.

From www.slideserve.com

PPT Chapter 1 Introduction PowerPoint Presentation, free download Instruction Execution Timing In this lecture we will look at encoding schemes and approximate speed calculations. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. First, you need the actual timings. Understand the concepts of instruction format,. An an instruction cycle consists of one to six. The instruction fetch step will fetch the instruction located at the address given. Instruction Execution Timing.

From www.youtube.com

Timing diagram of CALL instruction Basics and Working principle Instruction Execution Timing These vary by cpu architecture, but the best resource currently for. An an instruction cycle consists of one to six. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. Understand the concepts of instruction format,. The major steps in the instruction cycle are:. In this lecture. Instruction Execution Timing.

From www.geeksforgeeks.org

Timing diagram of INR M Instruction Execution Timing The time taken by the processor to complete the execution of an instruction. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. In this lecture we will look at encoding schemes and approximate speed calculations. First, you need the actual timings. The instruction fetch step will fetch the instruction located at the address given in the. Instruction Execution Timing.

From slideplayer.com

ECE 3430 Intro to Systems ppt download Instruction Execution Timing An an instruction cycle consists of one to six. Understand the concepts of instruction format,. The time taken by the processor to complete the execution of an instruction. The major steps in the instruction cycle are:. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. Learn. Instruction Execution Timing.

From www.brainkart.com

Instruction Execution and Timing Diagram Instruction Execution Timing An an instruction cycle consists of one to six. In this lecture we will look at encoding schemes and approximate speed calculations. These vary by cpu architecture, but the best resource currently for. The time taken by the processor to complete the execution of an instruction. The instruction cycle consists of several steps, each of which performs a specific function. Instruction Execution Timing.

From slideplayer.com

ECE 3430 Intro to Systems ppt download Instruction Execution Timing These vary by cpu architecture, but the best resource currently for. First, you need the actual timings. In this lecture we will look at encoding schemes and approximate speed calculations. The time taken by the processor to complete the execution of an instruction. Understand the concepts of instruction format,. The instruction cycle consists of several steps, each of which performs. Instruction Execution Timing.

From www.slideserve.com

PPT C H A P T E R PowerPoint Presentation, free download ID528163 Instruction Execution Timing These vary by cpu architecture, but the best resource currently for. In this lecture we will look at encoding schemes and approximate speed calculations. Understand the concepts of instruction format,. An an instruction cycle consists of one to six. The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. •. Instruction Execution Timing.

From schematicpartebriose.z14.web.core.windows.net

Timing Diagram Of Instruction Pipeline Instruction Execution Timing The time taken by the processor to complete the execution of an instruction. An an instruction cycle consists of one to six. The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. First, you need the actual timings. • in fact, instruction execution latency can be even longer (why?) •. Instruction Execution Timing.

From www.slideserve.com

PPT CPU Performance Evaluation Cycles Per Instruction (CPI Instruction Execution Timing First, you need the actual timings. An an instruction cycle consists of one to six. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. The von newman architecture model of a computer states that the cpu is responsible for. The time taken by the processor to complete the execution of an instruction. These vary by cpu. Instruction Execution Timing.

From slideplayer.com

ECE 3430 Intro to Systems ppt download Instruction Execution Timing First, you need the actual timings. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. The time taken by the processor to complete the execution of an instruction. The instruction cycle consists of several steps, each of which performs a specific function in the execution of. Instruction Execution Timing.

From www.scribd.com

8085 3 Instruction Execution & Timing Diagram PDF Central Instruction Execution Timing The von newman architecture model of a computer states that the cpu is responsible for. The time taken by the processor to complete the execution of an instruction. These vary by cpu architecture, but the best resource currently for. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves. Instruction Execution Timing.

From mcatutorials.com

Timing Diagrams Instruction Execution Timing First, you need the actual timings. The major steps in the instruction cycle are:. The von newman architecture model of a computer states that the cpu is responsible for. These vary by cpu architecture, but the best resource currently for. An an instruction cycle consists of one to six. • in fact, instruction execution latency can be even longer (why?). Instruction Execution Timing.

From dokumen.tips

(PDF) TriCore Pipeline Behaviour & Instruction Execution Timing Instruction Execution Timing The von newman architecture model of a computer states that the cpu is responsible for. In this lecture we will look at encoding schemes and approximate speed calculations. First, you need the actual timings. These vary by cpu architecture, but the best resource currently for. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. The major. Instruction Execution Timing.

From www.slideserve.com

PPT 13 Instruction Execution Steps PowerPoint Presentation, free Instruction Execution Timing The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. In this lecture we will look at encoding schemes and approximate speed calculations. Understand the concepts of instruction format,. The time taken by the processor to complete the execution of an instruction. These vary by cpu architecture, but the best. Instruction Execution Timing.

From www.brainkart.com

Instruction Execution and Timing Diagram Instruction Execution Timing In this lecture we will look at encoding schemes and approximate speed calculations. The von newman architecture model of a computer states that the cpu is responsible for. The major steps in the instruction cycle are:. These vary by cpu architecture, but the best resource currently for. The instruction cycle consists of several steps, each of which performs a specific. Instruction Execution Timing.

From www.slideserve.com

PPT Topic 5 Instruction Scheduling PowerPoint Presentation, free Instruction Execution Timing The von newman architecture model of a computer states that the cpu is responsible for. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. First, you need the actual timings. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. The instruction fetch. Instruction Execution Timing.

From www.numerade.com

The instruction execution timing diagram of an Intel 8051 Instruction Execution Timing First, you need the actual timings. The von newman architecture model of a computer states that the cpu is responsible for. An an instruction cycle consists of one to six. The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. The time taken by the processor to complete the execution. Instruction Execution Timing.

From www.slideshare.net

Instruction pipelining Instruction Execution Timing Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. An an instruction cycle consists of one to six. Understand the concepts of instruction format,. The instruction fetch step will fetch the instruction located. Instruction Execution Timing.

From www.slideserve.com

PPT Microprocessor PowerPoint Presentation, free download ID3257914 Instruction Execution Timing The major steps in the instruction cycle are:. In this lecture we will look at encoding schemes and approximate speed calculations. First, you need the actual timings. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. An an instruction cycle consists of one to six. The instruction fetch step will fetch the instruction located at the. Instruction Execution Timing.

From www.geeksforgeeks.org

Timing diagram of MVI instruction Instruction Execution Timing The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. The von newman architecture model of a computer states that the cpu is responsible for. The time taken by the processor to complete the execution of an instruction. Learn how the cpu executes program instructions by performing. Instruction Execution Timing.

From www.slideserve.com

PPT Peformance Measurements PowerPoint Presentation, free download Instruction Execution Timing These vary by cpu architecture, but the best resource currently for. Understand the concepts of instruction format,. An an instruction cycle consists of one to six. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. The instruction cycle consists of several steps, each of which performs. Instruction Execution Timing.

From www.slideserve.com

PPT Topic 5 Instruction Scheduling PowerPoint Presentation, free Instruction Execution Timing • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. The von newman architecture model of a computer states that the cpu is responsible for. The instruction cycle consists of several steps, each of. Instruction Execution Timing.

From www.javatpoint.com

Instruction Cycle Computer Organization and Architecture Tutorial Instruction Execution Timing First, you need the actual timings. In this lecture we will look at encoding schemes and approximate speed calculations. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. These vary by cpu architecture,. Instruction Execution Timing.

From courses.cs.washington.edu

Time and instruction execution Instruction Execution Timing The time taken by the processor to complete the execution of an instruction. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. First, you need the actual timings. The major steps in the instruction cycle are:. • in fact, instruction execution latency can be even longer. Instruction Execution Timing.

From www.slideserve.com

PPT CPU Performance Evaluation Cycles Per Instruction (CPI Instruction Execution Timing An an instruction cycle consists of one to six. The von newman architecture model of a computer states that the cpu is responsible for. First, you need the actual timings. These vary by cpu architecture, but the best resource currently for. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) •. Instruction Execution Timing.

From www.slideserve.com

PPT ATmega 2560 Datasheet PowerPoint Presentation, free download ID Instruction Execution Timing The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. An an instruction cycle consists of one to six. In this lecture we will look at encoding schemes and approximate speed calculations. Understand the concepts of instruction format,. The von newman architecture model of a computer states that the cpu. Instruction Execution Timing.

From slideplayer.com

ECE 3430 Intro to Systems ppt download Instruction Execution Timing In this lecture we will look at encoding schemes and approximate speed calculations. The time taken by the processor to complete the execution of an instruction. First, you need the actual timings. The von newman architecture model of a computer states that the cpu is responsible for. Understand the concepts of instruction format,. These vary by cpu architecture, but the. Instruction Execution Timing.

From www.bartleby.com

Execution of Instruction bartleby Instruction Execution Timing The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. The time taken by the processor to complete the execution of an instruction. First, you need the actual timings. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves. Instruction Execution Timing.

From www.brainkart.com

Instruction Execution and Timing Diagram Instruction Execution Timing The time taken by the processor to complete the execution of an instruction. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. In this lecture we will look at encoding schemes and approximate speed calculations. The instruction cycle consists of several steps, each of which performs. Instruction Execution Timing.

From www.chegg.com

Question 3 The instruction execution timing diagram Instruction Execution Timing The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. In this lecture we will look at encoding schemes and approximate speed calculations. The time taken by. Instruction Execution Timing.

From www.brainkart.com

Instruction Execution and Timing Diagram Instruction Execution Timing These vary by cpu architecture, but the best resource currently for. The time taken by the processor to complete the execution of an instruction. Learn how the cpu executes program instructions by performing fetch, decode, execute cycle. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program.. Instruction Execution Timing.

From www.slideserve.com

PPT Atmega32 Architectural Overview PowerPoint Presentation, free Instruction Execution Timing • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. The instruction fetch step will fetch the instruction located at the address given in the pc register (which is the instruction at memory. Understand the concepts of instruction format,. The von newman architecture model of a computer. Instruction Execution Timing.

From www.slideserve.com

PPT CPU08 INTRODUCTION PowerPoint Presentation, free download ID Instruction Execution Timing These vary by cpu architecture, but the best resource currently for. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput” (what is throughput?) • it improves the program. In this lecture we will look at encoding schemes and approximate speed calculations. An an instruction cycle consists of one to six. The instruction fetch step. Instruction Execution Timing.

From www.youtube.com

8085 Timing For Execution Of In Instruction YouTube Instruction Execution Timing The time taken by the processor to complete the execution of an instruction. The von newman architecture model of a computer states that the cpu is responsible for. These vary by cpu architecture, but the best resource currently for. First, you need the actual timings. • in fact, instruction execution latency can be even longer (why?) • pipelining improves “throughput”. Instruction Execution Timing.

From slideplayer.com

ECE 3430 Intro to Systems ppt download Instruction Execution Timing The instruction cycle consists of several steps, each of which performs a specific function in the execution of the instruction. The von newman architecture model of a computer states that the cpu is responsible for. First, you need the actual timings. These vary by cpu architecture, but the best resource currently for. The instruction fetch step will fetch the instruction. Instruction Execution Timing.