Xilinx Jtag Terminal . How can i do this? However, in preperation for a. I wish to use a jtag uart terminal from xsdb for stdout and stdin. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Defines a five wire serial interface known as the tap, or test access port. Connecting to a server with more than 32 devices in a jtag. Consists of the signals tck, tms, tdi, tdi, and trst (optional). Reconnecting to a target device with a lower jtag clock frequency.39. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger.

from www.george-smart.co.uk

After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Reconnecting to a target device with a lower jtag clock frequency.39. I wish to use a jtag uart terminal from xsdb for stdout and stdin. Connecting to a server with more than 32 devices in a jtag. However, in preperation for a. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. How can i do this? Consists of the signals tck, tms, tdi, tdi, and trst (optional). Defines a five wire serial interface known as the tap, or test access port.

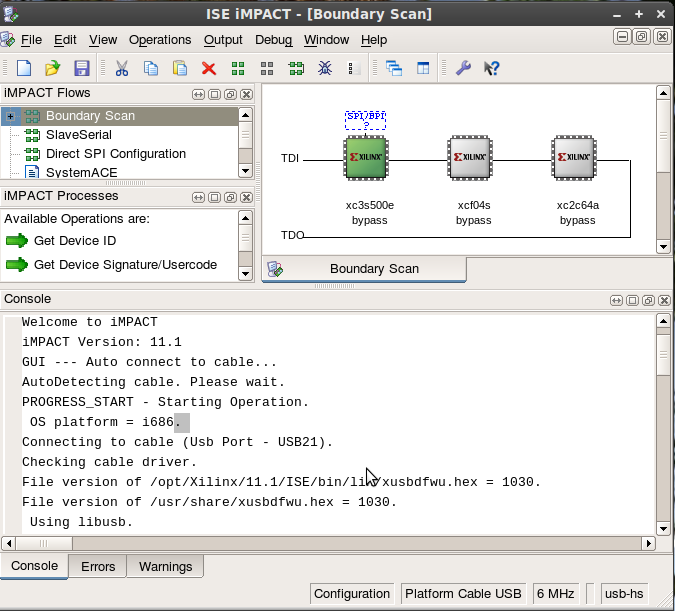

Xilinx JTAG Linux OLD Smart M1GEO

Xilinx Jtag Terminal How can i do this? Consists of the signals tck, tms, tdi, tdi, and trst (optional). However, in preperation for a. Reconnecting to a target device with a lower jtag clock frequency.39. Defines a five wire serial interface known as the tap, or test access port. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. I wish to use a jtag uart terminal from xsdb for stdout and stdin. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Connecting to a server with more than 32 devices in a jtag. How can i do this?

From linuxjedi.co.uk

Revisiting Xilinx JTAG Programming from a Raspberry Pi LinuxJedi's Xilinx Jtag Terminal However, in preperation for a. How can i do this? Reconnecting to a target device with a lower jtag clock frequency.39. Defines a five wire serial interface known as the tap, or test access port. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Consists of the signals tck,. Xilinx Jtag Terminal.

From kamami.pl

Xilinx FPGA Programmer JTAGSMT3NC MSL 6 (410357) Kamami online Xilinx Jtag Terminal Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. However, in preperation for a. Reconnecting to a target device with a lower jtag clock frequency.39. Defines a five wire serial interface known as the tap, or test access port. How can i do this? I wish to use a jtag uart. Xilinx Jtag Terminal.

From www.xilinx.com

AR 66370 XSDB Using JTAG UART Terminal on System Debugger Xilinx Jtag Terminal How can i do this? Defines a five wire serial interface known as the tap, or test access port. Reconnecting to a target device with a lower jtag clock frequency.39. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Consists of the signals tck, tms, tdi, tdi, and trst (optional). However,. Xilinx Jtag Terminal.

From blog.csdn.net

自制Xilinx JTAG仿真器_xilinx hs2 diyCSDN博客 Xilinx Jtag Terminal Reconnecting to a target device with a lower jtag clock frequency.39. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. However, in preperation for a. How can i do this? Defines a five wire serial interface known as the tap, or test access port. I wish to use a. Xilinx Jtag Terminal.

From fado.vn

Mua QuiExact Xilinx JTAG Development Tool JTAGSMT2 Compiler Compatible Xilinx Jtag Terminal After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. However, in preperation for a. How can i do this? Consists of the signals tck, tms, tdi, tdi, and trst (optional). Connecting to a server with more than 32 devices in a jtag. Defines a five wire serial interface known. Xilinx Jtag Terminal.

From pldkit.com

XPL1 XILINX LPT JTAG PROGRAMMER Xilinx Jtag Terminal Connecting to a server with more than 32 devices in a jtag. I wish to use a jtag uart terminal from xsdb for stdout and stdin. Reconnecting to a target device with a lower jtag clock frequency.39. Defines a five wire serial interface known as the tap, or test access port. After you create the “hello world” application, work through. Xilinx Jtag Terminal.

From schematicfixgrunwald.z19.web.core.windows.net

Xilinx Jtag Programmer Schematic Xilinx Jtag Terminal After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Defines a five wire serial interface known as the tap, or test access port. Consists of the signals tck, tms, tdi, tdi, and trst (optional). I wish to use a jtag uart terminal from xsdb for stdout and stdin. Xilinx. Xilinx Jtag Terminal.

From matthewtran.dev

FTDI Xilinx JTAG Programmer Matthew Tran’s Blog! Xilinx Jtag Terminal However, in preperation for a. Consists of the signals tck, tms, tdi, tdi, and trst (optional). After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Connecting to a server with more than 32 devices in a jtag. Reconnecting to a target device with a lower jtag clock frequency.39. Defines. Xilinx Jtag Terminal.

From fpgatechsolution.com

XILINX USB JTAG Xilinx Jtag Terminal Connecting to a server with more than 32 devices in a jtag. However, in preperation for a. Defines a five wire serial interface known as the tap, or test access port. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. How can i do this? Reconnecting to a target. Xilinx Jtag Terminal.

From linuxjedi.co.uk

Programming Xilinx JTAG from a Raspberry Pi LinuxJedi's /dev/null Xilinx Jtag Terminal Connecting to a server with more than 32 devices in a jtag. Defines a five wire serial interface known as the tap, or test access port. How can i do this? After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. I wish to use a jtag uart terminal from. Xilinx Jtag Terminal.

From fpga.eetrend.com

Xilinx FPGA的JTAG接口 FPGA 开发圈 Xilinx Jtag Terminal After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Consists of the signals tck, tms, tdi, tdi, and trst (optional). I wish to use a jtag uart terminal from xsdb for stdout and stdin. How can i do this? Connecting to a server with more than 32 devices in. Xilinx Jtag Terminal.

From electronics.stackexchange.com

xilinx Terminal resistor function on JTAG SMT2 schematic Electrical Xilinx Jtag Terminal Consists of the signals tck, tms, tdi, tdi, and trst (optional). Connecting to a server with more than 32 devices in a jtag. Defines a five wire serial interface known as the tap, or test access port. Reconnecting to a target device with a lower jtag clock frequency.39. After you create the “hello world” application, work through the following example. Xilinx Jtag Terminal.

From www.prime-sys.co.jp

JTAG変換ケーブル PSIテクニカルサポート Xilinx Jtag Terminal Defines a five wire serial interface known as the tap, or test access port. How can i do this? Consists of the signals tck, tms, tdi, tdi, and trst (optional). Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. I wish to use a jtag uart terminal from xsdb for stdout. Xilinx Jtag Terminal.

From linuxjedi.co.uk

Revisiting Xilinx JTAG Programming from a Raspberry Pi LinuxJedi's Xilinx Jtag Terminal After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Defines a five wire serial interface known as the tap, or test access port. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. I wish to use a jtag uart terminal. Xilinx Jtag Terminal.

From omatompower.com

XILINX Emulator JTAG Programmer for FPGA CPLD CMod XC2C64A D Xilinx Jtag Terminal How can i do this? Defines a five wire serial interface known as the tap, or test access port. Consists of the signals tck, tms, tdi, tdi, and trst (optional). Reconnecting to a target device with a lower jtag clock frequency.39. Connecting to a server with more than 32 devices in a jtag. Xilinx system debugger¶ the vitis software platform. Xilinx Jtag Terminal.

From eren80epil.over-blog.com

Xilinx jtag uart eren80epil Xilinx Jtag Terminal However, in preperation for a. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Consists of the signals tck, tms, tdi, tdi, and trst (optional). How can i do this? Defines a five wire serial interface known as the tap, or test access port. Connecting to a server with. Xilinx Jtag Terminal.

From mungfali.com

Xilinx Jtag Header Pinout Xilinx Jtag Terminal However, in preperation for a. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. How can i do this? Consists of the signals tck, tms, tdi, tdi, and trst (optional). I wish to use a jtag uart terminal from xsdb for stdout and stdin. Xilinx system debugger¶ the vitis. Xilinx Jtag Terminal.

From fpgatechsolution.com

XILINX USB JTAG Xilinx Jtag Terminal Reconnecting to a target device with a lower jtag clock frequency.39. I wish to use a jtag uart terminal from xsdb for stdout and stdin. Consists of the signals tck, tms, tdi, tdi, and trst (optional). How can i do this? Defines a five wire serial interface known as the tap, or test access port. However, in preperation for a.. Xilinx Jtag Terminal.

From pldkit.com

XPL1 XILINX LPT JTAG PROGRAMMER Xilinx Jtag Terminal After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Reconnecting to a target device with a lower jtag clock frequency.39. Defines a five wire serial interface known as the tap, or test access port. I wish to use a jtag uart terminal from xsdb for stdout and stdin. Xilinx. Xilinx Jtag Terminal.

From www.cdream5.com

XiLinx CPLD&FPGA JTAG下载线 Create Dream Xilinx Jtag Terminal After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Defines a five wire serial interface known as the tap, or test access port. I wish to use a jtag uart terminal from xsdb for stdout and stdin. How can i do this? Reconnecting to a target device with a. Xilinx Jtag Terminal.

From www.george-smart.co.uk

Xilinx JTAG Linux OLD Smart M1GEO Xilinx Jtag Terminal How can i do this? After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Consists of the signals tck, tms, tdi, tdi, and trst (optional). Reconnecting to a target device with a lower jtag clock frequency.39. Defines a five wire serial interface known as the tap, or test access. Xilinx Jtag Terminal.

From userdatabiermann.z19.web.core.windows.net

Xilinx Jtag Programmer Schematic Xilinx Jtag Terminal Defines a five wire serial interface known as the tap, or test access port. I wish to use a jtag uart terminal from xsdb for stdout and stdin. Reconnecting to a target device with a lower jtag clock frequency.39. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Consists. Xilinx Jtag Terminal.

From tomverbeure.github.io

Pano Logic JTAG First Contact Electronics etc… Xilinx Jtag Terminal Reconnecting to a target device with a lower jtag clock frequency.39. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Consists of the signals tck, tms, tdi, tdi, and trst (optional). How can i do this? After you create the “hello world” application, work through the following example to debug the. Xilinx Jtag Terminal.

From www.amazon.in

Sinkr JTAG Download Debugger DLC9 DLC9LP Compatible for XILINX Platform Xilinx Jtag Terminal However, in preperation for a. How can i do this? Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Reconnecting to a target device with a lower jtag clock frequency.39. Consists of the signals tck, tms, tdi, tdi, and trst (optional). Defines a five wire serial interface known as the tap,. Xilinx Jtag Terminal.

From matallworld.web.fc2.com

Xilinx Digilent Usb Jtag Driver Xilinx Jtag Terminal Connecting to a server with more than 32 devices in a jtag. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Consists of the signals tck, tms, tdi, tdi, and trst (optional). However, in preperation for a. How can i do this? Reconnecting to a target device with a lower jtag. Xilinx Jtag Terminal.

From ebics.net

Xilinx JTAG Capabilities and System Design HIGHEND FPGA Distributor Xilinx Jtag Terminal Defines a five wire serial interface known as the tap, or test access port. Reconnecting to a target device with a lower jtag clock frequency.39. I wish to use a jtag uart terminal from xsdb for stdout and stdin. How can i do this? Consists of the signals tck, tms, tdi, tdi, and trst (optional). However, in preperation for a.. Xilinx Jtag Terminal.

From www.61ic.com

【E1467】Xilinx JTAGSMT2全套设计资料FPGA索炜达电子 Xilinx Jtag Terminal Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Defines a five wire serial interface known as the tap, or test access port. Connecting to a server with more than 32 devices in a jtag. How can i do this? I wish to use a jtag uart terminal from xsdb for. Xilinx Jtag Terminal.

From pldkit.com

XPL1 XILINX LPT JTAG PROGRAMMER Xilinx Jtag Terminal How can i do this? Consists of the signals tck, tms, tdi, tdi, and trst (optional). Reconnecting to a target device with a lower jtag clock frequency.39. Connecting to a server with more than 32 devices in a jtag. Defines a five wire serial interface known as the tap, or test access port. However, in preperation for a. I wish. Xilinx Jtag Terminal.

From kamami.pl

TE079003 XMOD FTDI JTAG adapter (Xilinx compatible) Kamami online Xilinx Jtag Terminal I wish to use a jtag uart terminal from xsdb for stdout and stdin. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. However, in preperation for a. Defines a five wire serial interface known as the tap, or test access port. After you create the “hello world” application, work through. Xilinx Jtag Terminal.

From www.aliexpress.com

FC 40P 40Pin JTAG ALTERA XILINX C8051F AVR Download Line 30cm Pitch 2 Xilinx Jtag Terminal Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Reconnecting to a target device with a lower jtag clock frequency.39. How can i do this? Consists of the signals tck, tms, tdi, tdi, and trst (optional). However, in preperation for a. After you create the “hello world” application, work through the. Xilinx Jtag Terminal.

From www.tiaowiki.com

Config TIAO Universal JTAG Cable As A Buffered Xilinx Parallel Platform Xilinx Jtag Terminal However, in preperation for a. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. I wish to use a jtag uart terminal from xsdb for stdout and stdin. How can i do this? Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line. Xilinx Jtag Terminal.

From www.researchgate.net

Xilinx System Generator Black Box JTAG Implementation? ResearchGate Xilinx Jtag Terminal Connecting to a server with more than 32 devices in a jtag. I wish to use a jtag uart terminal from xsdb for stdout and stdin. How can i do this? Defines a five wire serial interface known as the tap, or test access port. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code. Xilinx Jtag Terminal.

From www.desertcart.ie

Buy Xilinx JTAG Download High Speed Programmer JTAGSMT2 Compatible Xilinx Jtag Terminal Reconnecting to a target device with a lower jtag clock frequency.39. Connecting to a server with more than 32 devices in a jtag. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Defines a five wire serial interface known as the tap, or test access port. Consists of the. Xilinx Jtag Terminal.

From matthewtran.dev

FTDI Xilinx JTAG Programmer Matthew Tran's Blog! Xilinx Jtag Terminal Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. However, in preperation for a. Defines a five wire serial interface known as the tap, or test access port. After you create the “hello world” application, work through the following example to debug the software using the vitis debugger. Consists of the. Xilinx Jtag Terminal.

From blog.csdn.net

Xilinx XSCT 调试jtaguart , jtagterminal_jtag协议转uartCSDN博客 Xilinx Jtag Terminal How can i do this? I wish to use a jtag uart terminal from xsdb for stdout and stdin. Xilinx system debugger¶ the vitis software platform debugger enables you to step through your code line by line. Connecting to a server with more than 32 devices in a jtag. After you create the “hello world” application, work through the following. Xilinx Jtag Terminal.