Module Clock Divider . This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. Huge savingsbuy it now available This clock divider can be implemented using a free running simple wrap around counter as in figure5. The verilog clock divider is simulated and. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Have the xilinx ise webpack installed.

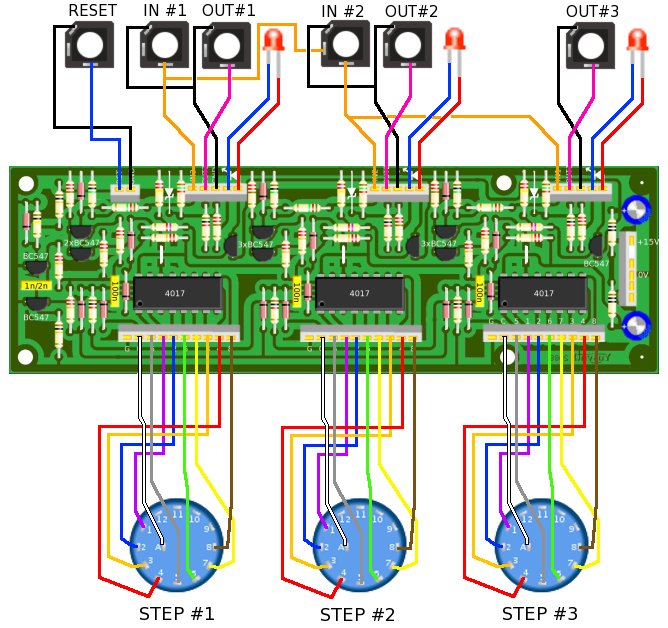

from www.soundtronics.co.uk

This clock divider can be implemented using a free running simple wrap around counter as in figure5. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The verilog clock divider is simulated and. Have the xilinx ise webpack installed. Huge savingsbuy it now available Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock.

YuSynth Clock Divider Module Bare PCB

Module Clock Divider This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. Huge savingsbuy it now available This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. Have the xilinx ise webpack installed. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. This clock divider can be implemented using a free running simple wrap around counter as in figure5. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The verilog clock divider is simulated and.

From www.etsy.com

Clock Divider V2 Eurorack Module Complete Kit Etsy Module Clock Divider This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. This clock divider can be implemented using a free running simple wrap around counter as in figure5. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Have the xilinx ise webpack installed. In. Module Clock Divider.

From www.bhphotovideo.com

4ms Rotating Clock Divider Kit Eurorack Module RCDKIT B&H Photo Module Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. The verilog clock divider is simulated and. This project includes a clock divider module (clockdivider) that can produce output clock. Module Clock Divider.

From www.youtube.com

Modular Tip Creative Uses for Clock Dividers! (ft. the Mazzatron Clock Divider) YouTube Module Clock Divider The verilog clock divider is simulated and. Have the xilinx ise webpack installed. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. In our case let us take input. Module Clock Divider.

From www.newgroove.it

4ms Rotating Clock Divider Breakout Module (RCDBO) da NewGroove.it Module Clock Divider Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. Have the xilinx ise webpack installed. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This verilog project provides full verilog code for the clock divider on fpga together with testbench. Module Clock Divider.

From www.gear4music.com

4ms Rotating Clock Divider Rev 2 (4HP) at Gear4music Module Clock Divider Have the xilinx ise webpack installed. This clock divider can be implemented using a free running simple wrap around counter as in figure5. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies. Module Clock Divider.

From www.soundtronics.co.uk

YuSynth Clock Divider Module Bare PCB Module Clock Divider Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Have the xilinx ise webpack installed.. Module Clock Divider.

From www.ebay.com

10 to 1 Clock Divider Frequency Divider module with multiple divisions eBay Module Clock Divider If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. Huge savingsbuy it now available This project includes a clock divider module (clockdivider) that can produce output clock signals at. Module Clock Divider.

From elevatorsound.com

2hp Div Eurorack Clock Divider Module (Black) Elevator Sound Module Clock Divider This clock divider can be implemented using a free running simple wrap around counter as in figure5. Have the xilinx ise webpack installed. The verilog clock divider is simulated and. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. In our case let us take input frequency. Module Clock Divider.

From www.worthpoint.com

4ms Rotating Clock Divider v2 Eurorack Module NEW [DETROIT MODULAR] 1814211691 Module Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Have the xilinx ise webpack installed. The verilog clock divider is simulated and. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. This verilog project provides full verilog code for the. Module Clock Divider.

From www.sweetwater.com

Doepfer A160 Eurorack Clock Divider Module Sweetwater Module Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. The verilog clock divider is simulated and. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Clock divider is also known as frequency divider, which divides the input clock frequency and. Module Clock Divider.

From synamodec.com

Clock Divider Module Clock Divider The verilog clock divider is simulated and. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. This clock divider can be implemented using a free running simple wrap around counter as in figure5. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by. Module Clock Divider.

From www.modulargrid.net

FPB 1U Clock Divider Eurorack Module on ModularGrid Module Clock Divider Have the xilinx ise webpack installed. The verilog clock divider is simulated and. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. If you generalize the clock divider by two, a smart and. Module Clock Divider.

From www.youtube.com

Simple Clock Divider and a Sub Oscillator DIY Module in a Week 8.1 YouTube Module Clock Divider Huge savingsbuy it now available The verilog clock divider is simulated and. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. This clock divider can be implemented using a free running simple wrap. Module Clock Divider.

From www.signalsounds.com

Shakmat Modular Time Wizard Eurorack Clock Divider Module Signal Sounds Module Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. Huge savingsbuy it now available This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies. Module Clock Divider.

From www.thanksbuyer.com

HF509 45MHz Frequency Divider Module Frequency Prescaler Clock Divider Divide By 2 4 8 64 128 Module Clock Divider This clock divider can be implemented using a free running simple wrap around counter as in figure5. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. Have the xilinx ise webpack installed. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output. Module Clock Divider.

From pushermanproductions.com

BUILT MODULE ST Modular Flitzem Defor (Brute Sequencer & Clock Divider) Pusherman Module Clock Divider Have the xilinx ise webpack installed. The verilog clock divider is simulated and. This clock divider can be implemented using a free running simple wrap around counter as in figure5. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Huge savingsbuy it now available In our case let us take input. Module Clock Divider.

From www.bhphotovideo.com

4ms Rotating Clock Divider Breakout RCDBOKIT BLACK PANEL B&H Module Clock Divider This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The verilog clock divider is simulated and. Huge savingsbuy it now available If you generalize the clock divider by two, a smart. Module Clock Divider.

From www.juno.co.uk

Wavefonix Clock Divider Module at Juno Records. Module Clock Divider This clock divider can be implemented using a free running simple wrap around counter as in figure5. Huge savingsbuy it now available If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Have the xilinx ise webpack installed. This verilog project provides full verilog code for the clock. Module Clock Divider.

From www.modulargrid.net

Barton Musical Circuits VC Master Clock/Divider Eurorack Module on ModularGrid Module Clock Divider The verilog clock divider is simulated and. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. Huge savingsbuy it now available This clock divider can be implemented using a free running simple wrap around counter as in figure5. Clock divider is also known as frequency divider, which divides the input clock. Module Clock Divider.

From www.soundtronics.co.uk

YuSynth Clock Divider Module Bare PCB Module Clock Divider If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Have the xilinx ise webpack installed. Huge savingsbuy it now available Clock divider is also known as frequency. Module Clock Divider.

From www.soundtronics.co.uk

YuSynth Clock Divider Module Laser Engraved 5U Laminate Front Panel Module Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Huge savingsbuy it now available Have the xilinx ise webpack installed. The verilog clock divider is simulated and.. Module Clock Divider.

From www.davidhaillant.com

UC Clock Divider Electronic things… and stuff Module Clock Divider If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. This clock divider can be implemented using a free running simple wrap around counter as in figure5. Have the xilinx. Module Clock Divider.

From reverb.com

Shakmat Modular Time Wizard Eurorack Clock Divider Module Reverb Module Clock Divider This clock divider can be implemented using a free running simple wrap around counter as in figure5. The verilog clock divider is simulated and. Have the xilinx ise webpack installed. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. Clock divider is also known as frequency divider, which divides the input. Module Clock Divider.

From reverb.com

4ms Rotating Clock Divider Eurorack Module rev 2 (RCD) Reverb UK Module Clock Divider Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. The verilog clock divider is simulated and. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. This project includes a clock divider module (clockdivider) that can produce output clock. Module Clock Divider.

From www.musicalinstrumentshoppe.com

2Hp Div Eurorack Clock Divider Module Silver Module Clock Divider Have the xilinx ise webpack installed. The verilog clock divider is simulated and. Huge savingsbuy it now available If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. This clock divider can be implemented using a free running simple wrap around counter as in figure5. In our case. Module Clock Divider.

From www.aliexpress.com

Store Home Products Feedback Module Clock Divider This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. Have the xilinx ise webpack installed. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Huge savingsbuy it now available This verilog project provides full verilog code for the. Module Clock Divider.

From www.elevatorsound.com

Doepfer A1602 Eurorack Clock Divider II Module Elevator Sound Module Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by.. Module Clock Divider.

From www.soundtronics.co.uk

YuSynth Clock Divider Module Aluminium Back Panel Module Clock Divider If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Huge savingsbuy it now available This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Have the xilinx ise webpack installed. Clock divider is also known as frequency divider, which. Module Clock Divider.

From www.vrogue.co

Modular Synth Clock Module Diy Arduino Sm Tik Tak Ard vrogue.co Module Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Have the xilinx ise webpack installed. The verilog clock divider is simulated and. This clock divider can be implemented using a free running simple wrap around counter as in figure5. If you generalize the clock divider by two, a smart. Module Clock Divider.

From midwestmodular.com

A1602 Clock Divider II Midwest Modular Module Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. The verilog clock divider is simulated and. Have the xilinx ise webpack installed. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. Huge savingsbuy it now available In our. Module Clock Divider.

From www.haraldswerk.de

www.haraldswerk.de Next Generation Formant Clock Divider Module Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. This clock divider can. Module Clock Divider.

From www.bhphotovideo.com

4ms Rotating Clock Divider Eurorack Module ROTATINGCLOCKDIVIDER Module Clock Divider Huge savingsbuy it now available This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. This clock divider can be implemented using a free running simple wrap around counter as in figure5. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. Clock divider. Module Clock Divider.

From reverb.com

Shakmat Modular Time Apprentice Eurorack Clock Divider Module Reverb Module Clock Divider Have the xilinx ise webpack installed. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. If you generalize the clock divider by two, a smart and efficient divider is the clock divider by a power of two. In our case let us take input frequency as 50mhz and divide the clock. Module Clock Divider.

From www.aliexpress.com

ClockDividerModule246812or16ClockDividerinputclockfrequencyup.jpg Module Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Huge savingsbuy it now available This clock divider can be implemented using a free running simple wrap around counter as in figure5. Have the xilinx ise webpack installed. In our case let us take input frequency as 50mhz and divide the clock. Module Clock Divider.

From reverb.com

2hp DIV Eurorack Clock Divider/Multipler Module (Silver) Reverb Module Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. This project includes a clock divider module (clockdivider) that can produce output clock signals at different frequencies by. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This clock divider can. Module Clock Divider.