Antenna Gate Area . This rule applies to any metal pattern connected to a gate of a transistor. The most common rule is called “antenna ratio”. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. We have described three different methods to fix the. The etch process builds up the electrical charges on metal layers. It defines a limit for the ratio between the area (or the. These charges cause a high voltage spike, which may damage the gates connected to. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide.

from www.vcars.org

This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. This rule applies to any metal pattern connected to a gate of a transistor. The most common rule is called “antenna ratio”. These charges cause a high voltage spike, which may damage the gates connected to. It defines a limit for the ratio between the area (or the. The etch process builds up the electrical charges on metal layers. We have described three different methods to fix the. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool.

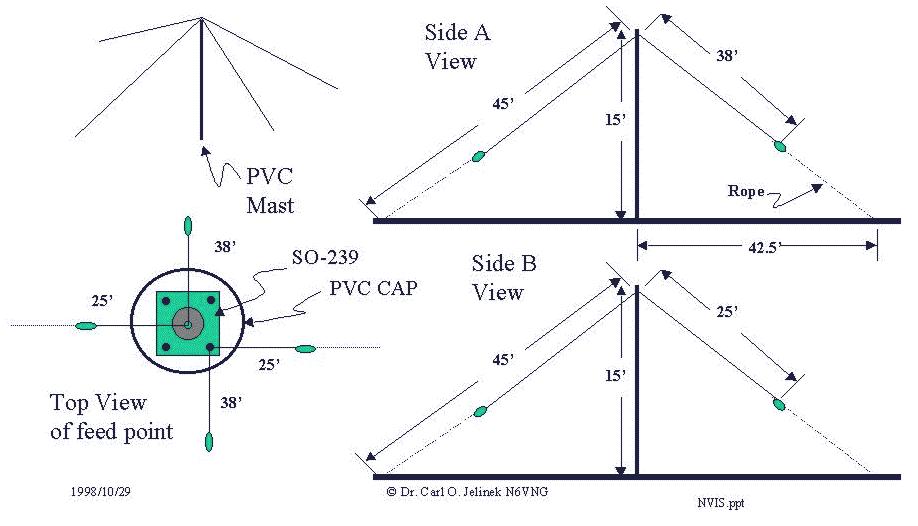

Near Vertical Incident Scattering Antenna

Antenna Gate Area How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. These charges cause a high voltage spike, which may damage the gates connected to. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. It defines a limit for the ratio between the area (or the. The etch process builds up the electrical charges on metal layers. The most common rule is called “antenna ratio”. This rule applies to any metal pattern connected to a gate of a transistor. We have described three different methods to fix the.

From oregonrfid.eu

Gate Antenna, 200x200x25mm,134kHz, 209,00 Antenna Gate Area This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. It defines a limit for the ratio between the area (or the. This rule applies to any. Antenna Gate Area.

From www.etechnog.com

How Antenna Works (Transmit or Receive Signal)? Learn with Diagram Antenna Gate Area This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. These charges cause a high voltage spike, which may damage the gates connected to. The. Antenna Gate Area.

From www.dxengineering.com

M2 Antennas 1030LP8 M2 Antennas HF Beam Antennas DX Engineering Antenna Gate Area The most common rule is called “antenna ratio”. It defines a limit for the ratio between the area (or the. This rule applies to any metal pattern connected to a gate of a transistor. We have described three different methods to fix the. This blog describes the antenna effect observed in the 16nm node design and the way to identify. Antenna Gate Area.

From www.researchgate.net

Human standing in the center of the antenna gate system [4] Download Antenna Gate Area These charges cause a high voltage spike, which may damage the gates connected to. The etch process builds up the electrical charges on metal layers. The most common rule is called “antenna ratio”. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. We have described. Antenna Gate Area.

From www.publicdomainpictures.net

Antenna On Communications Tower Free Stock Photo Public Domain Pictures Antenna Gate Area We have described three different methods to fix the. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. These. Antenna Gate Area.

From www.dreamstime.com

Multiple Antennas on the 4G Base Station Antenna Tower Stock Photo Antenna Gate Area These charges cause a high voltage spike, which may damage the gates connected to. The etch process builds up the electrical charges on metal layers. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. We have described three different methods to fix the. It defines a limit for the ratio. Antenna Gate Area.

From www.researchgate.net

Architecture of Large area scattered antenna array Download Antenna Gate Area This rule applies to any metal pattern connected to a gate of a transistor. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design. Antenna Gate Area.

From www.dxzone.com

OH2EC Antenna Resource Detail Antenna Gate Area How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. It defines a limit for the ratio between the area (or the. This rule applies to any metal pattern connected to a gate of a transistor. We have described three different methods to fix the. This blog describes the antenna effect. Antenna Gate Area.

From www.secureye.com

AM Antenna Gate & EAS AM Solution Secureye Antenna Gate Area We have described three different methods to fix the. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. This rule applies to any metal pattern connected to a gate of a transistor. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations. Antenna Gate Area.

From www.chegg.com

A rectangular horn antenna is represented by a Antenna Gate Area The most common rule is called “antenna ratio”. It defines a limit for the ratio between the area (or the. This rule applies to any metal pattern connected to a gate of a transistor. The etch process builds up the electrical charges on metal layers. This paper describes the antenna effect observed in the 16nm design and the way to. Antenna Gate Area.

From birrraus.com

Selecting The Correct Antenna and How To Point It Better for Antenna Gate Area It defines a limit for the ratio between the area (or the. The etch process builds up the electrical charges on metal layers. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. The most common rule is called “antenna ratio”. We have described three different methods to fix the. These. Antenna Gate Area.

From cde.nus.edu.sg

Deployable high gain antenna for CubeSats Engineering Design and Antenna Gate Area We have described three different methods to fix the. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. These charges cause a high voltage spike, which may damage the gates connected to. This rule applies to any metal pattern connected to a gate of a transistor. It defines a limit. Antenna Gate Area.

From www.youtube.com

Solutions of GATE (EC) Questions of Antenna Array YouTube Antenna Gate Area These charges cause a high voltage spike, which may damage the gates connected to. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. We have described three different methods to fix the. This paper describes the antenna effect observed in the 16nm design. Antenna Gate Area.

From www.alamy.com

5G radio transmitting tower with antennas for coverage Stock Photo Alamy Antenna Gate Area How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. We have described three different methods to fix the. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. These charges cause a high voltage spike, which. Antenna Gate Area.

From vfesupport.weebly.com

11 meter 5 element yagi antenna calculator vfesupport Antenna Gate Area This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. It defines a limit for the ratio between the area (or the. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. The most common. Antenna Gate Area.

From www.dxzone.com

HF Wire Antennas for Field Day The Antenna Gate Area This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. The etch process builds up the electrical charges on metal layers. These charges cause a high voltage spike, which may damage the gates connected to. It defines a limit for the ratio between the. Antenna Gate Area.

From www.mdpi.com

Sensors Free FullText LowProfile Broadband DualPolarized Dipole Antenna Gate Area The etch process builds up the electrical charges on metal layers. The most common rule is called “antenna ratio”. It defines a limit for the ratio between the area (or the. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. These charges cause. Antenna Gate Area.

From device.report

101G048 DX Base Station Antenna User Guide Antenna Gate Area The most common rule is called “antenna ratio”. These charges cause a high voltage spike, which may damage the gates connected to. It defines a limit for the ratio between the area (or the. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool.. Antenna Gate Area.

From www.atlasrfidstore.com

9 Tactics for Choosing an RFID Antenna Antenna Gate Area These charges cause a high voltage spike, which may damage the gates connected to. It defines a limit for the ratio between the area (or the. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. We have described three different methods to fix the. How. Antenna Gate Area.

From www.carrybagbd.com

58kHz Acrylic Antenna Gate Security AntiTheft Am EAS System Antenna Gate Area How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. The most common rule is called “antenna ratio”. We have described three different methods to fix the. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different. Antenna Gate Area.

From backendesign.blogspot.com

VLSI Backend Design Antenna Effect Antenna Gate Area The etch process builds up the electrical charges on metal layers. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. We have described three different methods to fix the. It defines a limit for the ratio between the area (or the. The most common rule is called “antenna ratio”. This. Antenna Gate Area.

From www.youtube.com

Antenna Parameters Fundamental Parameters of Antenna GATE EC Gate Antenna Gate Area We have described three different methods to fix the. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. This rule applies to any metal pattern connected to a gate of a transistor. This paper describes the antenna effect observed in the 16nm design. Antenna Gate Area.

From en.wikipedia.org

Monopole antenna Wikipedia Antenna Gate Area This rule applies to any metal pattern connected to a gate of a transistor. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. It defines a limit for the ratio between the area (or the. These charges cause a high voltage spike, which. Antenna Gate Area.

From www.vcars.org

Near Vertical Incident Scattering Antenna Antenna Gate Area How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. The etch process builds up the electrical charges on metal layers. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. This rule applies to any metal. Antenna Gate Area.

From www.steelpoletower.com

Triangle Self Supporting Antenna Tower Signal Transmission Guyed Wire Tower Antenna Gate Area This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. We have described three different methods to fix the. The most common rule is called “antenna ratio”. These charges cause a high voltage spike, which may damage the gates connected to. How do antenna. Antenna Gate Area.

From www.focus-rfid.com

High Quality UHF Gate Antenna Model STG5 Factory and Supplier FOCUS Antenna Gate Area The most common rule is called “antenna ratio”. These charges cause a high voltage spike, which may damage the gates connected to. It defines a limit for the ratio between the area (or the. We have described three different methods to fix the. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced. Antenna Gate Area.

From dxohzscbr.blob.core.windows.net

Homemade Cb Radio Base Station Antennas at Katherine Beatty blog Antenna Gate Area It defines a limit for the ratio between the area (or the. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. This rule applies to any metal pattern connected to a gate of a transistor. This paper describes the antenna effect observed in. Antenna Gate Area.

From www.cannondigi.com

2 Meter 440 Beam Antenna The Best Picture Of Beam Antenna Gate Area This rule applies to any metal pattern connected to a gate of a transistor. It defines a limit for the ratio between the area (or the. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. How do antenna violations occur, and what is the mechanism. Antenna Gate Area.

From commons.wikimedia.org

FileKBRC antenna tower.jpg Wikimedia Commons Antenna Gate Area These charges cause a high voltage spike, which may damage the gates connected to. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. It defines a limit for the ratio between the area (or the. We have described three different methods to fix the. This. Antenna Gate Area.

From cn.dreamstime.com

Multiple Antennas on the 4G Base Station Antenna Tower 库存图片 图片 包括有 蜂窝 Antenna Gate Area These charges cause a high voltage spike, which may damage the gates connected to. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. The etch process builds up the electrical charges on metal layers. How do antenna violations occur, and what is the mechanism to. Antenna Gate Area.

From backendesign.blogspot.com

VLSI Backend Design Antenna Effect Antenna Gate Area It defines a limit for the ratio between the area (or the. The etch process builds up the electrical charges on metal layers. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. We have described three different methods to fix the. These charges cause a high voltage spike, which may. Antenna Gate Area.

From stationproject.wordpress.com

Receive Antenna For The Low Bands Part 2 Second Shack Entry And Antenna Gate Area The most common rule is called “antenna ratio”. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design using different pv tool. It defines. Antenna Gate Area.

From commons.wikimedia.org

FileKBRC AM radio antenna tower.JPG Wikimedia Commons Antenna Gate Area This rule applies to any metal pattern connected to a gate of a transistor. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. This paper describes the antenna effect observed in the 16nm design and the way to identify antenna violations in design. Antenna Gate Area.

From www.rantecantennas.com

Slotted Array Antennas Your Guide to the Top Benefits Rantec Antenna Gate Area The etch process builds up the electrical charges on metal layers. We have described three different methods to fix the. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different pv tool. This paper describes the antenna effect observed in the 16nm design and the way. Antenna Gate Area.

From www.alamy.com

Omnidirectional satellite antenna hires stock photography and images Antenna Gate Area The most common rule is called “antenna ratio”. We have described three different methods to fix the. How do antenna violations occur, and what is the mechanism to occur antenna effect or plasma induced gate oxide. This blog describes the antenna effect observed in the 16nm node design and the way to identify antenna violations in chip(asic/fpga) design using different. Antenna Gate Area.