Logic Gates Of Vlsi Design . Y = x iff a = 1 (iff=if. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Objectives, metrics, design methodology, tools, and. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. An understanding of basic digital design: This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Boolean algebra, kmaps, gates and flip flops, finite state machine design. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Course outline, history and trends in vlsi design. Linear algebra and calculus at the level of a junior or senior in engineering. Optimizing the design’s area, power, and timing by fusing. How to design a chip: Logical effort g for logic gates.

from www.slideserve.com

An understanding of basic digital design: This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Course outline, history and trends in vlsi design. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Objectives, metrics, design methodology, tools, and. Logical effort g for logic gates. Y = x iff a = 1 (iff=if. Optimizing the design’s area, power, and timing by fusing. How to design a chip:

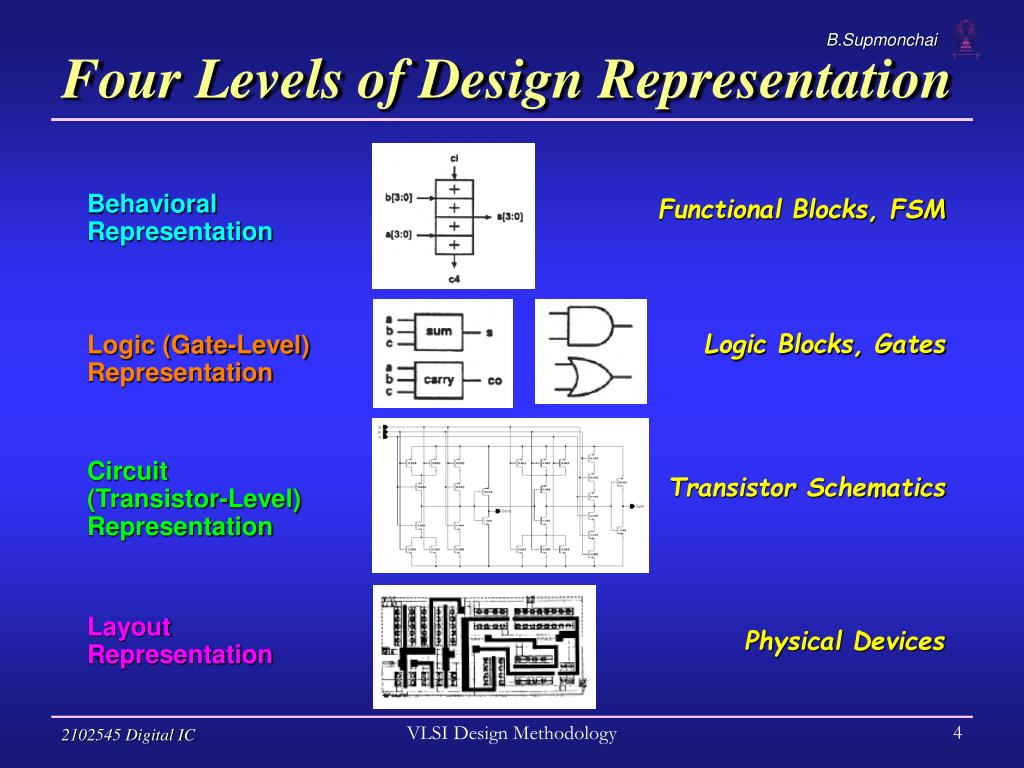

PPT Tutorial 3 VLSI Design Methodology PowerPoint Presentation, free

Logic Gates Of Vlsi Design Optimizing the design’s area, power, and timing by fusing. Logical effort g for logic gates. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Boolean algebra, kmaps, gates and flip flops, finite state machine design. An understanding of basic digital design: How to design a chip: Objectives, metrics, design methodology, tools, and. Course outline, history and trends in vlsi design. Linear algebra and calculus at the level of a junior or senior in engineering. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Y = x iff a = 1 (iff=if. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Optimizing the design’s area, power, and timing by fusing. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance.

From www.studypool.com

SOLUTION 11 drpsk vlsi unit 2 physical design of logic gates Studypool Logic Gates Of Vlsi Design How to design a chip: Boolean algebra, kmaps, gates and flip flops, finite state machine design. Course outline, history and trends in vlsi design. Optimizing the design’s area, power, and timing by fusing. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. This comprehensive learning module delves into boolean algebra. Logic Gates Of Vlsi Design.

From www.youtube.com

AND GATE Logic in VLSI YouTube Logic Gates Of Vlsi Design How to design a chip: Linear algebra and calculus at the level of a junior or senior in engineering. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Course outline, history and trends in vlsi. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT VLSI Design Lecture 5 Logic Gates PowerPoint Presentation, free Logic Gates Of Vlsi Design How to design a chip: Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. An understanding of basic digital design: Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Y = x iff a = 1 (iff=if. Course outline, history and trends in vlsi design. Optimizing the design’s area, power, and timing by. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT VLSI Design Chapter 5 CMOS Circuit and Logic Design PowerPoint Logic Gates Of Vlsi Design How to design a chip: Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Objectives, metrics, design methodology,. Logic Gates Of Vlsi Design.

From www.vlsi-expert.com

VLSI Concepts January 2018 Logic Gates Of Vlsi Design Boolean algebra, kmaps, gates and flip flops, finite state machine design. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Course outline, history and trends in vlsi design. Logical effort g for logic gates. Linear algebra and calculus at the level of a junior. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT VLSI Design Chapter 5 CMOS Circuit and Logic Design PowerPoint Logic Gates Of Vlsi Design Boolean algebra, kmaps, gates and flip flops, finite state machine design. How to design a chip: 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Logical effort g for logic gates. An understanding of basic digital design: Y = x iff a = 1 (iff=if. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. This comprehensive learning module delves. Logic Gates Of Vlsi Design.

From gatedesignsnorit.blogspot.com

Gate Designs Gate Array Design Vlsi Logic Gates Of Vlsi Design Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Objectives, metrics, design methodology, tools, and. Optimizing the design’s area, power, and timing by fusing. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Y = x iff a = 1 (iff=if. An understanding of basic digital design:. Logic Gates Of Vlsi Design.

From design.udlvirtual.edu.pe

Example Of Reversible Logic Gates Design Talk Logic Gates Of Vlsi Design Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Y = x iff a = 1 (iff=if. Optimizing the design’s area, power, and timing by fusing. Objectives, metrics, design methodology, tools, and. Linear algebra and calculus at the level of a junior or senior in engineering. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design,. Logic Gates Of Vlsi Design.

From www.youtube.com

Reversible Logic Design What is Reversible logic Gates VLSI Design Logic Gates Of Vlsi Design Course outline, history and trends in vlsi design. Optimizing the design’s area, power, and timing by fusing. Y = x iff a = 1 (iff=if. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. How to design a chip: Objectives, metrics, design methodology, tools, and. Boolean algebra, kmaps, gates and flip flops, finite state machine design. An understanding. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT VLSI Design Chapter 5 CMOS Circuit and Logic Design PowerPoint Logic Gates Of Vlsi Design 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Course outline, history and trends in vlsi design. Linear algebra and calculus at the level of a junior or senior in engineering. An understanding of basic digital design: Y = x iff a = 1 (iff=if. Logical effort g for logic gates. Objectives, metrics, design methodology, tools, and. Boolean. Logic Gates Of Vlsi Design.

From www.researchgate.net

How to design 2 input XOR gate using dynamic CMOS logic in VLSI DESIGN? Logic Gates Of Vlsi Design Course outline, history and trends in vlsi design. Objectives, metrics, design methodology, tools, and. Boolean algebra, kmaps, gates and flip flops, finite state machine design. Linear algebra and calculus at the level of a junior or senior in engineering. Logical effort g for logic gates. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Inverter has smallest logical effort (g=1) and. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT VLSI Design Chapter 5 CMOS Circuit and Logic Design PowerPoint Logic Gates Of Vlsi Design Objectives, metrics, design methodology, tools, and. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Y = x iff a = 1 (iff=if. An understanding of basic digital design: This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Optimizing the design’s area, power, and timing by fusing.. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT VLSI Design Chapter 5 CMOS Circuit and Logic Design PowerPoint Logic Gates Of Vlsi Design Boolean algebra, kmaps, gates and flip flops, finite state machine design. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Course outline, history and trends in vlsi design. How to design a chip: Optimizing the design’s area, power, and timing by fusing. Objectives, metrics, design methodology, tools, and. An understanding of basic digital design: Y = x iff a = 1. Logic Gates Of Vlsi Design.

From scialert.net

CMOS VLSI Design of Low Power Comparator Logic Circuits Logic Gates Of Vlsi Design Y = x iff a = 1 (iff=if. How to design a chip: 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Linear algebra and calculus at the level of a junior or senior in engineering. Optimizing the design’s area, power, and timing by fusing. Boolean algebra, kmaps, gates and. Logic Gates Of Vlsi Design.

From sakthiece.github.io

VIRTUAL LAB ECE18R369 DIGITAL VLSI DESIGN Logic Gates Of Vlsi Design How to design a chip: 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. An understanding of basic digital design: Y = x iff a = 1 (iff=if. Linear algebra and calculus at the level of a junior or senior in engineering. Course outline, history and trends in vlsi design. Optimizing the design’s area, power, and timing by. Logic Gates Of Vlsi Design.

From present5.com

VLSI Design Chapter 5 CMOS Circuit and Logic Logic Gates Of Vlsi Design Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Logical effort g for logic gates. Optimizing the design’s area, power, and timing by fusing. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Course outline, history and trends in vlsi design. Objectives, metrics, design methodology, tools, and. Linear algebra and calculus at the. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT Tutorial 3 VLSI Design Methodology PowerPoint Presentation, free Logic Gates Of Vlsi Design Optimizing the design’s area, power, and timing by fusing. Logical effort g for logic gates. Linear algebra and calculus at the level of a junior or senior in engineering. Boolean algebra, kmaps, gates and flip flops, finite state machine design. Course outline, history and trends in vlsi design. How to design a chip: This comprehensive learning module delves into boolean. Logic Gates Of Vlsi Design.

From www.researchgate.net

Block diagram of the proposed VLSI architecture for the softoutput Logic Gates Of Vlsi Design Linear algebra and calculus at the level of a junior or senior in engineering. An understanding of basic digital design: How to design a chip: Optimizing the design’s area, power, and timing by fusing. Course outline, history and trends in vlsi design. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Boolean algebra, kmaps, gates and flip flops, finite state machine. Logic Gates Of Vlsi Design.

From www.studypool.com

SOLUTION 11 drpsk vlsi unit 2 physical design of logic gates Studypool Logic Gates Of Vlsi Design Boolean algebra, kmaps, gates and flip flops, finite state machine design. An understanding of basic digital design: Logical effort g for logic gates. Linear algebra and calculus at the level of a junior or senior in engineering. Course outline, history and trends in vlsi design. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design,. Logic Gates Of Vlsi Design.

From design.udlvirtual.edu.pe

Types Of Logic Gates With Explanation Design Talk Logic Gates Of Vlsi Design Logical effort g for logic gates. Boolean algebra, kmaps, gates and flip flops, finite state machine design. Optimizing the design’s area, power, and timing by fusing. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Y = x iff a = 1 (iff=if. An understanding of basic digital design: This comprehensive learning module delves into boolean algebra and. Logic Gates Of Vlsi Design.

From www.youtube.com

Logic Gates Implementation using Multiplexer ece vlsi Logic Gates Of Vlsi Design Y = x iff a = 1 (iff=if. Course outline, history and trends in vlsi design. Linear algebra and calculus at the level of a junior or senior in engineering. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. An understanding of basic digital design: Boolean. Logic Gates Of Vlsi Design.

From www.youtube.com

Switch logic Pass Transistor & Transmission Gate VLSI Lec53 Logic Gates Of Vlsi Design Logical effort g for logic gates. Linear algebra and calculus at the level of a junior or senior in engineering. Course outline, history and trends in vlsi design. Y = x iff a = 1 (iff=if. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Objectives,. Logic Gates Of Vlsi Design.

From www.youtube.com

VLSI Design PR7 CMOS 2 1 mux design using logic gates &TG YouTube Logic Gates Of Vlsi Design How to design a chip: Linear algebra and calculus at the level of a junior or senior in engineering. Course outline, history and trends in vlsi design. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Boolean algebra, kmaps, gates and flip flops, finite state machine. Logic Gates Of Vlsi Design.

From www.youtube.com

VLSI CMOS Logic 3 Make any logic gates using transistors YouTube Logic Gates Of Vlsi Design Course outline, history and trends in vlsi design. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. Logical effort g for logic gates. Optimizing the design’s area, power, and timing by fusing. Linear algebra and calculus at the level of a junior or senior in engineering.. Logic Gates Of Vlsi Design.

From www.electronics-tutorial.net

VLSI Logic Gates Of Vlsi Design 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. An understanding of basic digital design: Logical effort g for logic gates. Boolean algebra, kmaps, gates and flip flops, finite state machine design. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Optimizing the design’s area, power, and timing by fusing.. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT Basics of VLSI PowerPoint Presentation, free download ID7335645 Logic Gates Of Vlsi Design Boolean algebra, kmaps, gates and flip flops, finite state machine design. An understanding of basic digital design: 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Linear algebra and calculus at the level of a junior or senior in engineering. Optimizing the design’s area, power, and timing by fusing. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. This. Logic Gates Of Vlsi Design.

From www.youtube.com

CMOS 2input NAND and NOR gates Layout diagram VLSI Lec34 YouTube Logic Gates Of Vlsi Design Adapted from harris, rabaey, blaauw, zhang, sylvester, and. Optimizing the design’s area, power, and timing by fusing. Linear algebra and calculus at the level of a junior or senior in engineering. An understanding of basic digital design: Course outline, history and trends in vlsi design. This comprehensive learning module delves into boolean algebra and its applications in digital circuit design,. Logic Gates Of Vlsi Design.

From scialert.net

CMOS VLSI Design of Low Power Comparator Logic Circuits Logic Gates Of Vlsi Design This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental concepts like boolean variables, logic gates,. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Objectives, metrics, design methodology, tools, and. Optimizing the design’s. Logic Gates Of Vlsi Design.

From www.youtube.com

Full Adder Circuit Design Using Reversible Logic gates Reversible Logic Gates Of Vlsi Design Y = x iff a = 1 (iff=if. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Boolean algebra, kmaps, gates and flip flops, finite state machine design. Objectives, metrics, design methodology, tools, and. How to design a chip: Course outline, history and trends in vlsi design. An understanding of basic digital. Logic Gates Of Vlsi Design.

From www.youtube.com

⨘ } VLSI } 007 } Logic Gates using Multiplexers } LE PROF } YouTube Logic Gates Of Vlsi Design Course outline, history and trends in vlsi design. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Boolean algebra, kmaps, gates and flip flops, finite state machine design. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. How to design a chip: This comprehensive learning module delves into boolean algebra and its applications in digital circuit design, covering fundamental. Logic Gates Of Vlsi Design.

From www.chegg.com

Solved Chapter 1 Problem 12E Solution Cmos Vlsi Design 4th Edition Logic Gates Of Vlsi Design Y = x iff a = 1 (iff=if. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Objectives, metrics, design methodology, tools, and. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Boolean algebra, kmaps, gates and flip flops, finite state machine. Logic Gates Of Vlsi Design.

From www.studypool.com

SOLUTION 11 drpsk vlsi unit 2 physical design of logic gates Studypool Logic Gates Of Vlsi Design How to design a chip: Logical effort g for logic gates. Course outline, history and trends in vlsi design. Boolean algebra, kmaps, gates and flip flops, finite state machine design. Objectives, metrics, design methodology, tools, and. Optimizing the design’s area, power, and timing by fusing. Y = x iff a = 1 (iff=if. Adapted from harris, rabaey, blaauw, zhang, sylvester,. Logic Gates Of Vlsi Design.

From present5.com

VLSI Design Chapter 5 CMOS Circuit and Logic Logic Gates Of Vlsi Design Boolean algebra, kmaps, gates and flip flops, finite state machine design. Course outline, history and trends in vlsi design. Linear algebra and calculus at the level of a junior or senior in engineering. Inverter has smallest logical effort (g=1) and intrinsic delay (p=1) logical effort is ratio of input capacitance. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. This comprehensive. Logic Gates Of Vlsi Design.

From kerteriz.net

4 Bits Multiplier Design in Electric VLSI with VHDL Built Layout Logic Gates Of Vlsi Design Objectives, metrics, design methodology, tools, and. Y = x iff a = 1 (iff=if. Linear algebra and calculus at the level of a junior or senior in engineering. How to design a chip: Optimizing the design’s area, power, and timing by fusing. Adapted from harris, rabaey, blaauw, zhang, sylvester, and. This comprehensive learning module delves into boolean algebra and its. Logic Gates Of Vlsi Design.

From www.slideserve.com

PPT EE466 VLSI Design Lecture 9 Circuit Families PowerPoint Logic Gates Of Vlsi Design Linear algebra and calculus at the level of a junior or senior in engineering. 1t (1948) 6t (1960s) 1kt (1971) 1mt (1989) vlsi = very. Boolean algebra, kmaps, gates and flip flops, finite state machine design. Logical effort g for logic gates. How to design a chip: This comprehensive learning module delves into boolean algebra and its applications in digital. Logic Gates Of Vlsi Design.