Interface Systemverilog Example . Systemverilog interface is a convenient method of communication between 2 design blocks. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. In the design example shown below, we have substituted the portlist of counter_ud with an interface. In verilog, the communication between blocks is specified using module ports. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Systemverilog adds the interface construct which encapsulates the. This encapsulates signals and communicates with design, testbench components. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Interface encapsulates information about signals such ports, clocks,.

from www.slideserve.com

In the design example shown below, we have substituted the portlist of counter_ud with an interface. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. Systemverilog adds the interface construct which encapsulates the. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. This encapsulates signals and communicates with design, testbench components. Interface encapsulates information about signals such ports, clocks,. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In verilog, the communication between blocks is specified using module ports. Systemverilog interface is a convenient method of communication between 2 design blocks.

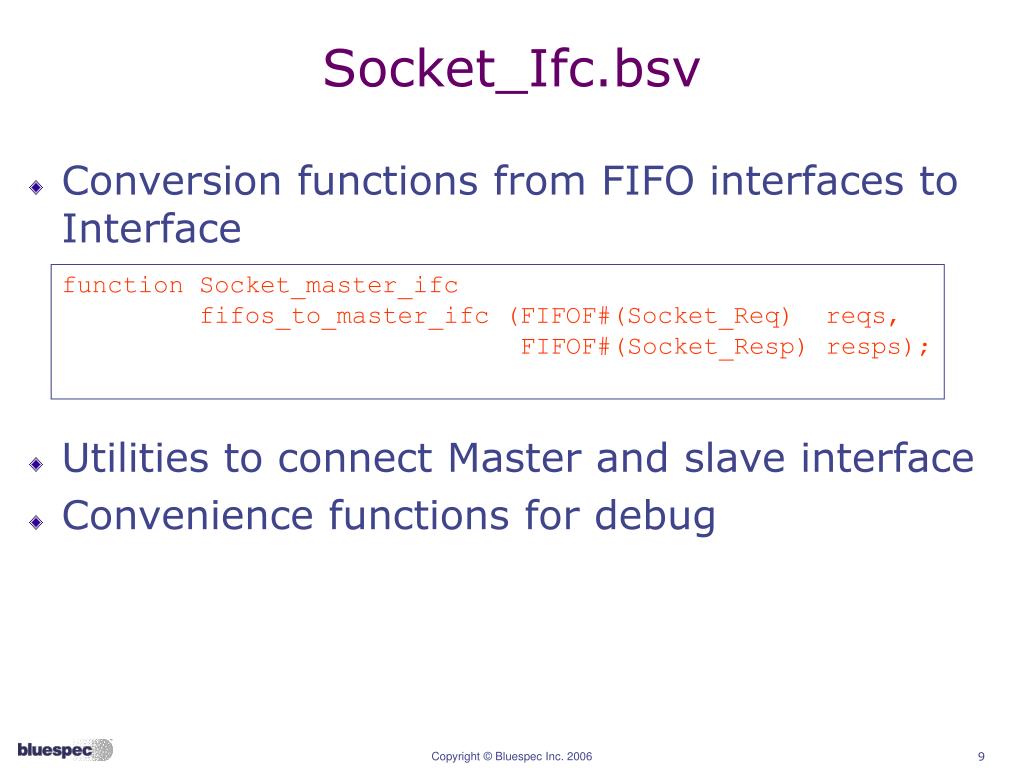

PPT Bluespec SystemVerilog™ Design Example A DMA Controller with a

Interface Systemverilog Example Systemverilog adds the interface construct which encapsulates the. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Systemverilog interface is a convenient method of communication between 2 design blocks. Systemverilog adds the interface construct which encapsulates the. In verilog, the communication between blocks is specified using module ports. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. This encapsulates signals and communicates with design, testbench components. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. Interface encapsulates information about signals such ports, clocks,. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design.

From dokumen.tips

(PDF) SystemVerilog Interface DOKUMEN.TIPS Interface Systemverilog Example In verilog, the communication between blocks is specified using module ports. Interface encapsulates information about signals such ports, clocks,. This encapsulates signals and communicates with design, testbench components. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Systemverilog adds the interface construct which encapsulates the. In the design example shown below, we have substituted the. Interface Systemverilog Example.

From www.edaphic.studio

SystemVerilog — Blog — Edaphic.Studio Interface Systemverilog Example In the design example shown below, we have substituted the portlist of counter_ud with an interface. Interface encapsulates information about signals such ports, clocks,. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. An interface in systemverilog is a group of signals used to model communication. Interface Systemverilog Example.

From www.slideserve.com

PPT Bluespec SystemVerilog™ Design Example A DMA Controller with a Interface Systemverilog Example Interface encapsulates information about signals such ports, clocks,. Systemverilog interface is a convenient method of communication between 2 design blocks. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. At. Interface Systemverilog Example.

From blog.csdn.net

SystemVerilog学习1——interface_verilog interfaceCSDN博客 Interface Systemverilog Example Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Systemverilog interface is a convenient method of. Interface Systemverilog Example.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 09 Function and Task YouTube Interface Systemverilog Example In verilog, the communication between blocks is specified using module ports. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Systemverilog adds the interface construct which encapsulates the. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. Interface encapsulates. Interface Systemverilog Example.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 14 interface YouTube Interface Systemverilog Example An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. This encapsulates signals and communicates with design, testbench components. Systemverilog interface is. Interface Systemverilog Example.

From www.slideserve.com

PPT SystemVerilog Fall 2004 PowerPoint Presentation, free download Interface Systemverilog Example Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. This encapsulates signals and communicates with design, testbench components. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. Unlike verilog that. Interface Systemverilog Example.

From www.slideserve.com

PPT Bluespec SystemVerilog™ Design Example A DMA Controller with a Interface Systemverilog Example Interface encapsulates information about signals such ports, clocks,. Systemverilog interface is a convenient method of communication between 2 design blocks. Systemverilog adds the interface construct which encapsulates the. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. This encapsulates signals and communicates with design, testbench components. In verilog, the communication between blocks is specified. Interface Systemverilog Example.

From github-wiki-see.page

13.Interface vineethkumarv/SystemVerilog_Course GitHub Wiki Interface Systemverilog Example Systemverilog interface is a convenient method of communication between 2 design blocks. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Systemverilog adds the interface construct. Interface Systemverilog Example.

From www.maven-silicon.com

SystemVerilog Testbench/Verification Environment Architecture Maven Interface Systemverilog Example At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. This encapsulates signals and communicates with design, testbench components. Systemverilog interface is a convenient method of communication between 2 design blocks. Systemverilog allows a module to accept an interface as the. Interface Systemverilog Example.

From www.youtube.com

Course Systemverilog Verification 2 L5.1 Basics of Systemverilog Interface Systemverilog Example Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. Interface encapsulates information about signals such ports, clocks,. Systemverilog interface is a convenient method of communication between 2 design blocks. An interface in systemverilog is a group of signals used to model communication between components, particularly in. Interface Systemverilog Example.

From www.youtube.com

Implementing AXI in Verilog Part 1 Slave Interface YouTube Interface Systemverilog Example Systemverilog interface is a convenient method of communication between 2 design blocks. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. In the design example shown below, we have substituted the portlist of counter_ud with an. Interface Systemverilog Example.

From www.youtube.com

Interface in System Verilog part 4 YouTube Interface Systemverilog Example In the design example shown below, we have substituted the portlist of counter_ud with an interface. This encapsulates signals and communicates with design, testbench components. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Interface encapsulates information about signals such ports, clocks,. Unlike verilog that has module ports for communication,. Interface Systemverilog Example.

From www.aldec.com

functional coverage in uvm Interface Systemverilog Example This encapsulates signals and communicates with design, testbench components. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Systemverilog interface is a convenient method of communication between 2 design blocks. Unlike verilog that has module ports for communication,. Interface Systemverilog Example.

From www.youtube.com

Functions and Tasks in SystemVerilog with conceptual examples YouTube Interface Systemverilog Example Systemverilog allows a module to accept an interface as the portlist instead of individual signals. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Systemverilog adds the interface construct which encapsulates the. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Interface encapsulates. Interface Systemverilog Example.

From tanakatarou.tech

SystemVerilog Interfaceを使用して回路を作成する modport タナビボ田中太郎の備忘録 Interface Systemverilog Example Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Systemverilog interface is a convenient method of communication between 2 design blocks. Systemverilog adds the interface construct which encapsulates the. Interface encapsulates information about signals such ports,. Interface Systemverilog Example.

From www.chipsalliance.org

Open Source SystemVerilog Tools in ASIC Design Chips Alliance Interface Systemverilog Example Systemverilog interface is a convenient method of communication between 2 design blocks. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser.. Interface Systemverilog Example.

From www.tina.com

SystemVerilog Simulation Interface Systemverilog Example An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Interface encapsulates information about signals such ports, clocks,. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. Unlike verilog that has. Interface Systemverilog Example.

From verificationguide.com

Systemverilog Dynamic Array Verification Guide Interface Systemverilog Example Systemverilog adds the interface construct which encapsulates the. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is.. Interface Systemverilog Example.

From www.microcontrollertips.com

How to structure SystemVerilog for reuse as Portable Stimulus Interface Systemverilog Example Systemverilog adds the interface construct which encapsulates the. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Systemverilog interface is. Interface Systemverilog Example.

From slidetodoc.com

An Introduction to System Verilog This Presentation will Interface Systemverilog Example At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. In verilog, the communication between blocks is specified using module ports. This encapsulates signals and communicates with design, testbench components. In the design example shown below, we have substituted the portlist. Interface Systemverilog Example.

From verificationacademy.com

Bind Statement with SystemVerilog Interface (Assertions) Verification Interface Systemverilog Example Systemverilog allows a module to accept an interface as the portlist instead of individual signals. This encapsulates signals and communicates with design, testbench components. Systemverilog interface is a convenient method of communication between 2 design blocks. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module. Interface Systemverilog Example.

From www.youtube.com

[SystemVerilog] Verification 07 Interfaces and the use of Virtual Interface Systemverilog Example Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Systemverilog. Interface Systemverilog Example.

From programmer.ink

[SystemVerilog basics] Interface Quick Start Guide Interface Systemverilog Example Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. This encapsulates signals and communicates with design, testbench components. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Interface encapsulates information about signals such ports, clocks,. Systemverilog. Interface Systemverilog Example.

From www.youtube.com

SystemVerilog DPI (Direct Programming Interface) YouTube Interface Systemverilog Example Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. This encapsulates signals and communicates with design, testbench components. In the design example shown below, we have substituted the portlist of counter_ud with an interface. In verilog, the communication between blocks is specified using module ports. Systemverilog. Interface Systemverilog Example.

From blog.csdn.net

SystemVerilog学习1——interface_verilog interfaceCSDN博客 Interface Systemverilog Example In verilog, the communication between blocks is specified using module ports. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. Interface encapsulates information about signals such ports, clocks,. Systemverilog interface is a convenient method of communication between 2 design blocks. At its simplest, an interface is. Interface Systemverilog Example.

From www.slideserve.com

PPT Bluespec SystemVerilog™ Design Example A DMA Controller with a Interface Systemverilog Example In verilog, the communication between blocks is specified using module ports. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Systemverilog interface is a convenient method of communication between 2 design blocks. Systemverilog adds the interface construct which encapsulates the. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web. Interface Systemverilog Example.

From www.tina.com

SystemVerilog Simulation Interface Systemverilog Example At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. This encapsulates signals and communicates with design, testbench components. Interface encapsulates information about signals such ports, clocks,. Systemverilog allows a module to accept an interface as the portlist instead of individual. Interface Systemverilog Example.

From programmer.ink

[SystemVerilog basics] Interface Quick Start Guide Interface Systemverilog Example Systemverilog adds the interface construct which encapsulates the. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. Unlike verilog that has module ports for communication,. Interface Systemverilog Example.

From www.youtube.com

4. Arbiter example with Simple Interfaces & Interfaces with Modports in Interface Systemverilog Example Systemverilog interface is a convenient method of communication between 2 design blocks. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Systemverilog adds the interface construct which encapsulates the. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while. Interface Systemverilog Example.

From studylib.net

SystemVerilog Interfaces Interface Systemverilog Example This encapsulates signals and communicates with design, testbench components. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is allowed as a module port, while a struct is. An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Systemverilog adds the. Interface Systemverilog Example.

From www.youtube.com

Course Systemverilog Verification 2 L4.1 Clocking Blocks in Interface Systemverilog Example Interface encapsulates information about signals such ports, clocks,. Systemverilog allows a module to accept an interface as the portlist instead of individual signals. Systemverilog adds the interface construct which encapsulates the. In verilog, the communication between blocks is specified using module ports. This encapsulates signals and communicates with design, testbench components. At its simplest, an interface is a named bundle. Interface Systemverilog Example.

From www.scribd.com

SystemVerilog Interface Interface Areas Of Computer Science Interface Systemverilog Example Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. Interface encapsulates information about signals such ports, clocks,. This encapsulates signals and communicates with design, testbench components. At its simplest, an interface is a named bundle of wires, similar to a struct, except that an interface is. Interface Systemverilog Example.

From www.youtube.com

Course Systemverilog Verification 2 L5.2 Interfaces and Modports Interface Systemverilog Example An interface in systemverilog is a group of signals used to model communication between components, particularly in testbench design. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a bundle of sets of signals. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Systemverilog adds. Interface Systemverilog Example.

From blog.csdn.net

SystemVerilog——Interface简单介绍_system verilog interfaceCSDN博客 Interface Systemverilog Example Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Systemverilog interface is a convenient method of communication between 2 design blocks. In the design example shown below, we have substituted the portlist of counter_ud with an interface. Unlike verilog that has module ports for communication, system verilog provides an interface construct that simply contains a. Interface Systemverilog Example.