Clock Gating Example In Verilog . What is the proper way to implement clock gating in rtl? I've an example wave here: Clock gating is way to save power in synchronous logic by temporarily. I'm trying to understand how clock gating works in rtl design. To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. As the name implies, clock gating should use a gate, an and gate. The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. Xor based clock gating & implementation: Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure).

from mavink.com

Xor based clock gating & implementation: I'm trying to understand how clock gating works in rtl design. The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: I've an example wave here: What is the proper way to implement clock gating in rtl? As the name implies, clock gating should use a gate, an and gate.

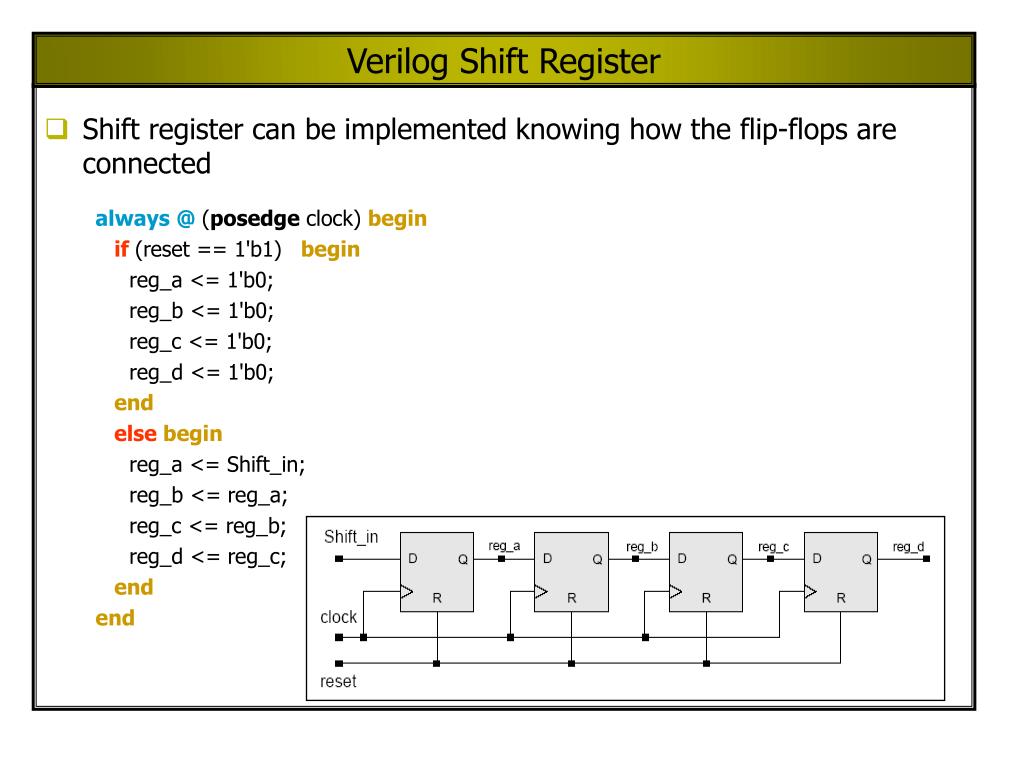

Shift Register Verilog

Clock Gating Example In Verilog I've an example wave here: I'm trying to understand how clock gating works in rtl design. As the name implies, clock gating should use a gate, an and gate. The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. Xor based clock gating & implementation: Clock gating is way to save power in synchronous logic by temporarily. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: I've an example wave here: You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). What is the proper way to implement clock gating in rtl?

From studylib.net

Verilog Example Clock Gating Example In Verilog The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. What is the proper. Clock Gating Example In Verilog.

From www.youtube.com

xilinx clock gating circuitLow power design technique YouTube Clock Gating Example In Verilog As the name implies, clock gating should use a gate, an and gate. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). What is the proper way to implement. Clock Gating Example In Verilog.

From github.com

GitHub Emilylulu/MemorytransferimplementationbyVerilog Clock Gating Example In Verilog The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow:. Clock Gating Example In Verilog.

From www.researchgate.net

Figure A5. VerilogA code of the clock amplitudebased control Clock Gating Example In Verilog The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). Clock gating is way to save power in synchronous logic by temporarily. The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. I've an example wave. Clock Gating Example In Verilog.

From www.semanticscholar.org

Figure 7 from A Review on Clock Gating Methodologies for power Clock Gating Example In Verilog Xor based clock gating & implementation: I've an example wave here: Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: What is the proper way to implement clock gating in rtl? The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. You need. Clock Gating Example In Verilog.

From www.youtube.com

Clock divider by 3 with duty cycle 50 using Verilog YouTube Clock Gating Example In Verilog I'm trying to understand how clock gating works in rtl design. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Clock gating is way to save power in synchronous logic by temporarily. Xor based clock gating & implementation: What is the proper way to implement clock gating in rtl? To prevent the wastage. Clock Gating Example In Verilog.

From mavink.com

Shift Register Verilog Clock Gating Example In Verilog Clock gating is way to save power in synchronous logic by temporarily. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. As the name implies, clock gating should use a gate, an and gate. The clock gating signal should only toggle when the latch is closed, otherwise there is a chance. Clock Gating Example In Verilog.

From ileonsun.github.io

Leon Sun Clock Gating Check Clock Gating Example In Verilog You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. I've an example wave here: To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. The clock gating signal should. Clock Gating Example In Verilog.

From www.teamvlsi.com

Team VLSI Clock Gating Example In Verilog You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. What is the proper way to implement clock gating in rtl? As the name implies, clock gating should use a gate, an and gate. The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for. Clock Gating Example In Verilog.

From www.youtube.com

Verilog Code of D latch YouTube Clock Gating Example In Verilog The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. Xor based clock gating & implementation: To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. As the. Clock Gating Example In Verilog.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Clock Gating Example In Verilog Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the. Clock Gating Example In Verilog.

From www.youtube.com

How to generate clock in Verilog HDL YouTube Clock Gating Example In Verilog Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals. Clock Gating Example In Verilog.

From slideplayer.com

Verilog Synthesis Synthesis vs. Compilation ppt download Clock Gating Example In Verilog You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. What is the proper way to implement clock gating in rtl? The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). I've an example wave here: The clock. Clock Gating Example In Verilog.

From community.cadence.com

How to resolve clock gating hold checks could not be fixed Clock Gating Example In Verilog To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). What is the proper. Clock Gating Example In Verilog.

From www.researchgate.net

Waveforms showing edge combinations due to DET clock gating and example Clock Gating Example In Verilog The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). I've an example wave here: Xor based clock gating & implementation: As the name implies, clock gating should use a gate, an and gate. I'm trying to understand how clock gating works in rtl design. Enabling. Clock Gating Example In Verilog.

From www.myshared.ru

Презентация на тему "Verilog RTL Coding Guideline Ando KI June Clock Gating Example In Verilog To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. Xor based clock gating & implementation: What is the proper way to implement clock gating in rtl? As the name implies, clock gating should use a gate, an. Clock Gating Example In Verilog.

From electronics.stackexchange.com

fpga FSM implementation using single always block in Verilog Clock Gating Example In Verilog Clock gating is way to save power in synchronous logic by temporarily. Xor based clock gating & implementation: To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. The clock gating signal should only toggle when the latch. Clock Gating Example In Verilog.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Example In Verilog Clock gating is way to save power in synchronous logic by temporarily. I'm trying to understand how clock gating works in rtl design. I've an example wave here: To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation.. Clock Gating Example In Verilog.

From semiwiki.com

The Role of Clock Gating SemiWiki Clock Gating Example In Verilog The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. As the name implies, clock gating should use a gate, an and gate. I've an example wave here: To prevent the wastage. Clock Gating Example In Verilog.

From blog.csdn.net

verilog GATED_CLOCK_gated clock rtlCSDN博客 Clock Gating Example In Verilog Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. As the name implies, clock gating should use a gate, an and. Clock Gating Example In Verilog.

From www.cnblogs.com

clock gating check いつまでも 博客园 Clock Gating Example In Verilog I'm trying to understand how clock gating works in rtl design. Xor based clock gating & implementation: The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above. Clock Gating Example In Verilog.

From zhuanlan.zhihu.com

低功耗设计基础:Clock Gating 知乎 Clock Gating Example In Verilog I've an example wave here: Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: I'm trying to understand how clock gating works in rtl design. The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. To prevent the wastage of clock cycles as. Clock Gating Example In Verilog.

From www.slideserve.com

PPT Verilog For Computer Design PowerPoint Presentation, free Clock Gating Example In Verilog Xor based clock gating & implementation: The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). I'm trying to understand how clock gating works in rtl. Clock Gating Example In Verilog.

From community.cadence.com

How to resolve clock gating hold checks could not be fixed Clock Gating Example In Verilog What is the proper way to implement clock gating in rtl? Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. You need to have the gating signal toggle on the inactive edge of. Clock Gating Example In Verilog.

From blog.csdn.net

clock gateCSDN博客 Clock Gating Example In Verilog Clock gating is way to save power in synchronous logic by temporarily. To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to. Clock Gating Example In Verilog.

From www.solutionspile.com

[Solved] USING VERILOG AND FOLLOWING THE SPECIFIC INSTRUCTI Clock Gating Example In Verilog The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: What is the proper way to implement clock gating in rtl? I'm trying to understand how clock gating works in. Clock Gating Example In Verilog.

From www.slideserve.com

PPT PROCESSOR POWER SAVING CLOCK GATING PowerPoint Presentation Clock Gating Example In Verilog You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. I'm trying to understand how clock gating works in rtl design. I've an example wave here: As the name implies, clock gating should use a gate, an and gate. The clock gating signal should only toggle when the latch is closed, otherwise. Clock Gating Example In Verilog.

From www.hotzxgirl.com

How To Implement A Verilog Testbench Clock Generator For Sequential Clock Gating Example In Verilog Xor based clock gating & implementation: What is the proper way to implement clock gating in rtl? Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). You need to. Clock Gating Example In Verilog.

From www.numerade.com

SOLVED The SR latch can be built using NAND gates or NOR gates. This Clock Gating Example In Verilog I've an example wave here: You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. What is the proper way to implement clock gating in rtl? As the name implies, clock gating should use a gate, an and gate. Clock gating is way to save power in synchronous logic by temporarily. Enabling. Clock Gating Example In Verilog.

From www.slideserve.com

PPT Verilog II CPSC 321 PowerPoint Presentation, free download ID Clock Gating Example In Verilog The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. I'm trying to understand how clock gating works in rtl design. What is the proper way to implement clock gating in rtl? I've an example wave here: To prevent the wastage of clock cycles as long as enable is 0. Clock Gating Example In Verilog.

From www.slideserve.com

PPT Lecture 7 Power PowerPoint Presentation, free download ID5730587 Clock Gating Example In Verilog To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals when enable is 0 and reduces power dissipation. I'm trying to understand how clock gating works in rtl design. As the name implies, clock gating should use a gate, an and gate. Enabling rtl clock gating. Clock Gating Example In Verilog.

From www.researchgate.net

(a) Verilog module which implements a NAND3 based Clock Gating Example In Verilog What is the proper way to implement clock gating in rtl? I'm trying to understand how clock gating works in rtl design. As the name implies, clock gating should use a gate, an and gate. I've an example wave here: Clock gating is way to save power in synchronous logic by temporarily. The clock gating signal should only toggle when. Clock Gating Example In Verilog.

From www.youtube.com

25 Verilog Clock Divider YouTube Clock Gating Example In Verilog You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. As the name implies, clock gating should use a gate, an and gate. I've an example wave here: To prevent the wastage of clock cycles as long as enable is 0 clock gating is implemented that stops the switching of clock signals. Clock Gating Example In Verilog.

From www.slideshare.net

Clock gating Clock Gating Example In Verilog You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: What is the proper way to implement clock gating in rtl? The clock gating signal should only toggle when the latch is closed, otherwise there is. Clock Gating Example In Verilog.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Gating Example In Verilog The clock enable signal, generated by a combinatorial logic, controls when to provide the clock to the downstream logic (ff in the above figure). The clock gating signal should only toggle when the latch is closed, otherwise there is a chance for glitches and. To prevent the wastage of clock cycles as long as enable is 0 clock gating is. Clock Gating Example In Verilog.