Clock Multiplier Fpga . The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. It is dependent to a secondary order on temperature, i/o pin. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. For a pll clock multiplier, where does the new clock come from? The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum.

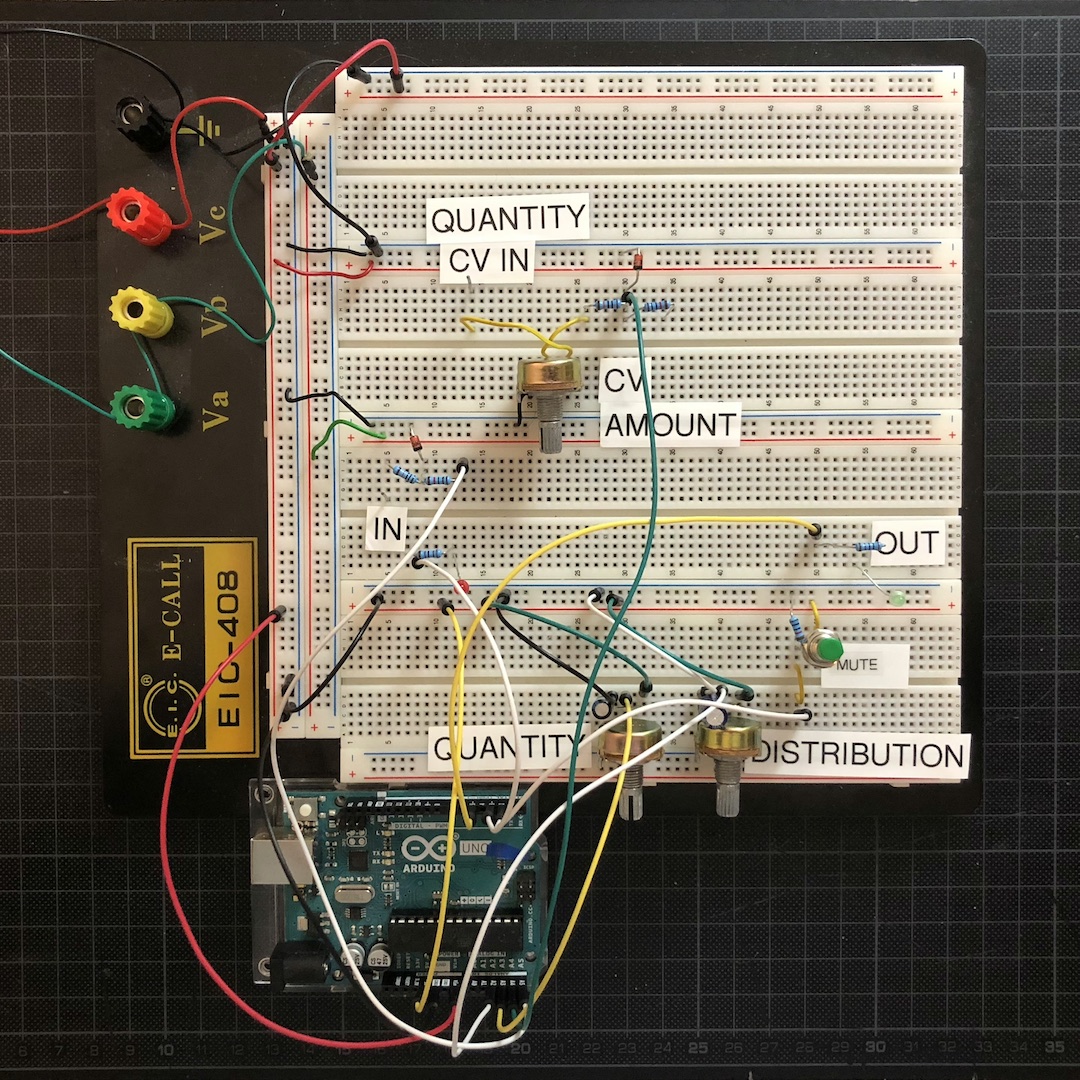

from www.bummbummgarage.com

It is dependent to a secondary order on temperature, i/o pin. For a pll clock multiplier, where does the new clock come from? A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. It produces a fifty percent duty cycle of square waves that are half on off time and half on time.

Clock Multiplier Bumm Bumm Garage

Clock Multiplier Fpga For a pll clock multiplier, where does the new clock come from? A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. For a pll clock multiplier, where does the new clock come from? It produces a fifty percent duty cycle of square waves that are half on off time and half on time. It is dependent to a secondary order on temperature, i/o pin. The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels.

From www.semanticscholar.org

Figure 2 from PLLless clock multiplier with selfadjusting phase symmetry Semantic Scholar Clock Multiplier Fpga The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. For a pll clock multiplier, where does the new clock come from? It produces a fifty percent duty cycle of square waves that are half on off time and half on time. It is dependent to a secondary order on temperature, i/o pin.. Clock Multiplier Fpga.

From www.mdpi.com

Electronics Free FullText A Fast LockIn Time, Capacitive FIRFilterBased Clock Multiplier Clock Multiplier Fpga The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. For a pll clock multiplier, where does the new clock come from? It produces a fifty percent duty cycle of square waves that are half on off time and half on time. A clock in an fpga system is responsible for driving the. Clock Multiplier Fpga.

From www.allaboutcircuits.com

Clock Signal Management Clock Resources of FPGAs Technical Articles Clock Multiplier Fpga A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. For a pll clock multiplier, where does the. Clock Multiplier Fpga.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. The 1.5 multiplier is just a starting point guess and is fully. Clock Multiplier Fpga.

From www.mdpi.com

Electronics Free FullText Fast FPGABased Multipliers by Constant for Digital Signal Clock Multiplier Fpga It produces a fifty percent duty cycle of square waves that are half on off time and half on time. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The 1.5 multiplier is just a starting point. Clock Multiplier Fpga.

From allaboutfpga.com

FPGA Architecture Clock Multiplier Fpga The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. For a pll clock multiplier, where does the new clock come from? A clock in an fpga system is responsible for driving the. Clock Multiplier Fpga.

From www.mdpi.com

Computers Free FullText Array Multipliers for High Throughput in Xilinx FPGAs with 6Input LUTs Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. The 1.5 multiplier is just a starting point guess and is fully. Clock Multiplier Fpga.

From www.bummbummgarage.com

Clock Multiplier Bumm Bumm Garage Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. For a pll clock multiplier, where does the new clock come. Clock Multiplier Fpga.

From www.researchgate.net

FPGA slices and clock cycle requirements of bitserial and bitparallel... Download Scientific Clock Multiplier Fpga A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. The multiplier logicore™ simplifies this challenge by abstracting. Clock Multiplier Fpga.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Multiplier Fpga It produces a fifty percent duty cycle of square waves that are half on off time and half on time. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The multiplier logicore™ simplifies this challenge by abstracting. Clock Multiplier Fpga.

From www.edn.com

µCbased circuit performs frequency multiplication EDN Clock Multiplier Fpga A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It produces a fifty percent duty cycle of square waves that. Clock Multiplier Fpga.

From www.nxfee.com

An Optimization in Conventional Shift &Add Multiplier for AreaEfficient Implementation on FPGA Clock Multiplier Fpga It produces a fifty percent duty cycle of square waves that are half on off time and half on time. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. For a pll clock multiplier, where does the. Clock Multiplier Fpga.

From www.mdpi.com

Computers Free FullText Array Multipliers for High Throughput in Xilinx FPGAs with 6Input LUTs Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of. Clock Multiplier Fpga.

From www.semanticscholar.org

Figure 11 from A 6.758.25GHz −250dB FoM Rapid ON/OFF FractionalN InjectionLocked Clock Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. The 1.5 multiplier is just a starting point guess and is fully. Clock Multiplier Fpga.

From www.researchgate.net

(PDF) Efficient Implementation of Complex Multipliers on FPGAs Using DSP Slices Clock Multiplier Fpga For a pll clock multiplier, where does the new clock come from? The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. It is dependent to a secondary order on temperature, i/o pin. It produces a fifty percent duty cycle of square waves that are half on off time. Clock Multiplier Fpga.

From www.slideshare.net

VLSI Implementation of High Speed & Low Power Multiplier in FPGA Clock Multiplier Fpga For a pll clock multiplier, where does the new clock come from? The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of. Clock Multiplier Fpga.

From www.reddit.com

What is the purpose of a Clock Enable on a Multiplier? r/FPGA Clock Multiplier Fpga A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. For a pll clock multiplier, where does the new clock come. Clock Multiplier Fpga.

From www.youtube.com

High Performance Accurate and Approximate Multipliers for FPGA based Hardware Accelerators YouTube Clock Multiplier Fpga The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. For a pll clock multiplier, where does the new clock come. Clock Multiplier Fpga.

From www.mdpi.com

Electronics Free FullText A Fast LockIn Time, Capacitive FIRFilterBased Clock Multiplier Clock Multiplier Fpga The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can. Clock Multiplier Fpga.

From www.mdpi.com

Electronics Free FullText A Fast LockIn Time, Capacitive FIRFilterBased Clock Multiplier Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. For a pll clock multiplier, where does the new clock come from? The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required. Clock Multiplier Fpga.

From www.electronics-lab.com

frequency multiplier Archives Clock Multiplier Fpga For a pll clock multiplier, where does the new clock come from? The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. It is dependent to a secondary order on temperature, i/o pin.. Clock Multiplier Fpga.

From fpga.eetrend.com

锁相环(PLL)基本原理 FPGA 开发圈 Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz.. Clock Multiplier Fpga.

From vhdlwhiz.com

VHDL and FPGA terminology Multiplier (DSP) Clock Multiplier Fpga The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. It produces a fifty percent duty cycle of square waves that. Clock Multiplier Fpga.

From www.mdpi.com

Electronics Free FullText A Fast LockIn Time, Capacitive FIRFilterBased Clock Multiplier Clock Multiplier Fpga The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The 1.5 multiplier is just a starting point guess and is. Clock Multiplier Fpga.

From www.slideserve.com

PPT ECE 448 Lecture 1 6 PowerPoint Presentation, free download ID2911672 Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum. Clock Multiplier Fpga.

From www.semanticscholar.org

Table I from FPGA implementation of vedic floating point multiplier Semantic Scholar Clock Multiplier Fpga A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It is dependent to a secondary order on temperature, i/o pin.. Clock Multiplier Fpga.

From www.mdpi.com

Electronics Free FullText Fast FPGABased Multipliers by Constant for Digital Signal Clock Multiplier Fpga For a pll clock multiplier, where does the new clock come from? A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. It produces a fifty percent duty cycle of square waves that are half on off time. Clock Multiplier Fpga.

From people.ece.cornell.edu

FPGA intro Clock Multiplier Fpga It produces a fifty percent duty cycle of square waves that are half on off time and half on time. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It is dependent to a secondary order on temperature, i/o pin. The 1.5 multiplier is just a starting point guess and is fully. Clock Multiplier Fpga.

From www.wevolver.com

FPGA Design A Comprehensive Guide to Mastering FieldProgrammable Gate Arrays Clock Multiplier Fpga The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. It is dependent to a secondary order on temperature, i/o pin. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum. Clock Multiplier Fpga.

From www.instructables.com

DIGITAL CLOCK FPGA 9 Steps Instructables Clock Multiplier Fpga It produces a fifty percent duty cycle of square waves that are half on off time and half on time. For a pll clock multiplier, where does the new clock come from? The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. A clock in an fpga system is. Clock Multiplier Fpga.

From www.youtube.com

Digital Alarm Clock on Altera DE2 FPGA in VHDL YouTube Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It produces a fifty percent duty cycle of square waves that are half on off time and half on time. The 1.5 multiplier is just a starting point guess and is fully. Clock Multiplier Fpga.

From www.mdpi.com

Computers Free FullText Array Multipliers for High Throughput in Xilinx FPGAs with 6Input LUTs Clock Multiplier Fpga The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. For a pll clock multiplier, where does. Clock Multiplier Fpga.

From www.mdpi.com

Electronics Free FullText Fast FPGABased Multipliers by Constant for Digital Signal Clock Multiplier Fpga A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The 1.5 multiplier is just a starting point guess and is fully dependent on the fpga's input logic level threshold levels. It produces a fifty percent duty cycle. Clock Multiplier Fpga.

From www.semanticscholar.org

Figure 1 from AllDigital Baseband 65 nm PLL / FPLL Clock Multiplier using 10cell Library Clock Multiplier Fpga It is dependent to a secondary order on temperature, i/o pin. For a pll clock multiplier, where does the new clock come from? A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The multiplier logicore™ simplifies this. Clock Multiplier Fpga.

From www.researchgate.net

Neural Processing Units (NPUs) grid on FPGA [88]. Download Scientific Diagram Clock Multiplier Fpga A clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process data, with numbers reaching a maximum of upwards of 1ghz. The multiplier logicore™ simplifies this challenge by abstracting away fpga device specifics, while maintaining the required maximum. It produces a fifty percent duty cycle of square waves that. Clock Multiplier Fpga.